用户手册

AG32 MCU

参考手册

1.2

1 设备概述¶

1.1 简介¶

AG32系列32位微控制器旨在为MCU用户提供更高的灵活性和丰富的兼容外设,同时保持引脚和功能的兼容性。AG32产品系列具有优异的质量、稳定性和极具竞争力的性价比。

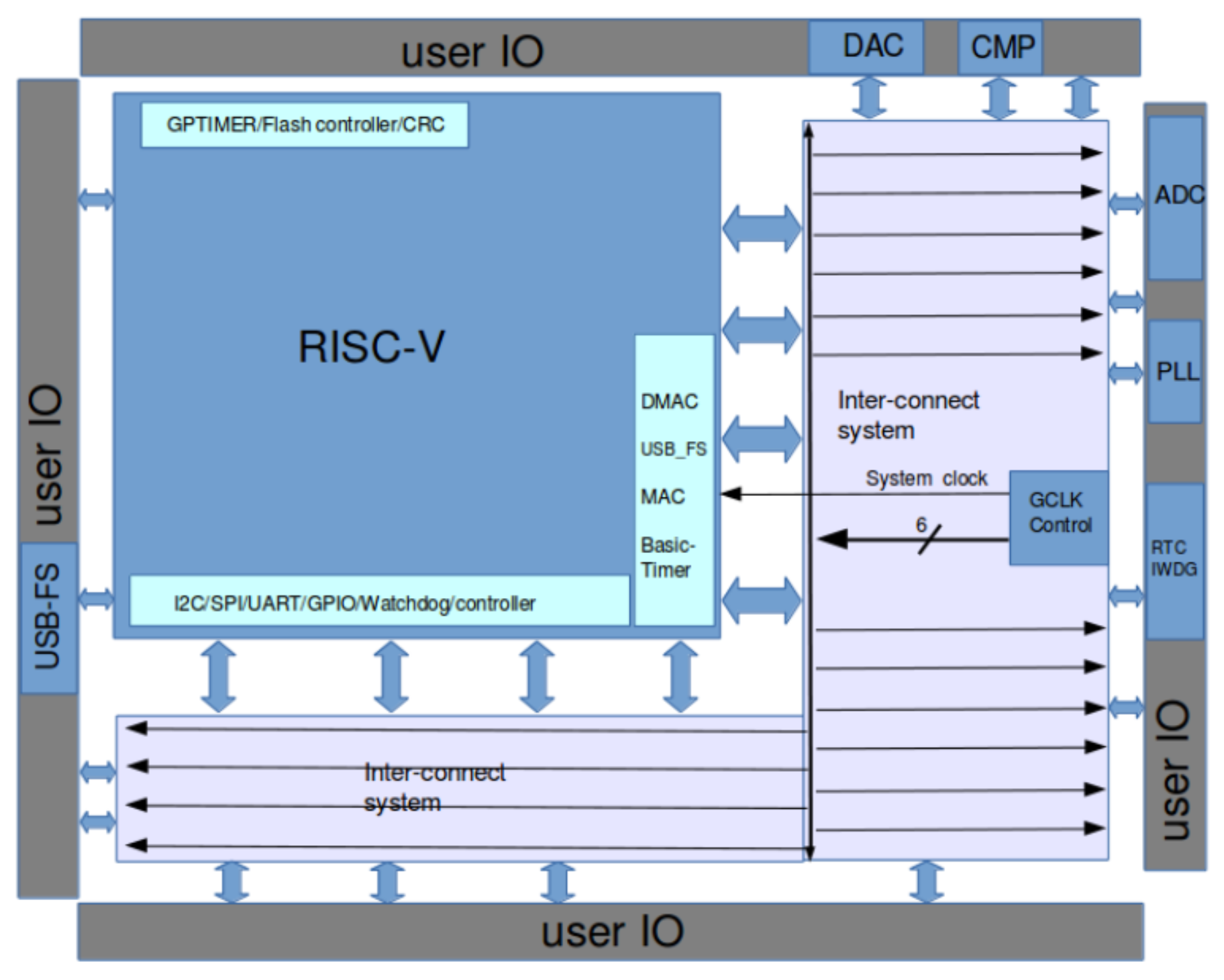

1.1.1 系统概览¶

- 基于RISC-V内核,支持RV32IMAFC指令集

- 最多1MB闪存

- 128KB SRAM

- 16KB指令缓存

1.1.2 时钟、复位与电源管理¶

- 工作电压范围:3.135V ~ 3.465V,适用于主芯片和I/O

- POR(上电复位)、PDR(电压监测复位)

- 支持4~26 MHz的晶体振荡器

- 内部20MHz振荡器

- RTC使用的32kHz振荡器

- 内部40kHz振荡器

1.1.3 低功耗运行模式¶

- 支持Sleep、Stop和Standby模式

- RTC可由VBAT独立供电

1.1.4 模数转换器(ADC)/数模转换器(DAC)/比较器(CMP)/直接存储器访问(DMA)/定时器/通用输入输出(GPIO)¶

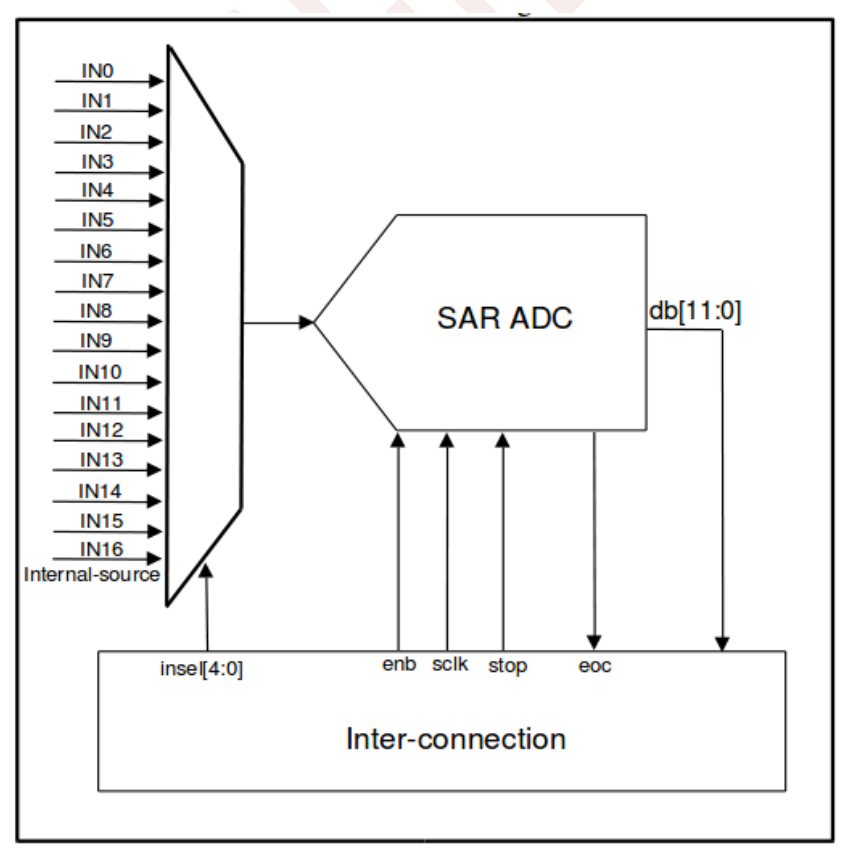

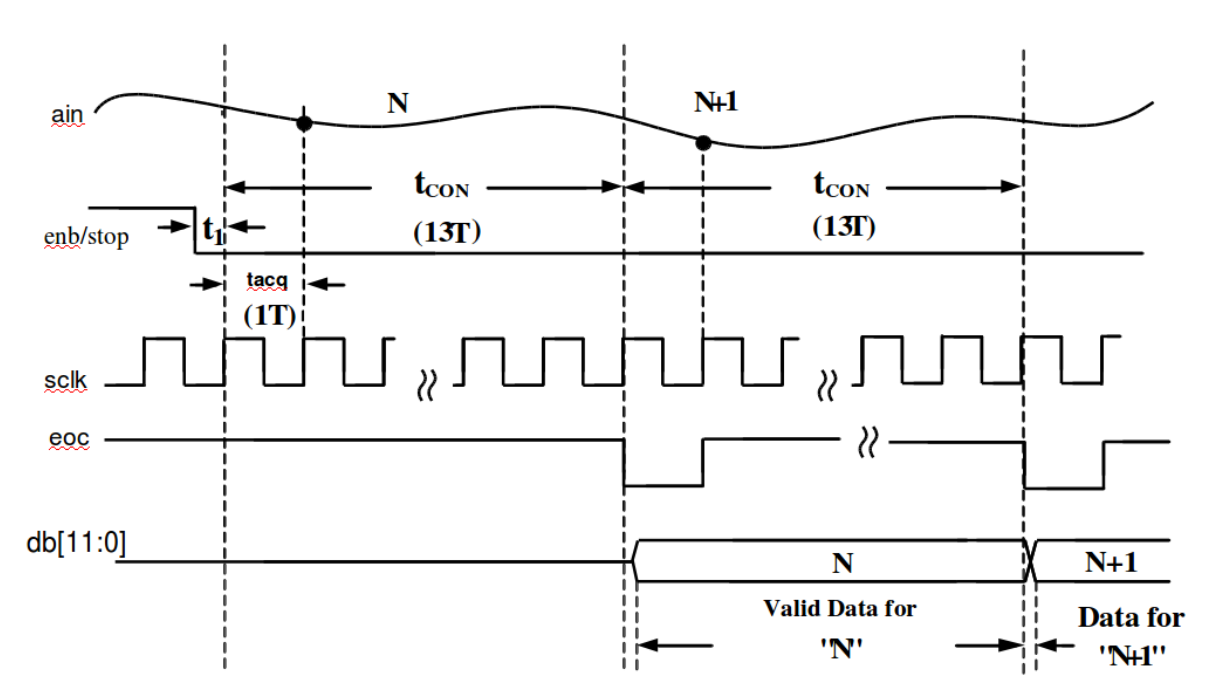

- 3个12位、1.0 MSPS的ADC(模数转换器):最多支持16通道,三路交错模式下总采样率达3 MSPS

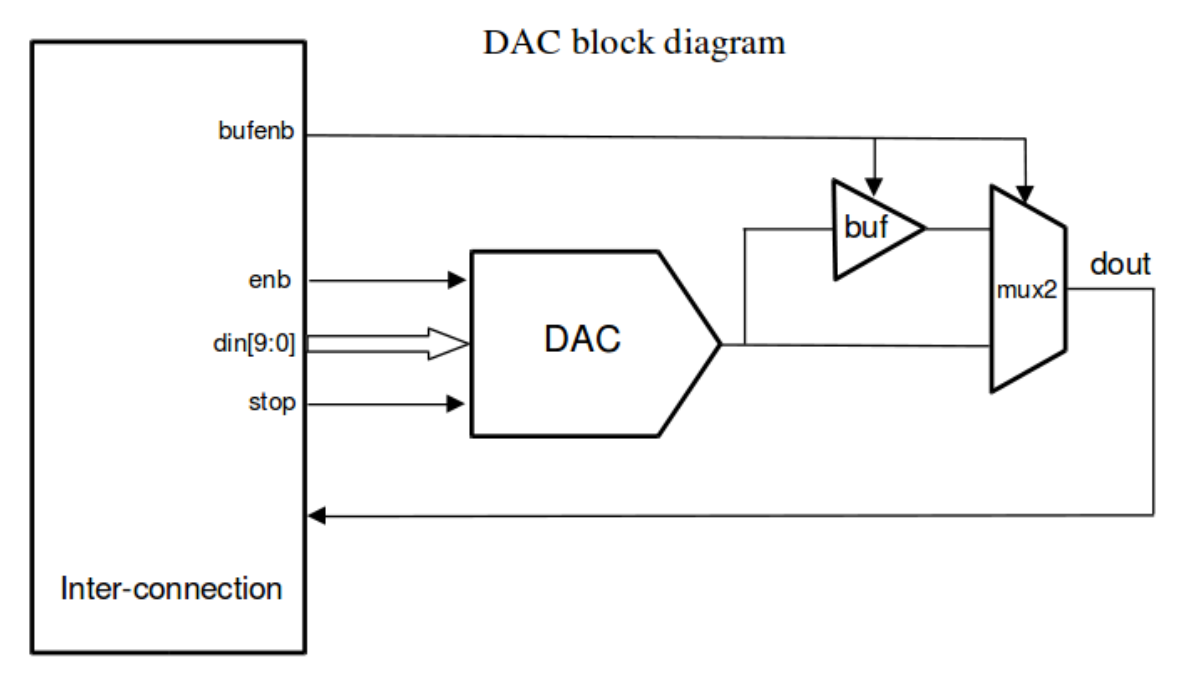

- 2个10位DAC(数模转换器)

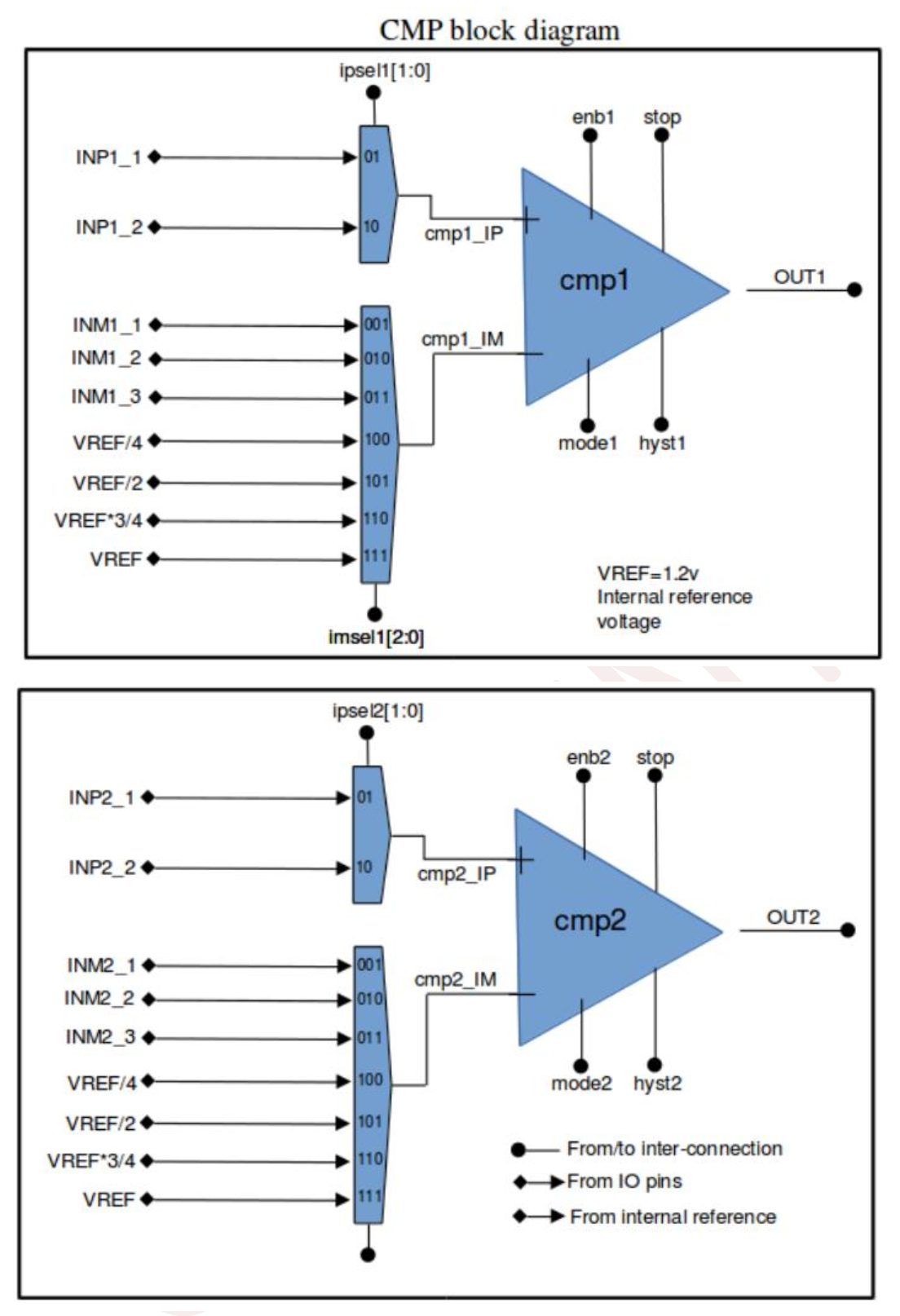

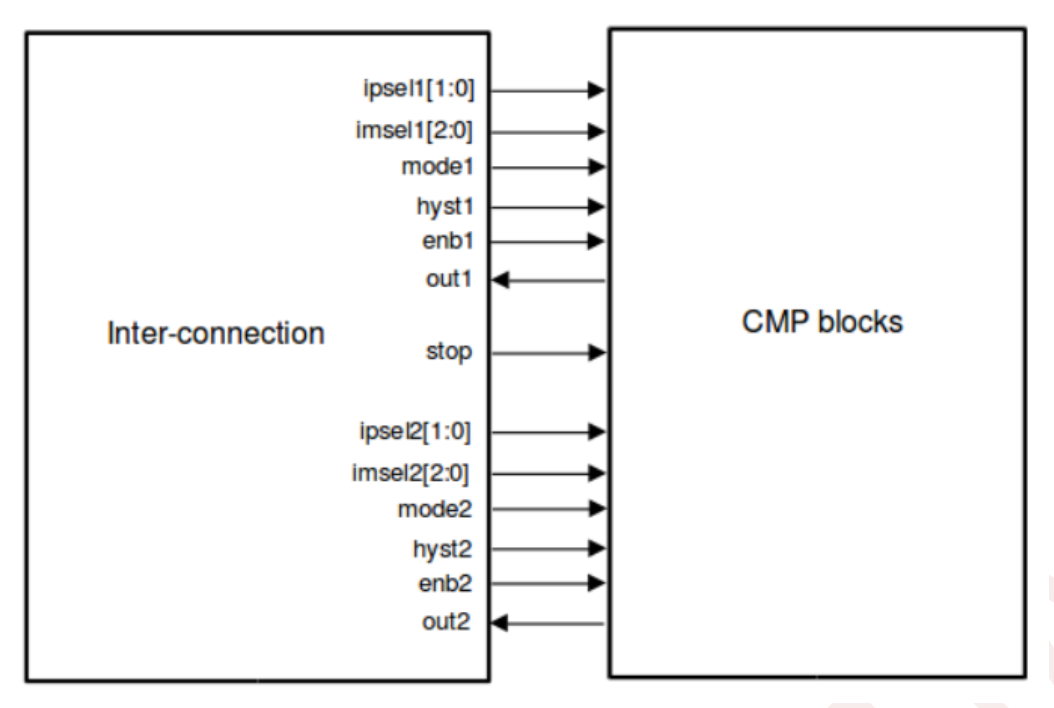

- 2个轨到轨模拟比较器(CMP)

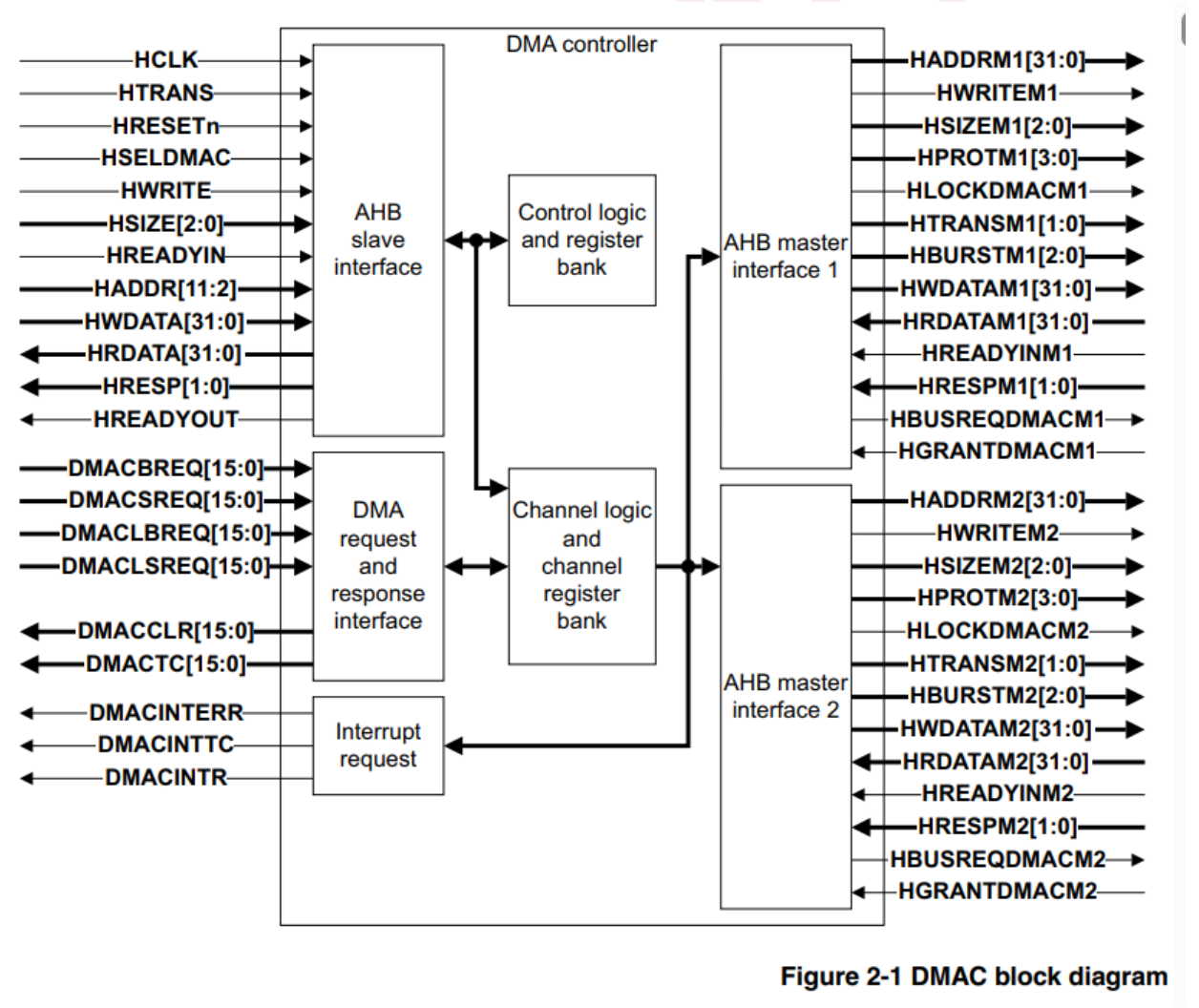

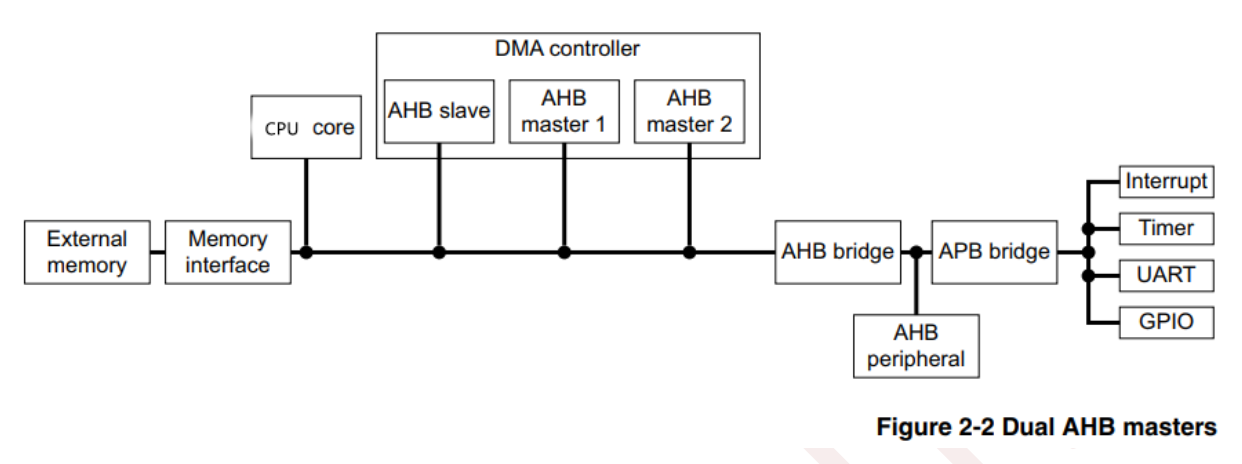

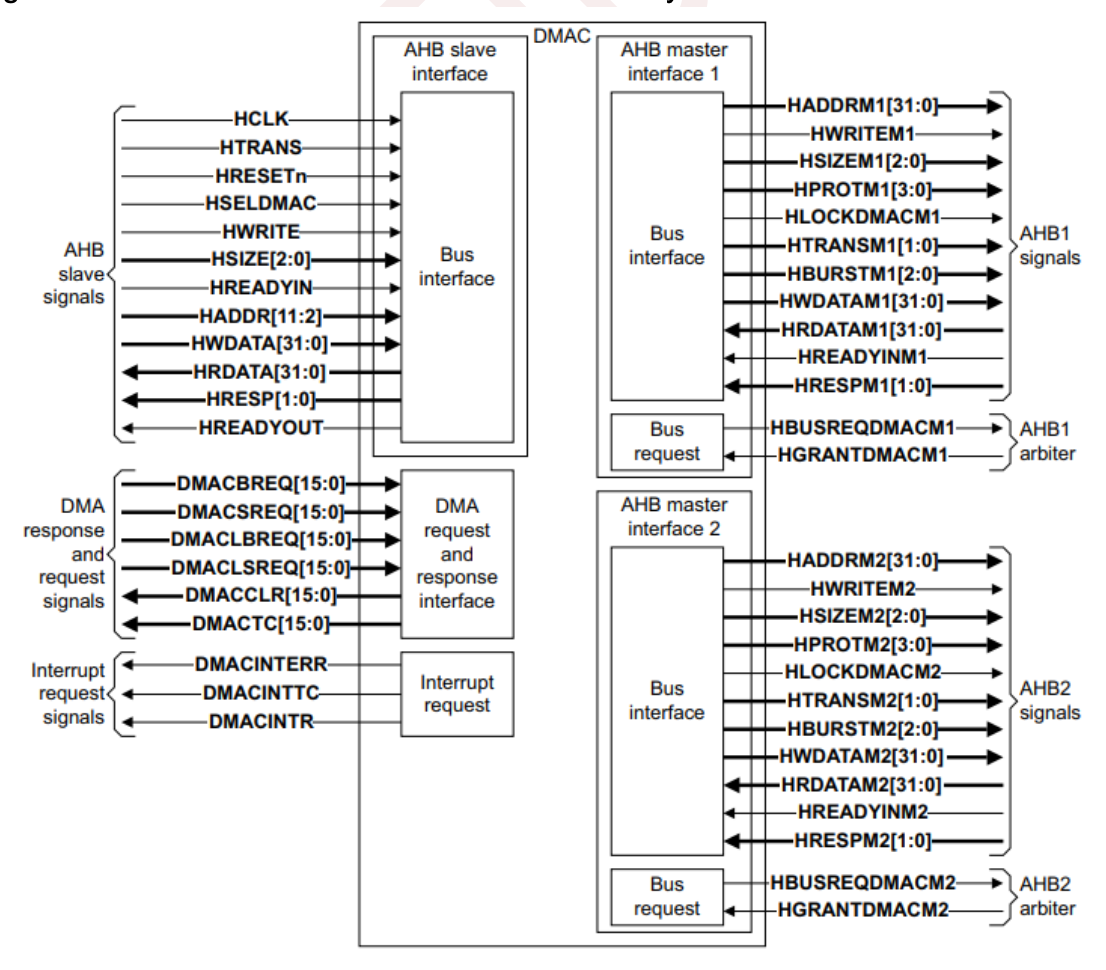

- 通用DMA控制器

- 高级定时器(Advanced-control Timers)

- 最多支持78个通用I/O端口

1.1.5 通信接口¶

- 支持I²C接口

- 支持UART接口

- 支持SPI接口

- 支持CAN接口

1.1.6 其他功能¶

- 调试模式:支持串行线调试(SWD)和JTAG接口

- USB 2.0全速设备/主机控制器,内置PHY

- 支持MII/RMII的10/100以太网MAC,带专用DMA

- 实时时钟(RTC):支持亚秒级精度

- 每颗芯片具备唯一的128位ID

1.2 产品参数¶

| 产品 / 参数 | AG32VF303KCU6 | AG32VF303CCT6 | AG32VF303VCT6 | AG32VH407RCT6 | AG32VF407RGT6 | AG32VF407VGT6 |

|---|---|---|---|---|---|---|

| Flash存储器(KB) | 256K | 256K | 256K | 256K | 1024K | 1024K |

| SRAM(KB) | 128K | 128K | 128K | 128K | 128K | 128K |

| PSRAM | / | / | / | 8MB | / | / |

| 以太网 | 是 | 是 | 是 | 是 | 是 | 是 |

| 定时器 | 2×基本定时器 + 5×高级定时器 | 2×基本定时器 + 5×高级定时器 | 2×基本定时器 + 5×高级定时器 | 2×基本定时器 + 5×高级定时器 | 2×基本定时器 + 5×高级定时器 | 2×基本定时器 + 5×高级定时器 |

| SPI/I²C | 2 | 2 | 2 | 2 | 2 | 2 |

| UART | 5 | 5 | 5 | 5 | 5 | 5 |

| USB(FS) | 是 | 是 | 是 | 是 | 是 | 是 |

| CAN | 1× CAN2.0 | 1× CAN2.0 | 1× CAN2.0 | 1× CAN2.0 | 1× CAN2.0 | 1× CAN2.0 |

| 12位ADC | 3 | 3 | 3 | 3 | 3 | 3 |

| ADC通道数 | 9 | 10 | 16 | 11 | 16 | 16 |

| 10位DAC | 2 | 2 | 2 | 2 | 2 | 2 |

| DAC通道数 | 2 | 2 | 2 | 2 | 2 | 2 |

| 轨到轨模拟比较器 | 2 | 2 | 2 | 2 | 2 | 2 |

| 最大CPU频率 | 248 MHz | 248 MHz | 248 MHz | 248 MHz | 248 MHz | 248 MHz |

| 工作电压范围 | 3.135V ~ 3.465V | 3.135V ~ 3.465V | 3.135V ~ 3.465V | 3.135V ~ 3.465V | 3.135V ~ 3.465V | 3.135V ~ 3.465V |

| 封装形式 | QFN32 | LQFP48 | LQFP100 | LQFP64 | LQFP64 | LQFP100 |

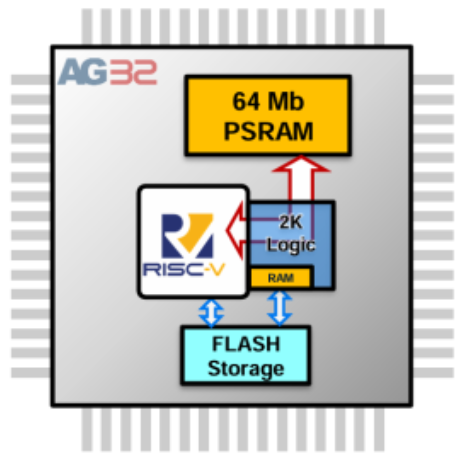

AG32VH407RCT6:AG32 + PSRAM

- MCU + 2K CPLD + 8MB PSRAM

- 支持HyperRAM高速接口

- 提供DMA与FIFO读/写参考设计

1.3 芯片架构¶

1.4 存储器映射(Memory Map)¶

| 区域 | 地址范围 | 描述 |

|---|---|---|

| ROM | 0x0001_0000 – 0x0001_1FFF | 只读存储器 |

| System Control | 0x0300_0000 – 0x0300_0FFF | 系统控制 |

| PLIC | 0x0C00_0000 – 0x0C20_FFFF | 平台级中断控制器 |

| SRAM | 0x2000_0000 – 0x2001_FFFF | 片上SRAM |

| FLASH (XIP) | 0x8000_0000 – 0x80FF_FFFF | 通过XIP方式访问的Flash |

| Option Bytes | 0x8100_0000 – 0x8100_003F | 选项字节配置区 |

| RTC | 0x4000_0000 – 0x4000_007F | 实时时钟 |

| Flash Control | 0x4000_1000 – 0x4000_1FFF | Flash控制寄存器 |

| APB Peripherals | 0x4001_0000 – 0x40FF_FFFF | APB总线外设 |

| AHB Peripherals | 0x4100_0000 – 0x41FF_FFFF | AHB总线外设 |

| External AHB | 0x6000_0000 – 0x7FFF_FFFF | 外部AHB接口地址空间 |

1.5 系统控制 (System Control)¶

设备启动模式(BOOT_MODE)¶

地址偏移量:0x00

| 31–2 | 1 | 0 | |

|---|---|---|---|

| Reserved | BOOT_MODE | BOOT_MODE | |

| RO | RO |

Bit [1:0]:Device boot mode

BOOT0和 BOOT1引脚的数值在复位后的第4个SYSCLK上升沿被锁存。

复位控制(RST_CNTL)¶

地址偏移量: 0x04

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| 31 | RSTF_LPWR | 低功耗复位标志 | 0 | 未检测到复位 |

| 1 | 检测到低功耗复位 | |||

| 30 | RSTF_WDOG | 看门狗复位标志 | 0 | 未检测到复位 |

| 1 | 检测到看门狗复位 | |||

| 29 | RSTF_IWDG | 独立看门狗复位标志 | 0 | 未检测到复位 |

| 1 | 检测到独立看门狗复位 | |||

| 28 | RSTF_SFT | 软件复位标志 | 0 | 未检测到复位 |

| 1 | 检测到软件复位 | |||

| 27 | RSTF_POR | 上电复位标志 | 0 | 未检测到复位 |

| 1 | 检测到上电复位 | |||

| 26 | RSTF_PIN | NRST引脚复位标志 | 0 | 未检测到复位 |

| 1 | 检测到NRST引脚复位 | |||

| 25 | RSTF_EXT | 外部逻辑复位标志 | 0 | 未检测到复位 |

| 1 | 检测到外部逻辑复位 | |||

| 24 | RST_REMOVE | 清除复位标志 | - | 写入1清除所有复位标志 |

| 1 | RST_EXT_EN | 外部逻辑复位使能 | 0 | 禁用外部逻辑复位 |

| 1 | 启用外部逻辑复位 | |||

| 0 | RST_SFT | 软件复位 | - | 写入1触发软件复位 |

电源控制(PWR_CNTL)¶

地址偏移量: 0x08

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| [1:0] | LPWR_MODE | 低功耗模式 | 00 | 进入睡眠模式,使用WFI(等待中断)指令 |

| 01 | 进入停止模式,使用WFI指令 | |||

| 11 | 进入待机模式,使用WFI指令 |

时钟控制(CLK_CNTL)¶

地址偏移量: 0x0C

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| [15:12] | SCLK_DIV_HIGH | Flash SPI时钟分频高位 | 0-15 | Flash SPI时钟由SYS_CLK分频(SCLK_DIV_HIGH + 1),有效范围从0(分频 1)到15(分频16) |

| [11:8] | SCLK_DIV_LOW | Flash SPI时钟分频低位 | - | 必须设置为与SCLK_DIV_HIGH相同的值 |

| 6 | PLL_RDY | PLL准备就绪标志 | 0 | PLL未准备好 |

| 1 | PLL已准备好 | |||

| 5 | PLL_ON | PLL开启标志 | 0 | PLL关闭 |

| 1 | PLL开启 | |||

| 4 | HSE_RDY | HSE准备就绪标志 | 0 | HSE未准备好 |

| 1 | HSE已准备好 | |||

| 3 | HSE_BYP | HSE旁路标志 | 0 | HSE振荡器未旁路 |

| 1 | HSE振荡器已旁路 | |||

| 2 | HSE_ON | HSE开启标志 | 0 | HSE振荡器关闭 |

| 1 | HSE振荡器开启 |

JTAG控制(SWJ_CNTL)¶

地址偏移量: 0x14

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| 4 | NJTRST | NJTRST引脚配置 | 0 | NJTRST用作专用引脚 |

| 1 | NJTRST用作用户引脚 | |||

| 3 | JTDO | JTDO引脚配置 | 0 | JTDO用作专用引脚 |

| 1 | JTDO用作用户引脚 | |||

| 2 | JTDI | JTDI引脚配置 | 0 | JTDI用作专用引脚 |

| 1 | JTDI用作用户引脚 | |||

| 1 | JTMS | JTMS引脚配置 | 0 | JTMS用作专用引脚 |

| 1 | JTMS用作用户引脚 | |||

| 0 | JTCK | JTCK引脚配置 | 0 | JTCK用作专用引脚 |

| 1 | JTCK用作用户引脚 |

调试控制(DBG_CNTL)¶

地址偏移量: 0x1C

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| 4 | DBG_RTC_STOP | 在调试期间停止RTC | - | - |

| 3 | DBG_IWDG_STOP | 在调试期间停止独立看门狗(IWDG) | - | - |

唤醒上升触发器(WKP_RISE_TRG)¶

地址偏移量: 0x20

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| [7:0] | EXT_INTO-7 | 使用EXT_INTO-7从停止模式唤醒设备,触发条件为上升沿 | - | - |

| 8 | ALARM | 使用RTC闹钟从停止模式唤醒设备 | - | - |

唤醒下降触发器(WKP_FALL_TRG)¶

地址偏移量: 0x24

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| [7:0] | EXT_INTO-7 | 使用EXT_INTO-7从停止模式唤醒设备,触发条件为下降沿 | - | - |

| 8 | ALARM | 使用RTC闹钟从停止模式唤醒设备 | - | - |

唤醒待处理寄存器(WKP_PENDING)¶

地址偏移量: 0x28

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| [8:0] | - | 当选择的触发事件发生时,相应的位被置为 1 | - | - |

PBUS时钟分频器(PBUS_DIVIDER)¶

地址偏移量: 0x38

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| [3:0] | PBUS_DIV | APB 时钟由SYS_CLK分频(PBUS_DIV + 1),有效范围从0(分频1)到15(分频16) | - | - |

APB外设复位(APB_RESET)¶

地址偏移量: 0x40

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| [28] | 12C1 | 复位12C1外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [27] | 12C0 | 复位12C0外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [26] | CAN0 | 复位CAN0外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [25] | UART4 | 复位UART4外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [24] | UART3 | 复位UART3外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [23] | UART2 | 复位UART2外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [22] | UART1 | 复位UART1外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [21] | UART0 | 复位UART0外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [20] | GPTIMER4 | 复位GPTIMER4外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [19] | GPTIMER3 | 复位GPTIMER3外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [18] | GPTIMER2 | 复位GPTIMER2外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [17] | GPTIMER1 | 复位GPTIMER1外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [16] | GPTIMER0 | 复位GPTIMER0外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [15] | TIMER1 | 复位TIMER1外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [14] | TIMER0 | 复位TIMER0外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [13] | GPIO9 | 复位GPIO9外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [12] | GPIO8 | 复位GPIO8外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [11] | GPIO7 | 复位GPIO7外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [10] | GPIO6 | 复位GPIO6外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [9] | GPIO5 | 复位GPIO5外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [8] | GPIO4 | 复位GPIO4外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [7] | GPIO3 | 复位GPIO3外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [6] | GPIO2 | 复位GPIO2外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [5] | GPIO1 | 复位GPIO1外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [4] | GPIO0 | 复位GPIO0外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [3] | SPI1 | 复位SPI1外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [2] | SPI0 | 复位SPI0外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [1] | WATCHDOG0 | 复位看门狗0外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [0] | FCBO | 复位FCBO外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 |

AHB外设复位(AHB_RESET)¶

地址偏移量: 0x50

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| [3] | MAC0 | 复位MAC0外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

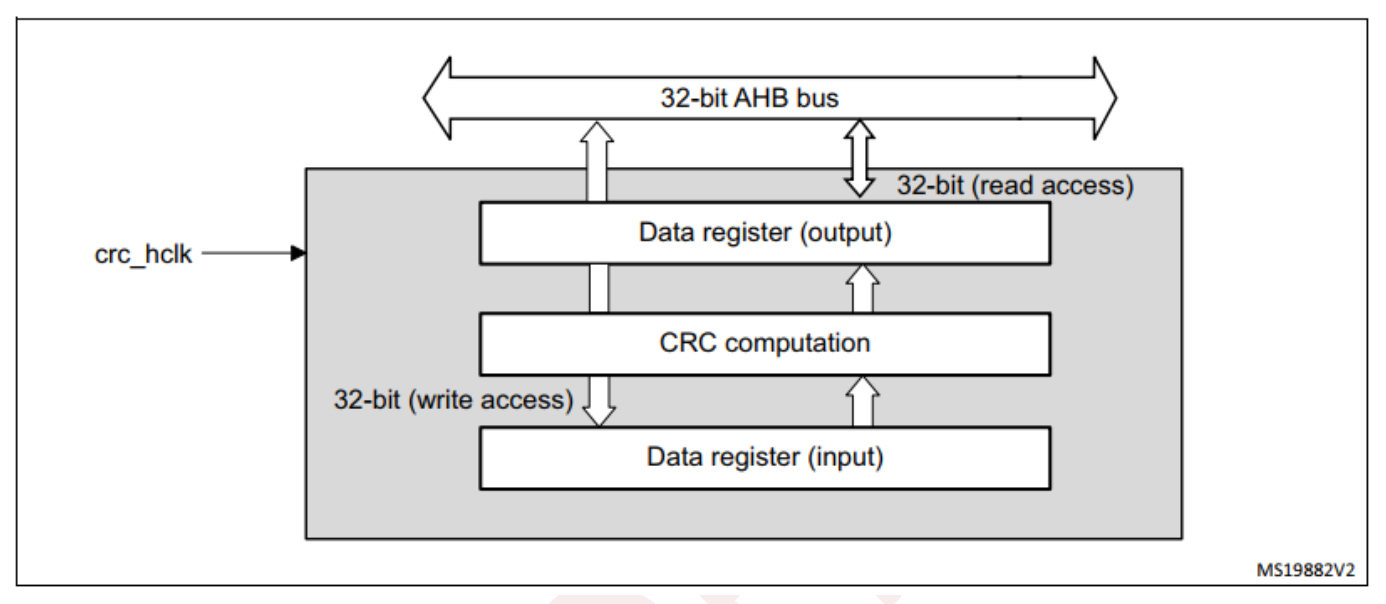

| [2] | CRC0 | 复位CRC0外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [1] | USB0 | 复位USB0外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 | |||

| [0] | DMAC0 | 复位DMAC0外设 | 0 | 复位未被置位 |

| 1 | 复位已被置位 |

APB外设时钟使能(APB_CLKENABLE)¶

地址偏移量: 0x60

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| [n] | - | 启用或禁用对应外设的时钟 | 0 | 外设时钟被禁用 |

| 1 | 外设时钟被启用 |

时钟使能位的分配与 APB_RESET 寄存器相同,您可以根据实际情况参考 APB_RESET 的对应位进行设置。

AHB外设时钟使能(AHB_CLKENABLE)¶

地址偏移量: 0x70

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| [n] | - | 启用或禁用对应外设的时钟 | 0 | 外设时钟被禁用 |

| 1 | 外设时钟被启用 |

时钟使能位的分配与 AHB_RESET 寄存器相同,您可以根据实际情况参考 AHB_RESET 的对应位进行设置。

APB外设时钟在调试期间停止(APB_CLKSTOP)¶

地址偏移量: 0x80

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| [n] | - | 在调试期间停止对应外设的时钟 | 0 | 在调试期间时钟未停止 |

| 1 | 在调试期间时钟已停止 |

时钟停止位的分配与 APB_RESET 寄存器相同,您可以根据实际情况参考 APB_RESET 的对应位进行设置。涉及的外设包括 WATCHDOG、TIMER、GPTIMER和CAN。

设备ID代码(DEVICE_ID)¶

地址偏移量: 0x100

| 位 | 名称 | 描述 | 值 | 含义 |

|---|---|---|---|---|

| [31:0] | - | 返回芯片设备ID | 0x40200001 | 芯片设备ID |

返回的是芯片的设备ID,且为只读寄存器。

2 引脚定义(Pin Definition)¶

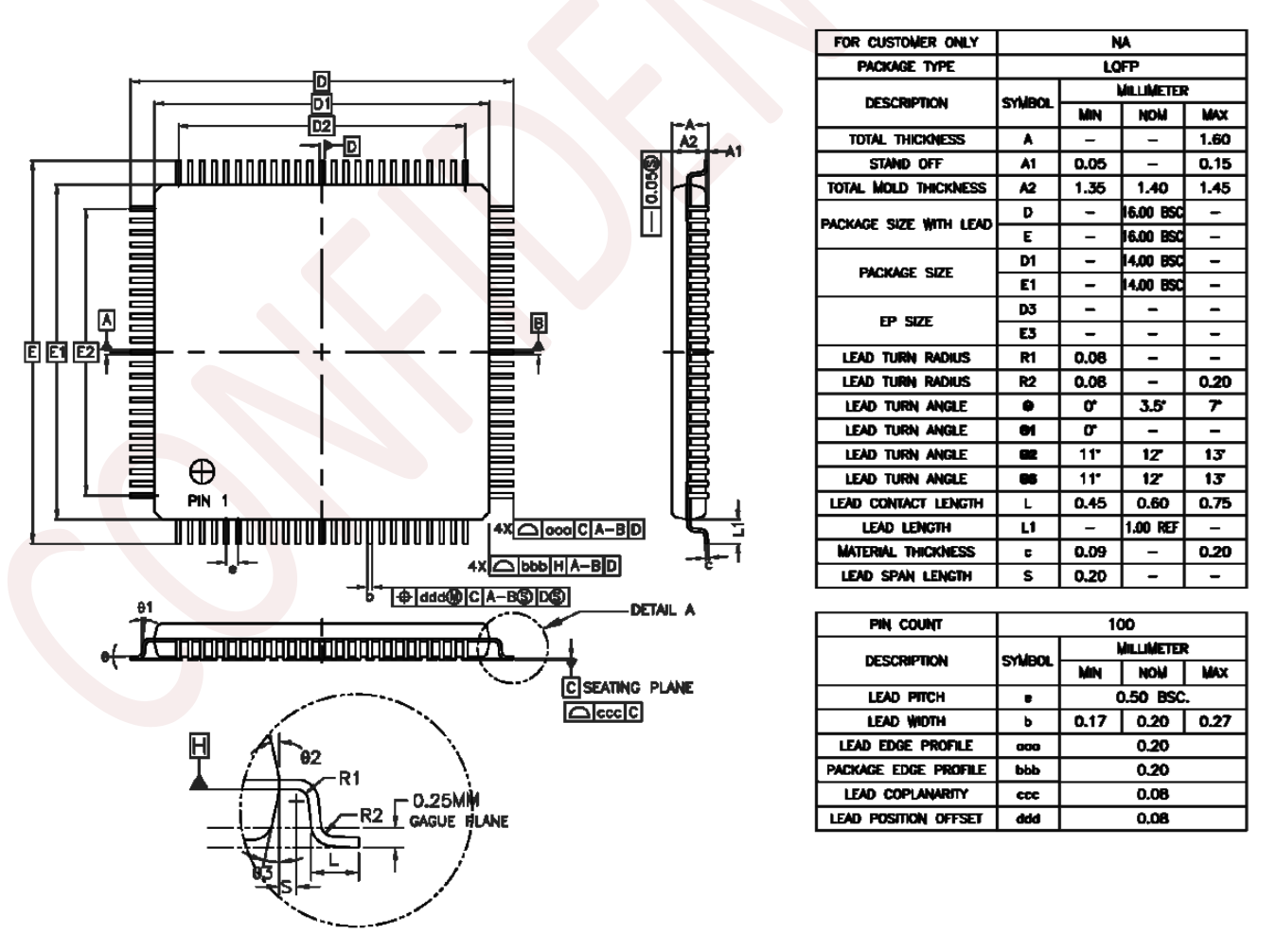

2.1 LQFP-100¶

| 引脚号 | 引脚名称 | 功能描述(中英文) |

|---|---|---|

| 1 | PIN_1 | IO |

| 2 | PIN_2 | IO |

| 3 | PIN_3 | IO |

| 4 | PIN_4 | IO |

| 5 | PIN_5 | IO |

| 6 | VBAT | VBAT 供电引脚 |

| 7 | PIN_7 | IO / RTC |

| 8 | OSC32_IN | 32kHz 晶振输入 |

| 9 | OSC32_OUT | 32kHz 晶振输出 |

| 10 | VSS33 | 地(GND) |

| 11 | VDD33 | 3.3V 电源 |

| 12 | OSC_IN | 主晶振输入 |

| 13 | OSC_OUT | 主晶振输出 |

| 14 | NRST | 复位输入 |

| 15 | PIN_15 | IO / ADC_IN10 |

| 16 | PIN_16 | IO / ADC_IN11 |

| 17 | PIN_17 | IO / ADC_IN12 |

| 18 | PIN_18 | IO / ADC_IN13 |

| 19 | NC | 不连接(NC) |

| 20 | VSSA | 模拟地(GNDA) |

| 21 | VREFP | 模拟参考电压输入 |

| 22 | VDDA | 模拟电源 |

| 23 | PIN_23 | IO / WKUP / ADC_IN0 / CMP_PA0 |

| 24 | PIN_24 | IO / ADC_IN1 / CMP_PA1 |

| 25 | PIN_25 | IO / ADC_IN2 / CMP_PA2 |

| 26 | PIN_26 | IO / ADC_IN3 / CMP_PA3 |

| 27 | VSS33 | 地(GND) |

| 28 | VDD33 | 3.3V 电源 |

| 29 | PIN_29 | IO / ADC_IN4 / CMP_PA4 / DAC0 |

| 30 | PIN_30 | IO / ADC_IN5 / CMP_PA5 / DAC1 |

| 31 | PIN_31 | IO / ADC_IN6 |

| 32 | PIN_32 | IO / ADC_IN7 |

| 33 | PIN_33 | IO / ADC_IN14 |

| 34 | PIN_34 | IO / ADC_IN15 |

| 35 | PIN_35 | IO / ADC_IN8 |

| 36 | PIN_36 | IO / ADC_IN9 |

| 37 | PIN_37 | IO / BOOT1 |

| 38~48 | PIN_38~48 | IO |

| 49 | NC | 不连接(NC) |

| 50 | VDD33 | 3.3V 电源 |

| 51~67 | PIN_51~67 | IO |

| 68 | PIN_68 | IO / UART0_TX |

| 69 | PIN_69 | IO / UART0_RX |

| 70 | PIN_70 | IO / USBDM |

| 71 | PIN_71 | IO / USBDP |

| 72 | PIN_72 | IO / JTMS |

| 73 | NC | 不连接(NC) |

| 74 | VSS33 | 地(GND) |

| 75 | VDD33 | 3.3V 电源 |

| 76 | PIN_76 | IO / JTCK |

| 77 | PIN_77 | IO / JTDI |

| 78~88 | PIN_78~88 | IO |

| 89 | PIN_89 | IO / JTDO |

| 90 | PIN_90 | IO / JNTRST |

| 91~92 | PIN_91~92 | IO |

| 93 | PIN_93 | IO |

| 94 | BOOT0 | 启动模式选择 |

| 95~98 | PIN_95~98 | IO |

| 99 | VSS33 | 地(GND) |

| 100 | VDD33 | 3.3V 电源 |

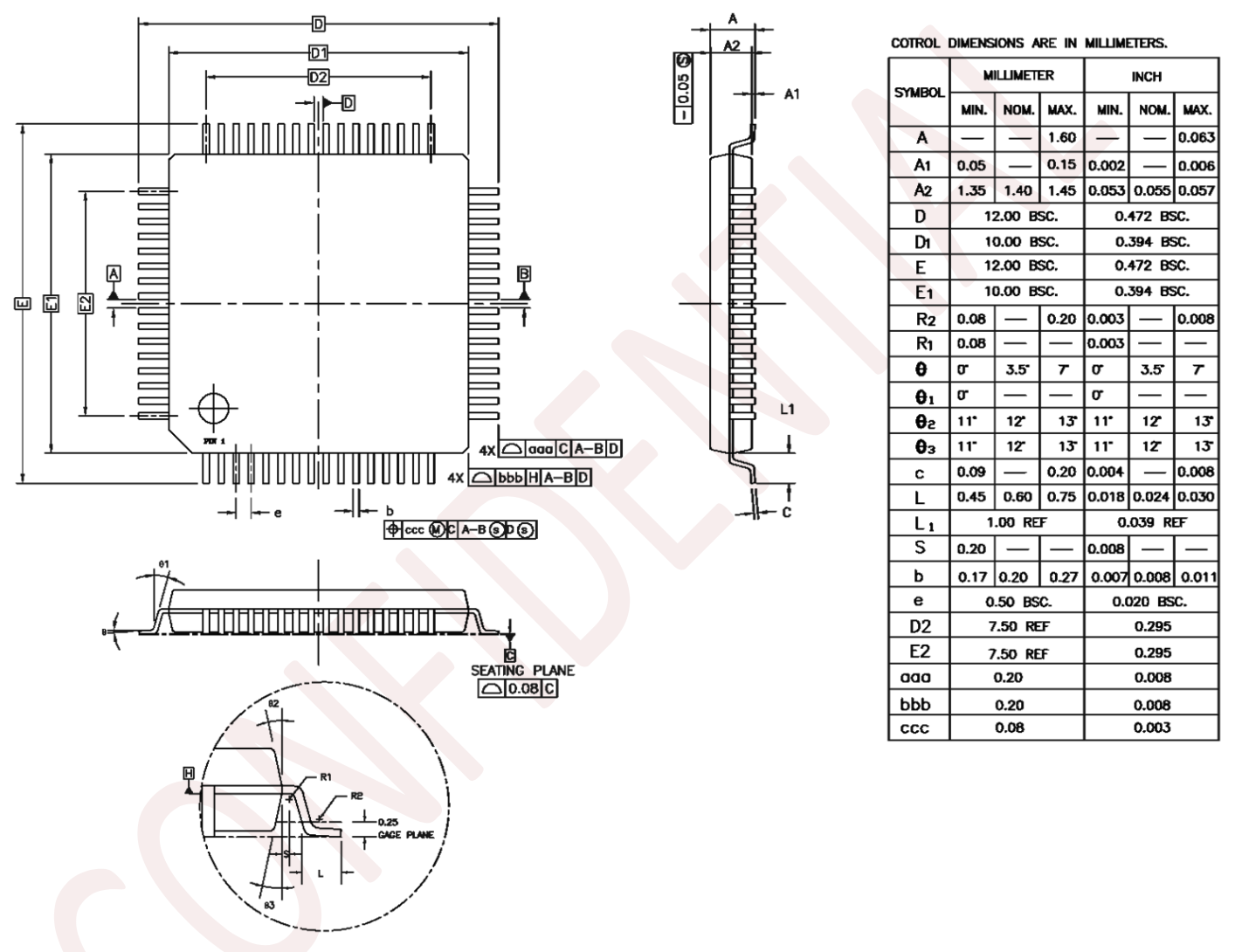

2.2 LQFP-64¶

| 引脚号 | 引脚名称 | 功能描述(中英文) |

|---|---|---|

| 1 | VBAT | VBAT 电源输入 |

| 2 | PIN_2 | IO / RTC |

| 3 | OSC32_IN | 32kHz 晶振输入 |

| 4 | OSC32_OUT | 32kHz 晶振输出 |

| 5 | OSC_IN | 主晶振输入 |

| 6 | OSC_OUT | 主晶振输出 |

| 7 | NRST | 复位引脚 |

| 8 | PIN_8 | IO / ADC_IN10 |

| 9 | PIN_9 | IO / ADC_IN11 |

| 10 | PIN_10 | IO / ADC_IN12 |

| 11 | PIN_11 | IO / ADC_IN13 |

| 12 | VSSA | 模拟地(GNDA) |

| 13 | VDDA | 模拟电源 |

| 14 | PIN_14 | IO / WKUP / ADC_IN0 / CMP_PA0 |

| 15 | PIN_15 | IO / ADC_IN1 / CMP_PA1 |

| 16 | PIN_16 | IO / ADC_IN2 / CMP_PA2 |

| 17 | PIN_17 | IO / ADC_IN3 / CMP_PA3 |

| 18 | VSS33 | 地(GND) |

| 19 | VDD33 | 3.3V 电源 |

| 20 | PIN_20 | IO / ADC_IN4 / CMP_PA4 / DAC0 |

| 21 | PIN_21 | IO / ADC_IN5 / CMP_PA5 / DAC1 |

| 22 | PIN_22 | IO / ADC_IN6 |

| 23 | PIN_23 | IO / ADC_IN7 |

| 24 | PIN_24 | IO / ADC_IN14 |

| 25 | PIN_25 | IO / ADC_IN15 |

| 26 | PIN_26 | IO / ADC_IN8 |

| 27 | PIN_27 | IO / ADC_IN9 |

| 28 | PIN_28 | IO / BOOT1 |

| 29 | PIN_29 | IO |

| 30 | PIN_30 | IO |

| 31 | PIN_31 | IO |

| 32 | VDD33 | 3.3V 电源 |

| 33 | PIN_33 | IO |

| 34 | PIN_34 | IO |

| 35 | PIN_35 | IO |

| 36 | PIN_36 | IO |

| 37 | PIN_37 | IO |

| 38 | PIN_38 | IO |

| 39 | PIN_39 | IO |

| 40 | PIN_40 | IO |

| 41 | PIN_41 | IO |

| 42 | PIN_42 | IO / UART0_TX |

| 43 | PIN_43 | IO / UART0_RX |

| 44 | PIN_44 | IO / USBDM |

| 45 | PIN_45 | IO / USBDP |

| 46 | PIN_46 | IO / JTMS |

| 47 | PIN_47 | IO |

| 48 | VDD33 | 3.3V 电源 |

| 49 | PIN_49 | IO / JTCK |

| 50 | PIN_50 | IO / JTDI |

| 51 | PIN_51 | IO |

| 52 | PIN_52 | IO |

| 53 | PIN_53 | IO |

| 54 | PIN_54 | IO |

| 55 | PIN_55 | IO / JTDO |

| 56 | PIN_56 | IO / JNTRST |

| 57 | PIN_57 | IO |

| 58 | PIN_58 | IO |

| 59 | PIN_59 | IO |

| 60 | BOOT0 | 启动引脚 BOOT0 |

| 61 | PIN_61 | IO |

| 62 | PIN_62 | IO |

| 63 | VSS33 | 地(GND) |

| 64 | VDD33 | 3.3V 电源 |

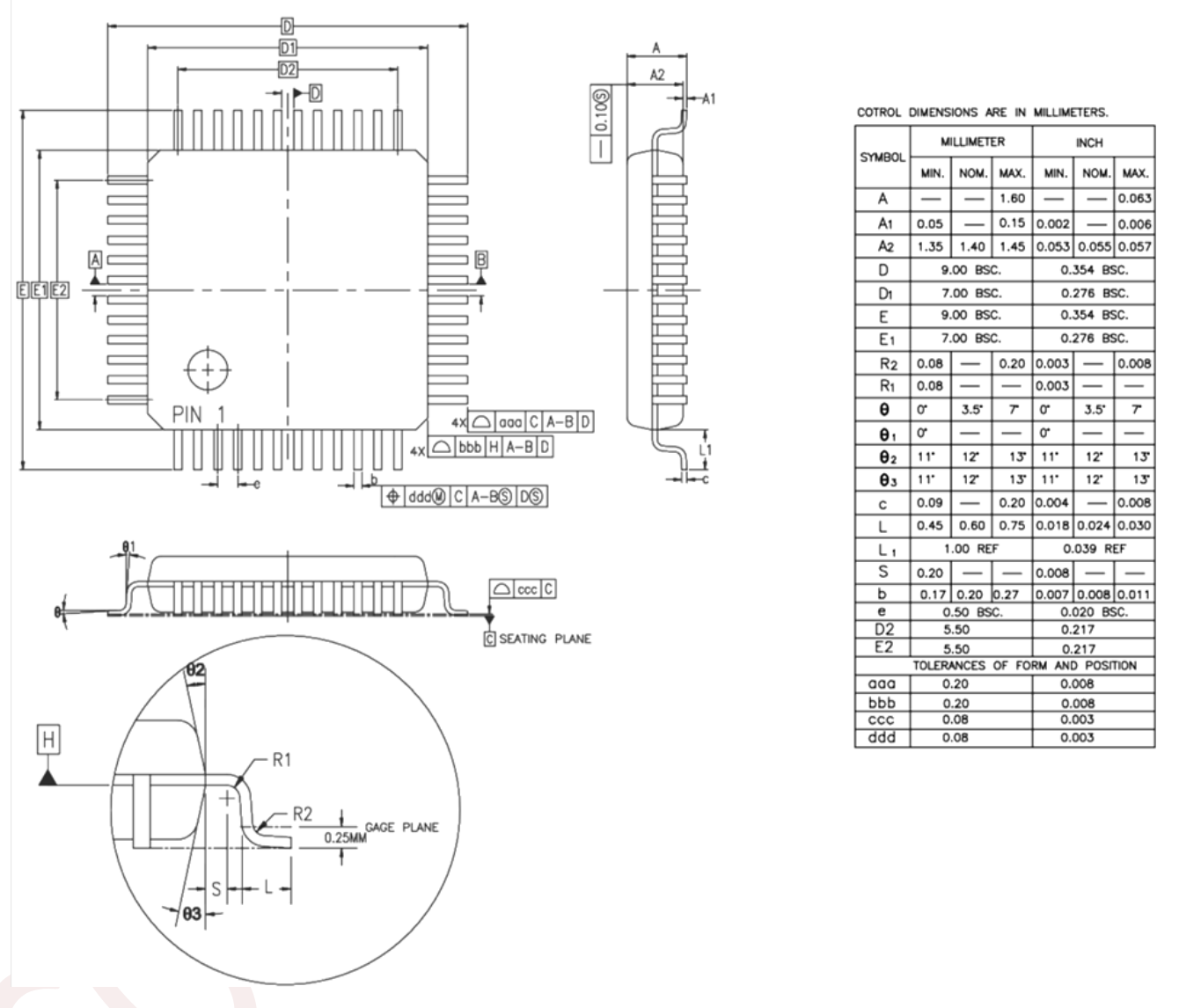

2.3 LQFP-48¶

| Pin | Pin Name | Function 中文说明 |

|---|---|---|

| 1 | VBAT | VBAT 电池供电引脚 |

| 2 | PIN_2 | IO/RTC 实时时钟/通用IO |

| 3 | OSC32_IN | 32kHz低速晶振输入 |

| 4 | OSC32_OUT | 32kHz低速晶振输出 |

| 5 | OSC_IN | 主晶振输入 |

| 6 | OSC_OUT | 主晶振输出 |

| 7 | NRST | 复位引脚 |

| 8 | VSSA | 模拟地 |

| 9 | VDDA | 模拟电源 |

| 10 | PIN_10 | IO/WKUP/ADC_IN0/CMP_PA0 唤醒/ADC/比较器 |

| 11 | PIN_11 | IO/ADC_IN1/CMP_PA1 |

| 12 | PIN_12 | IO/ADC_IN2/CMP_PA2 |

| 13 | PIN_13 | IO/ADC_IN3/CMP_PA3 |

| 14 | PIN_14 | IO/ADC_IN4/CMP_PA4/DAC0 |

| 15 | PIN_15 | IO/ADC_IN5/CMP_PA5/DAC1 |

| 16 | PIN_16 | IO/ADC_IN6 |

| 17 | PIN_17 | IO/ADC_IN7 |

| 18 | PIN_18 | IO/ADC_IN8 |

| 19 | PIN_19 | IO/ADC_IN9 |

| 20 | PIN_20 | IO/BOOT1 启动配置 |

| 21 | PIN_21 | IO |

| 22 | PIN_22 | IO |

| 23 | VSS33 | 数字地 |

| 24 | VDD33 | 数字电源 |

| 25 | PIN_25 | IO |

| 26 | PIN_26 | IO |

| 27 | PIN_27 | IO |

| 28 | PIN_28 | IO |

| 29 | PIN_29 | IO |

| 30 | PIN_30 | IO/UART0_TX 串口发送 |

| 31 | PIN_31 | IO/UART0_RX 串口接收 |

| 32 | PIN_32 | IO/USBDM USB负差分线 |

| 33 | PIN_33 | IO/USBDP USB正差分线 |

| 34 | PIN_34 | IO/JTMS JTAG模式选择 |

| 35 | PIN_35 | IO |

| 36 | VDD33 | 数字电源 |

| 37 | PIN_37 | IO/JTCK JTAG时钟 |

| 38 | PIN_38 | IO/JTDI JTAG数据输入 |

| 39 | PIN_39 | IO/JTDO JTAG数据输出 |

| 40 | PIN_40 | IO/JNTRST JTAG复位 |

| 41 | PIN_41 | IO |

| 42 | PIN_42 | IO |

| 43 | PIN_43 | IO |

| 44 | BOOT0 | 启动配置引脚 |

| 45 | PIN_45 | IO |

| 46 | PIN_46 | IO |

| 47 | VSS33 | 数字地 |

| 48 | VDD33 | 数字电源 |

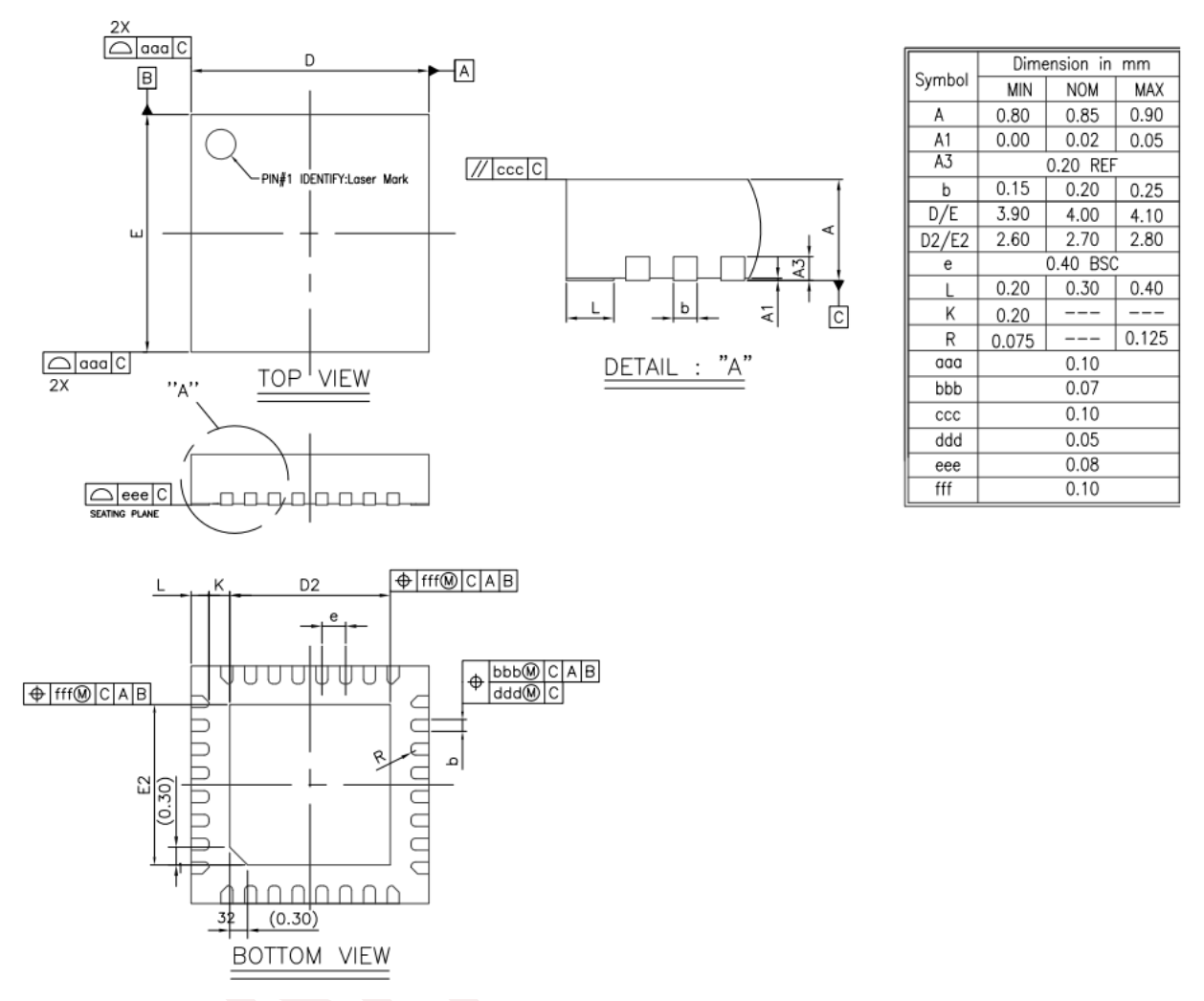

2.4 QFN-32¶

| Pin | Pin Name | Function 中文说明 |

|---|---|---|

| 1 | PIN_1 | IO/RTC 实时时钟/通用IO |

| 2 | PIN_2 | IO/OSC_IN 主晶振输入 |

| 3 | PIN_3 | IO/OSC_OUT 主晶振输出 |

| 4 | NRST | 复位引脚 |

| 5 | PIN_5 | IO/ADC_IN12 模拟输入 |

| 6 | VDDA33 | 模拟电源 |

| 7 | PIN_7 | IO/WKUP/ADC_IN0/CMP_PA0 唤醒/ADC/比较器 |

| 8 | PIN_8 | IO/ADC_IN1/CMP_PA1 |

| 9 | PIN_9 | IO/ADC_IN2/CMP_PA2 |

| 10 | PIN_10 | IO/ADC_IN3/CMP_PA3 |

| 11 | PIN_11 | IO/ADC_IN4/CMP_PA4/DAC0 |

| 12 | PIN_12 | IO/ADC_IN5/CMP_PA5/DAC1 |

| 13 | PIN_13 | IO/ADC_IN6 |

| 14 | PIN_14 | IO/ADC_IN7 |

| 15 | PIN_15 | IO/BOOT1 启动配置 |

| 16 | VDD33 | 数字电源 |

| 17 | GND | 地 |

| 18 | PIN_18 | IO |

| 19 | PIN_19 | IO |

| 20 | PIN_20 | IO/UART0_TX 串口发送 |

| 21 | PIN_21 | IO/UART0_RX 串口接收 |

| 22 | PIN_22 | IO/USBDM USB负差分线 |

| 23 | PIN_23 | IO/USBDP USB正差分线 |

| 24 | PIN_24 | IO/JTMS JTAG模式选择 |

| 25 | PIN_25 | IO/JTCK JTAG时钟 |

| 26 | PIN_26 | IO/JTDI JTAG数据输入 |

| 27 | PIN_27 | IO/JTDO JTAG数据输出 |

| 28 | PIN_28 | IO/JNTRST JTAG复位 |

| 29 | PIN_29 | IO |

| 30 | BOOT0 | 启动配置引脚 |

| 31 | PIN_31 | IO |

| 32 | VDD33 | 数字电源 |

2.5 AG32VH407RCT6 与 AG32VF407RGT6¶

| Pin | AG32VH407RCT6 引脚名 | 功能描述 | AG32VF407RGT6 引脚名 | 功能描述 |

|---|---|---|---|---|

| 1 | VBAT | VBAT | VBAT | VBAT |

| 2 | PIN_2 | IO_RTC | PIN_2 | IO_RTC |

| 3 | OSC32_IN | OSC32_IN | OSC32_IN | OSC32_IN |

| 4 | OSC32_OUT | OSC32_OUT | OSC32_OUT | OSC32_OUT |

| 5 | OSC_IN | OSC_IN | OSC_IN | OSC_IN |

| 6 | OSC_OUT | OSC_OUT | OSC_OUT | OSC_OUT |

| 7 | NRST | NRST | NRST | NRST |

| 8 | RWDS | RWDS | PIN_8 | IO_ADC_IN10 |

| 9 | PIN_9 | IO_ADC_IN11 | PIN_9 | IO_ADC_IN11 |

| 10 | PIN_10 | IO_ADC_IN12 | PIN_10 | IO_ADC_IN12 |

| 11 | PIN_11 | IO_ADC_IN13 | PIN_11 | IO_ADC_IN13 |

| 12 | GND | GND | GND | GND |

| 13 | VDD33 | VDD33 | VDD33 | VDD33 |

| 14 | PIN_14 | IO_WKUP_ADC_IN0_CMP_PA0 | PIN_14 | IO_WKUP_ADC_IN0_CMP_PA0 |

| 15 | PIN_15 | IO_ADC_IN1_CMP_PA1 | PIN_15 | IO_ADC_IN1_CMP_PA1 |

| 16 | PIN_16 | IO_ADC_IN2_CMP_PA2 | PIN_16 | IO_ADC_IN2_CMP_PA2 |

| 17 | PIN_17 | IO_ADC_IN3_CMP_PA3 | PIN_17 | IO_ADC_IN3_CMP_PA3 |

| 18 | GND | GND | GND | GND |

| 19 | VDD33 | VDD33 | VDD33 | VDD33 |

| 20 | PIN_20 | IO_ADC_IN5_CMP_PA5_DAC1 | PIN_20 | IO_ADC_IN4_CMP_PA4_DAC0 |

| 21 | PIN_21 | IO_ADC_IN7 | PIN_21 | IO_ADC_IN5_CMP_PA5_DAC1 |

| 22 | RWDS | RWDS | PIN_22 | IO_ADC_IN6 |

| 23 | PIN_23 | IO_ADC_IN15 | PIN_23 | IO_ADC_IN7 |

| 24 | PIN_24 | IO_ADC_IN9 | PIN_24 | IO_ADC_IN14 |

| 25 | PIN_25 | IO_BOOT1 | PIN_25 | IO_ADC_IN15 |

| 26 | PIN_26 | IO | PIN_26 | IO_ADC_IN8 |

| 27 | PIN_27 | IO | PIN_27 | IO_ADC_IN9 |

| 28 | PIN_28 | IO | PIN_28 | IO_BOOT1 |

| 29 | PIN_29 | IO | PIN_29 | IO |

| 30 | VDD33 | VDD33 | PIN_30 | IO |

| 31 | GND | GND | PIN_31 | IO |

| 32 | VDD33 | VDD33 | VDD33 | VDD33 |

| 33 | PIN_33 | IO | PIN_33 | IO |

| 34 | PIN_34 | IO | PIN_34 | IO |

| 35 | PIN_35 | IO | PIN_35 | IO |

| 36 | PIN_36 | IO | PIN_36 | IO |

| 37 | PIN_37 | IO | PIN_37 | IO |

| 38 | PIN_38 | IO | PIN_38 | IO |

| 39 | PIN_39 | IO | PIN_39 | IO |

| 40 | PIN_40 | IO | PIN_40 | IO |

| 41 | PIN_41 | IO | PIN_41 | IO |

| 42 | PIN_42 | IO_UART0_TX | PIN_42 | IO_UART0_TX |

| 43 | PIN_43 | IO_UART0_RX | PIN_43 | IO_UART0_RX |

| 44 | PIN_44 | IO_USBDM | PIN_44 | IO_USBDM |

| 45 | PIN_45 | IO_USBDP | PIN_45 | IO_USBDP |

| 46 | PIN_46 | IO_JTMS | PIN_46 | IO_JTMS |

| 47 | PIN_47 | IO | PIN_47 | IO |

| 48 | VDD33 | VDD33 | VDD33 | VDD33 |

| 49 | PIN_49 | IO_JTCK | PIN_49 | IO_JTCK |

| 50 | PIN_50 | IO_JTDI | PIN_50 | IO_JTDI |

| 51 | PIN_51 | IO | PIN_51 | IO |

| 52 | PIN_52 | IO | PIN_52 | IO |

| 53 | PIN_53 | IO | PIN_53 | IO |

| 54 | PIN_54 | IO | PIN_54 | IO |

| 55 | PIN_55 | IO_JTDO | PIN_55 | IO_JTDO |

| 56 | PIN_56 | IO_JNTRST | PIN_56 | IO_JNTRST |

| 57 | PIN_57 | IO | PIN_57 | IO |

| 58 | PIN_58 | IO | PIN_58 | IO |

| 59 | PIN_59 | IO | PIN_59 | IO |

| 60 | BOOT0 | BOOT0 | BOOT0 | BOOT0 |

| 61 | PIN_61 | IO | PIN_61 | IO |

| 62 | PIN_62 | IO | PIN_62 | IO |

| 63 | GND | GND | GND | GND |

| 64 | VDD33 | VDD33 | VDD33 | VDD33 |

注意:

- RWDS(引脚8和引脚22)需要在外部短接。

- VDD33需通过磁珠与PCB上的其他电源单独隔离。

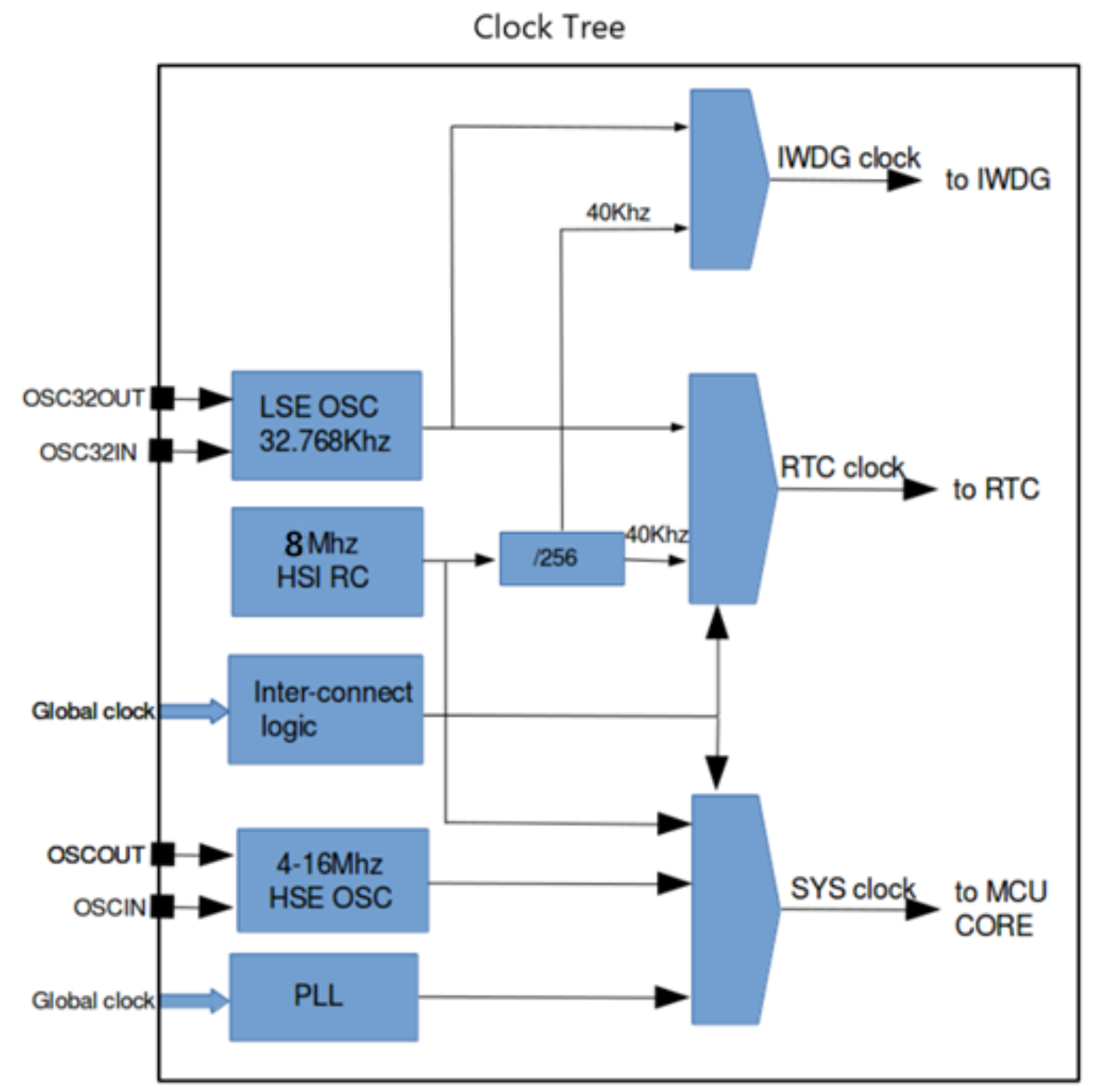

3 时钟系统¶

3.1 时钟源¶

系统时钟(SYSCLK)可由以下几种时钟源驱动:

- HSI 振荡器时钟

- HSE 振荡器时钟

- PLL 时钟

- 互联全局时钟(FPGA 内核)

设备还提供以下两种辅助时钟源:

-

40 kHz 低速内部 RC 振荡器(LSI)

用于驱动独立看门狗(IWDG),并可选用于从停止/待机模式下自动唤醒的 RTC。

-

32.768 kHz 低速外部晶体(LSE 晶体)

可选用于驱动实时时钟(RTCCLK)。

每个时钟源在未使用时都可以独立开启或关闭,以优化功耗。

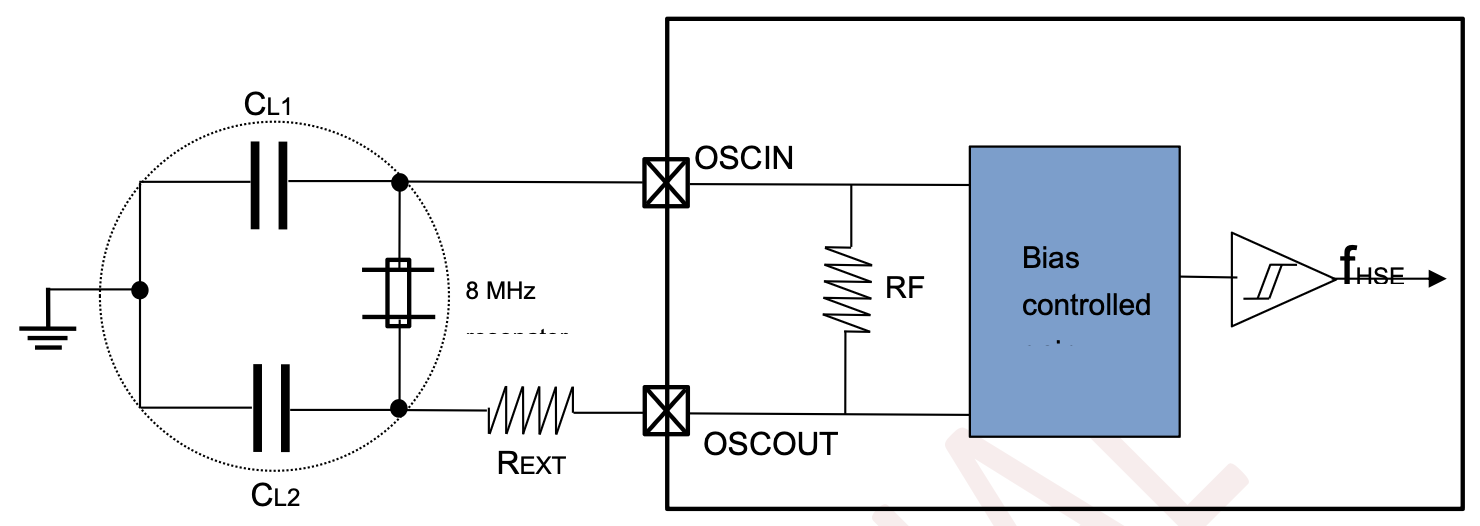

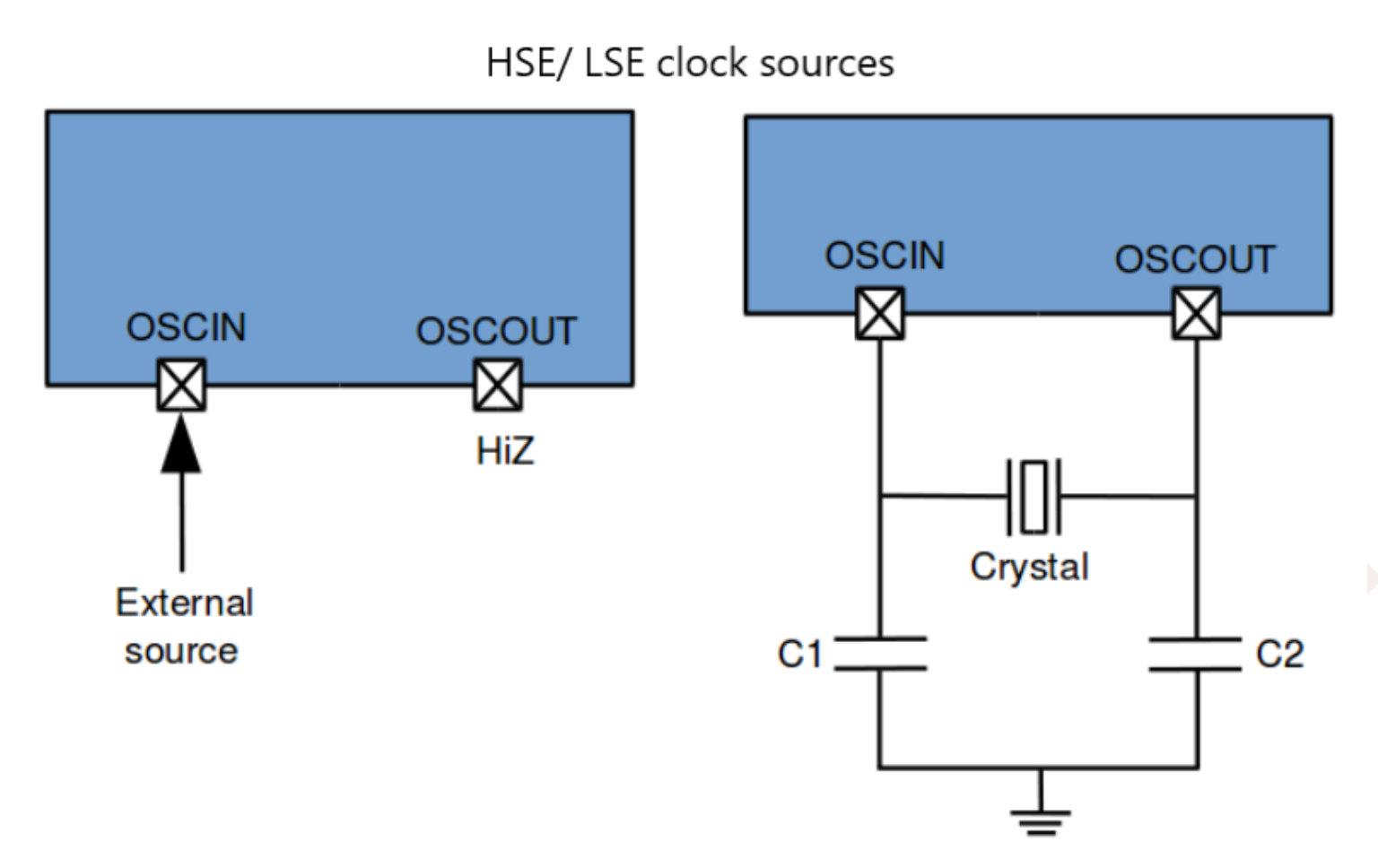

3.2 HSE 时钟¶

高速外部时钟信号(HSE)可以由以下两种时钟源生成:

- HSE 外部晶体/陶瓷谐振器

- HSE 用户外部时钟

谐振器和负载电容器必须尽可能靠近振荡器引脚,以减少输出失真和启动稳定时间。负载电容的值必须根据所选振荡器进行调整。

外部源(HSE Bypass)¶

在此模式下,必须提供外部时钟源,频率最高可达 100 MHz。

通过在时钟控制寄存器(RCC_CR)中设置 HSEBYP 和 HSEON 位来选择此模式。

外部时钟信号(方波、正弦波或三角波)必须驱动 OSC_IN 引脚,且 OSC_OUT 引脚应保持高阻态(hi-Z)。

外部晶体/陶瓷谐振器(HSE 晶体)¶

4 至 24 MHz 的外部振荡器具有在主时钟上产生非常准确频率的优势。

HSERDY 标志指示高速外部振荡器是否稳定。启动时,时钟直到此位被硬件设置后才会释放。

可以使用 HSEON 位打开或关闭 HSE 晶体。

3.3 HSI 时钟¶

HSI 时钟信号由内部振荡器生成,可以直接作为系统时钟使用。

HSI 内部振荡器的优势在于提供了一种低成本的时钟源(无需外部组件)。它的启动时间也比 HSE 晶体振荡器更快。

3.4 PLL 时钟¶

内部 PLL 可用于倍增 HSE 晶体输出时钟频率。

如果在应用中使用 USB 接口,则必须将 PLL 配置为输出 48 MHz 的时钟。这是为了提供 48 MHz 的 USBCLK 时钟。

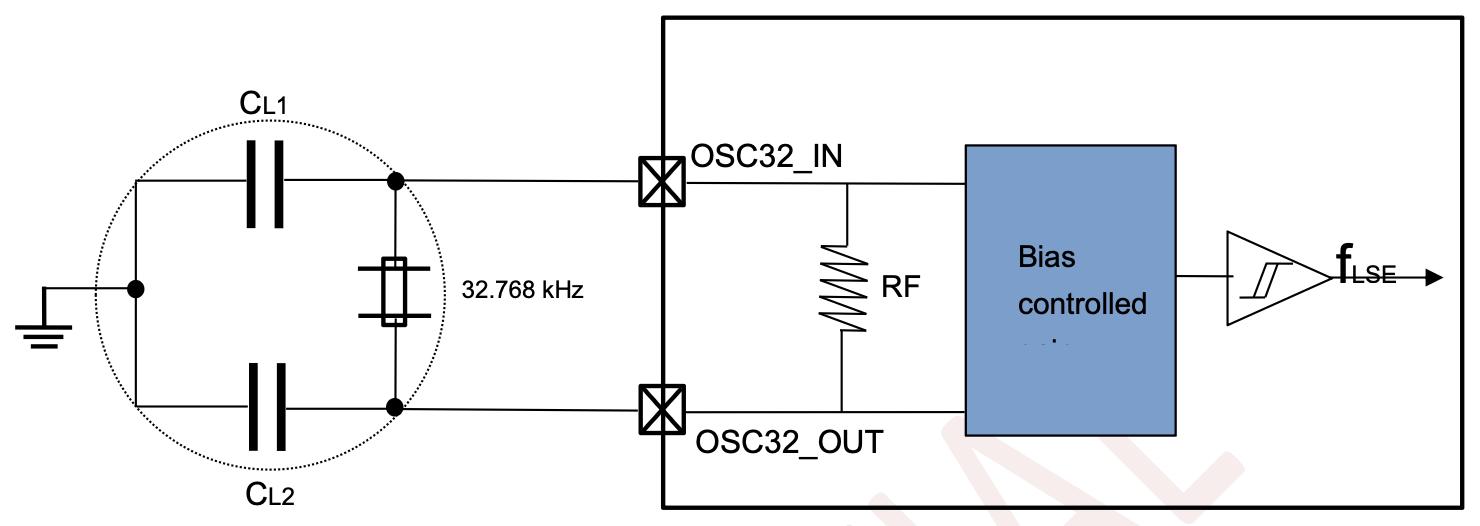

3.5 LSE 时钟¶

LSE 晶体是一种 32.768 kHz 的低速外部晶体或陶瓷谐振器。它的优势在于为实时时钟外设(RTC)提供低功耗且高度精确的时钟源,用于时钟/日历或其他定时功能。

LSE 晶体通过在备份域控制寄存器中设置 LSEON 位来打开和关闭。

备份域控制寄存器中的 LSERDY 标志指示 LSE 晶体是否稳定。启动时,LSE 晶体输出的时钟信号在硬件设置此位之前不会释放。

外部源(LSE Bypass)¶

在此模式下,必须提供外部时钟源,频率最高可达 1 MHz。

外部时钟信号(方波、正弦波或三角波)必须驱动 OSC32_IN 引脚,且 OSC32_OUT 引脚应保持高阻态(Hi-Z)。

3.6 LSI 时钟¶

LSI 时钟是将 HSI 时钟除以 256 得到的。它可以在停止模式下继续运行,用于独立看门狗(IWDG)和自动唤醒单元。时钟频率大约为 40 kHz(在 30 kHz 和 60 kHz 之间)。

3.7 系统时钟(SYSCLK)选择¶

系统复位后,HSI 振荡器被选择为系统时钟。当时钟源直接或通过 PLL 用作系统时钟时,无法停止它。

从一个时钟源切换到另一个时钟源,只有在目标时钟源准备就绪时才会发生(时钟在启动延迟后稳定或 PLL 锁定)。

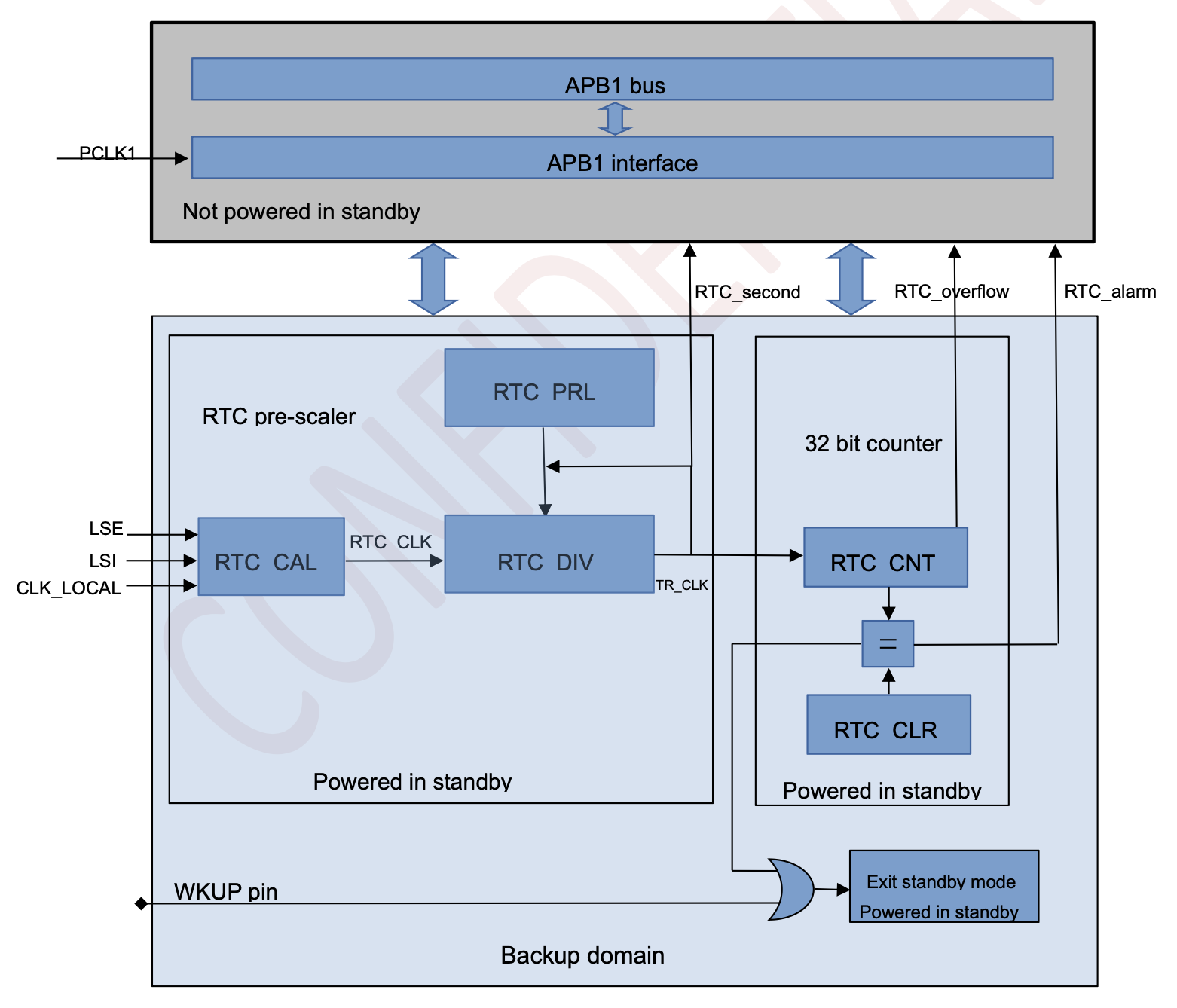

3.8 RTC 时钟¶

RTCCLK 时钟源可以是以下之一:CLKLOCAL(来自 FPGA 核心逻辑)、LSE 或 LSI 时钟。

通过在备份域控制寄存器(RCC_BDCR)中编程 RTCSEL[1:0] 位来选择时钟源。

此选择在没有重置备份域的情况下无法修改。

LSE 时钟位于备份域中,而 HSE 和 LSI 时钟不在备份域中。因此:

-

如果选择 LSE 作为 RTC 时钟:

即使 VDD 电源关闭,只要 VBAT 电源保持,RTC 仍然继续工作。

-

如果选择 LSI 作为自动唤醒单元(AWU)时钟:

如果 VDD 电源关闭,AWU 状态不保证。

-

如果选择 CLKLOCAL 作为 RTC 时钟:

如果 VDD 电源关闭或内部电压调节器关闭(移除 1.2V 域的电源),RTC 状态不保证。

在电源控制寄存器中,DPB 位(禁用备份域写保护)必须设置为 1。

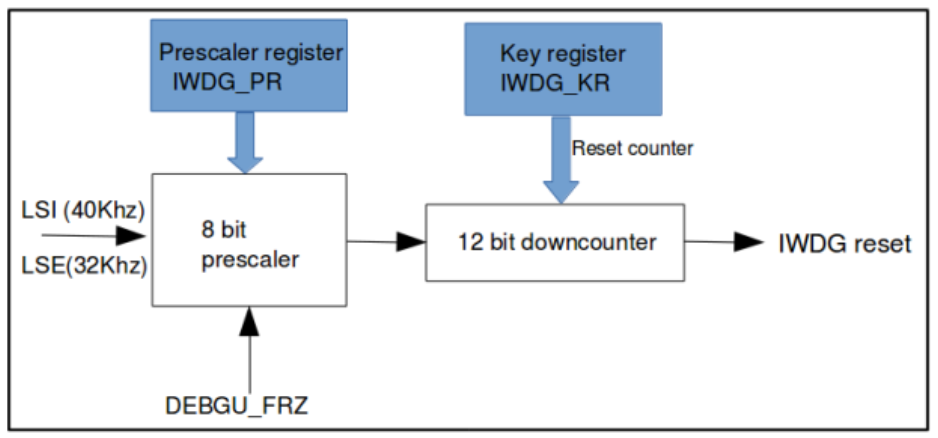

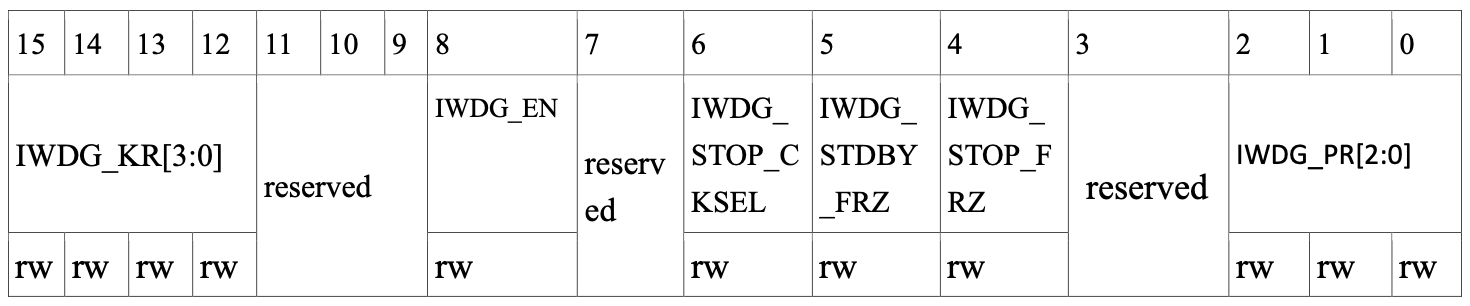

3.9 看门狗时钟¶

如果独立看门狗(IWDG)通过硬件选项或软件访问启动:

-

在运行模式或停止模式下:

通过在备份域控制寄存器(RCC_BDCR)中设置 IWDG_STOP_CLKSEL 位来选择 LSE 或 LSI 作为时钟源。

-

在待机模式下:

硬件将选择 LSE 作为 IWDG 的时钟源。

4 复位¶

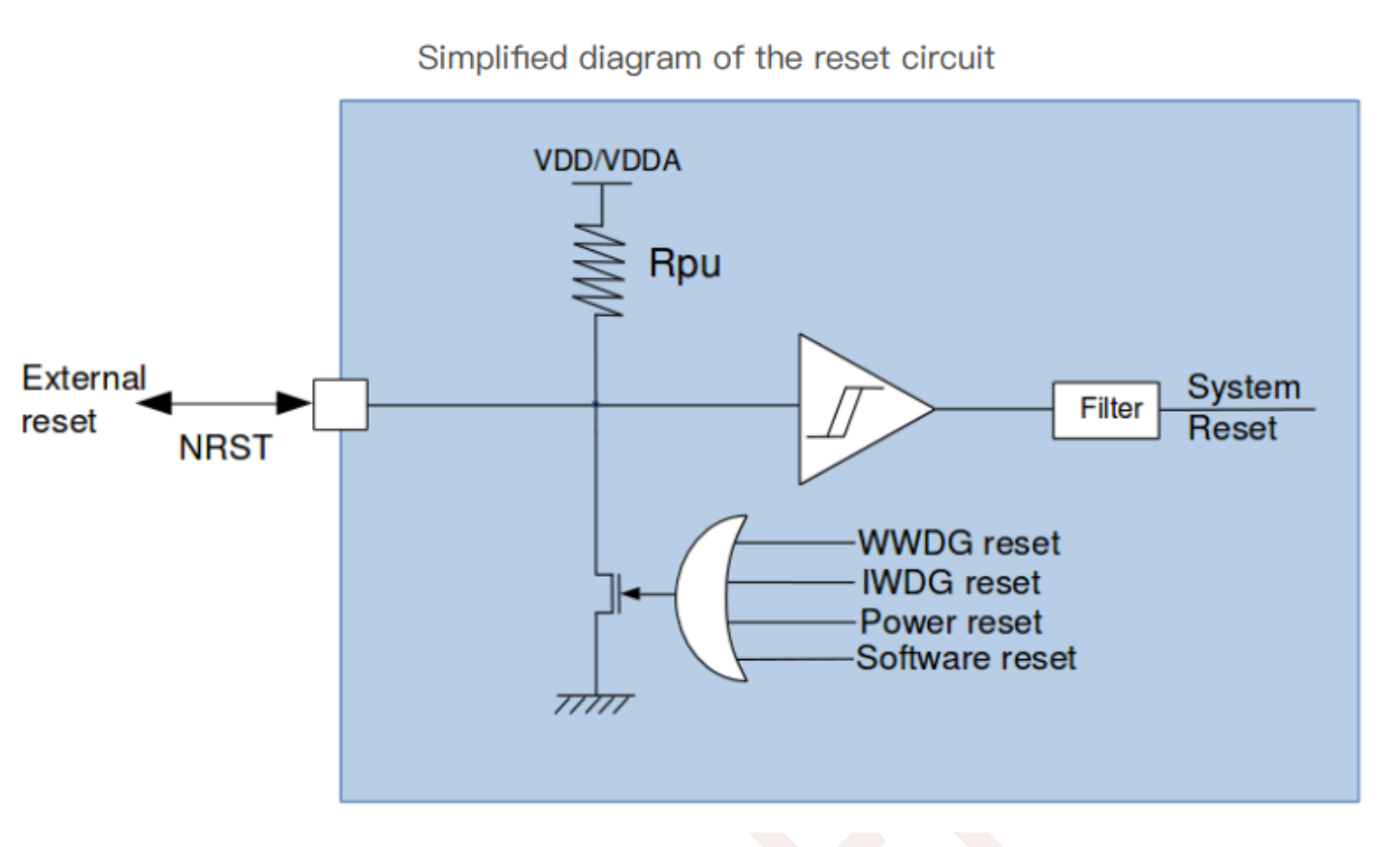

有三种类型的复位:系统复位、电源复位和备份域复位。

4.1 系统复位¶

当发生以下事件之一时,会生成系统复位:

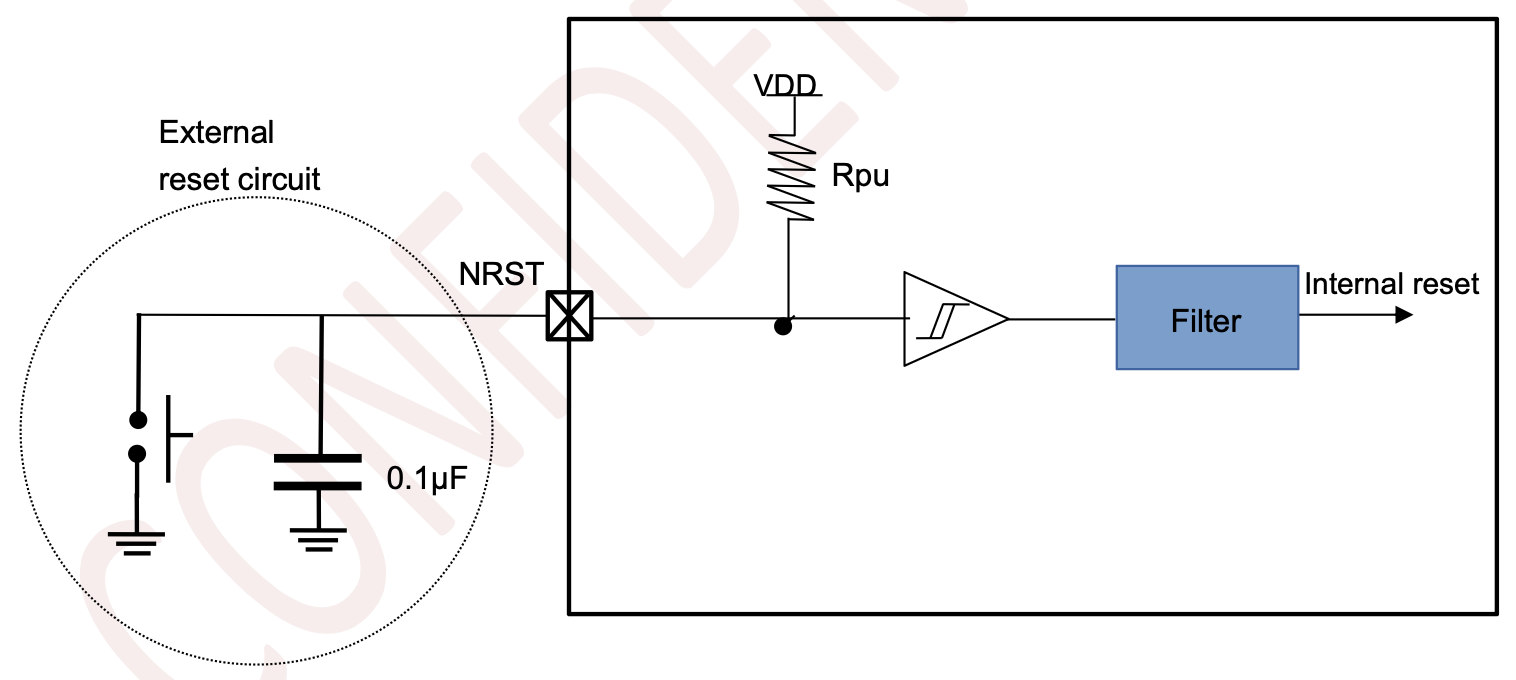

- NRST 引脚上的低电平(外部复位)

- 窗口看门狗计数结束条件(WWDG 复位)

- 独立看门狗计数结束条件(IWDG 复位)

- 软件复位(SW 复位)

- 低功耗管理复位

可以通过检查控制/状态寄存器(RCC_CSR)中的复位标志来识别复位源。

软件复位¶

必须在 MCU 应用程序中断和复位控制寄存器中的 SYSRESETREQ 位设置为 1,才能强制设备进行软件复位。

低功耗管理复位¶

有两种方式可以生成低功耗管理复位:

-

进入待机模式时生成复位:

通过重置用户选项字节中的 nRST_STDBY 位来启用此复位。在这种情况下,每当成功执行待机模式入口序列时,设备将复位,而不是进入待机模式。

-

进入停止模式时生成复位:

通过重置用户选项字节中的 nRST_STOP 位来启用此复位。在这种情况下,每当成功执行停止模式入口序列时,设备将复位,而不是进入停止模式。

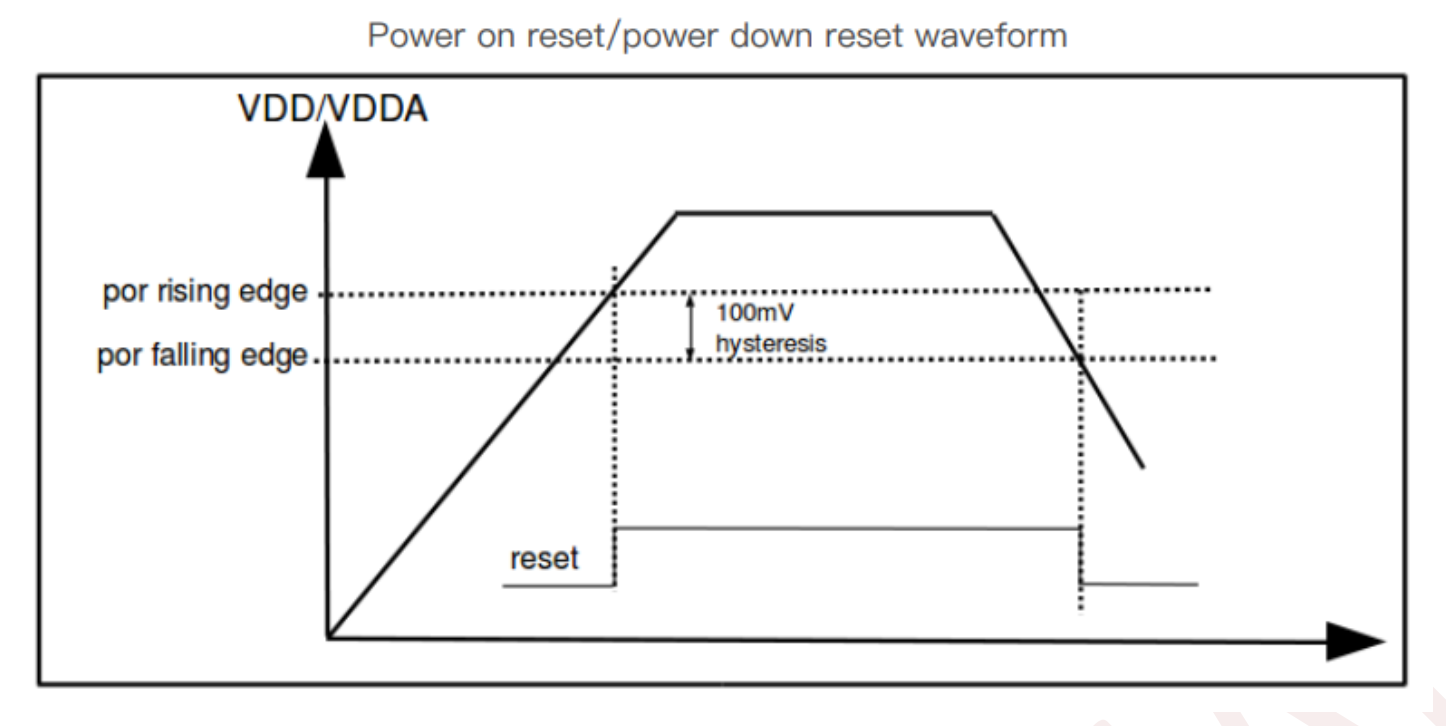

4.2 电源复位¶

当发生以下事件之一时,会生成电源复位:

- 上电/断电复位(POR/PDR 复位)

- 退出待机模式时

4.3 备份域复位¶

备份域有两个特定的复位,只影响备份域。

当发生以下事件之一时,会生成备份域复位:

- 软件复位。

- 如果 VDD33 或 VBAT 电源之前被断电,则在电源恢复时生成复位。

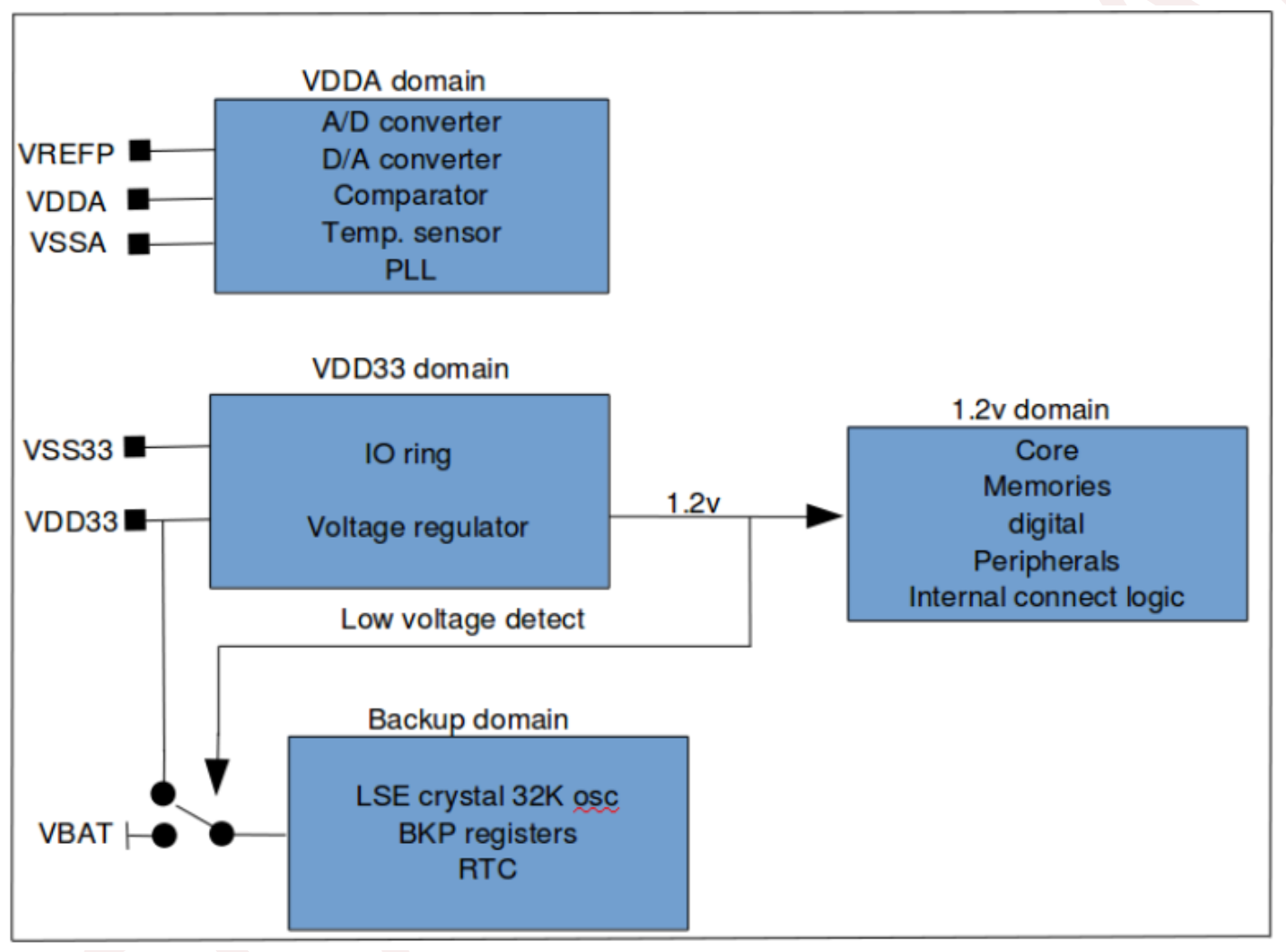

5 电源控制¶

5.1 电源供应¶

AG32VF 需要一个 3.135V 到 3.465V 的工作电压供应(VDD33)。使用嵌入式电压调节器为内部 1.2V 数字电源供电。当主 VDD33 电源断电时,实时时钟(RTC)和备份寄存器可以通过 VBAT 电压供电。

5.2 独立的 ADC 和 DAC 转换器供电及参考电压¶

为了提高转换精度,ADC 和 DAC 具有独立的电源,可以单独进行滤波并避免 PCB 上的噪声干扰。

- ADC 和 DAC 电压供应输入通过单独的 VDDA 引脚提供。

- 提供隔离的电源接地连接在 VSSA 引脚上。

为了确保在低电压输入和输出上的更高精度,用户可以将外部参考电压连接到 VREFP 引脚。

VREFP 是模拟输入(ADC)或输出(DAC)信号的最高电压,表示满刻度值。VREFP 上的电压范围为 3.135V 到 VDDA。

5.3 电池备份域¶

为了在 VDD33 断电时保持备份寄存器的内容并提供 RTC 功能,VBAT 引脚可以连接到由电池或其他来源提供的可选待机电压。

VBAT 引脚为 RTC 单元、LSE 振荡器以及 OSC32_IN 和 OSC32_OUT 引脚供电,使得 RTC 即使在主数字电源(VDD33)关闭时也能正常工作。

如果应用中未使用外部电池,建议将 VBAT 外部连接至 VDD33,并加装一个 100nF 外部陶瓷去耦电容器。

当备份域由 VDD33 供电时(模拟开关连接到 VDD33)。

5.4 电压调节器¶

电压调节器在复位后始终启用。根据应用模式,电压调节器有两种不同的工作模式。

- 在运行模式和停止模式下,调节器为 1.2V 域(核心、存储器、数字外设和互联逻辑)提供全功率。

- 在待机模式下,电压调节器关闭。除了待机电路和备份域外,寄存器和 SRAM 的内容将丢失。

5.5 上电复位(POR)/断电复位(PDR)¶

该设备具有集成的 POR/PDR 电路,允许设备从 2.2V 开始正常工作。当 VDD33/VDDA 低于指定的阈值 VPOR/PDR 时,设备将保持在复位模式,无需外部复位电路。

5.6 低功耗模式¶

默认情况下,微控制器在系统复位或电源复位后处于运行模式。当 CPU 不需要持续运行时,可以使用几种低功耗模式来节省电能。用户需要选择一种在低功耗消耗、短启动时间和可用唤醒源之间达到最佳平衡的模式。

AG32VF 设备具有三种低功耗模式:

- 睡眠模式(CPU 时钟关闭,所有外设,包括核心外设,保持运行)

- 停止模式(所有时钟停止)

- 待机模式(1.2V 域断电)

此外,可以通过以下方式之一减少运行模式下的功耗:

- 降低系统时钟速度。

- 在不使用时,将 APB 和 AHB 外设的时钟关闭。

5.6.1 降低系统时钟速度¶

在运行模式下,系统时钟的速度可以降低。同时,在进入睡眠模式之前,也可以降低外设的时钟速度。

5.6.2 外设时钟门控¶

在运行模式下,单个外设和存储器的时钟可以随时停止,以减少功耗。

为了在睡眠模式下进一步降低功耗,可以在执行 WFI 或 WFE 指令之前禁用外设时钟。

5.6.3 睡眠模式¶

进入睡眠模式¶

通过执行 WFI(等待中断)或 WFE(等待事件)指令进入睡眠模式。根据系统控制寄存器中的 SLEEPONEXIT 位,可以选择两种进入睡眠模式的机制:

- 立即睡眠:如果 SLEEPONEXIT 位被清除,微控制器在执行 WFI 或 WFE 指令后立即进入睡眠模式。

- 退出后睡眠:如果 SLEEPONEXIT 位被设置,微控制器在退出最低优先级的中断服务程序(ISR)后立即进入睡眠模式。

在睡眠模式下,所有 I/O 引脚保持与运行模式相同的状态。

退出睡眠模式¶

- 如果使用 WFI 指令进入睡眠模式,任何由嵌套矢量中断控制器(NVIC)确认的外设中断都可以唤醒设备。

-

如果使用 WFE 指令进入睡眠模式,微控制器在发生事件时退出睡眠模式。唤醒事件可以通过以下方式生成:

-

在外设控制寄存器中启用中断,但不在 NVIC 中启用,并在系统控制寄存器中启用 SEVONPEND 位。当微控制器从 WFE 恢复时,必须清除外设中断挂起位和外设 NVIC IRQ 通道挂起位(在 NVIC 中断清除挂起寄存器中)。

-

或者配置外部或内部 EXTI 线路为事件模式。当 CPU 从 WFE 恢复时,无需清除外设中断挂起位或 NVIC IRQ 通道挂起位,因为与事件线对应的挂起位没有被设置。此模式提供最低的唤醒时间,因为在中断进入/退出过程中不会浪费时间。

-

表 1. 立即睡眠模式(Sleep-now)

| 模式 | 描述 |

|---|---|

| 模式入口 | 使用 WFI(等待中断)或 WFE(等待事件),同时: – SLEEPDEEP = 0 和 – SLEEPONEXIT = 0 参考系统控制寄存器。 |

| 模式退出 | 如果使用 WFI 进入模式: 中断:参考:中断和异常向量。 如果使用 WFE 进入模式: 唤醒事件:参考:唤醒事件管理。 |

| 唤醒延迟 | 无 |

表 2. 退出后睡眠模式(Sleep-on-exit)

| 模式 | 描述 |

|---|---|

| 模式入口 | 使用 WFI(等待中断),同时: – SLEEPDEEP = 0 和 – SLEEPONEXIT = 1 参考系统控制寄存器。 |

| 模式退出 | 中断:参考:中断和异常向量。 |

| 唤醒延迟 | 无 |

5.6.4 停止模式(Stop mode)¶

停止模式基于 MCU 深度睡眠模式,并结合外设时钟门控。

在停止模式下,1.2V 域中的所有时钟都停止,PLL、HSI 和 HSE 振荡器被禁用。SRAM 和寄存器的内容被保留。

在停止模式下,所有 I/O 引脚保持与运行模式相同的状态。

进入停止模式¶

参考表 3,了解如何进入停止模式的详细信息。

如果闪存编程正在进行,进入停止模式会延迟,直到内存访问完成。

如果正在访问 APB 域,进入停止模式也会延迟,直到 APB 访问完成。

在停止模式下,可以通过编程单独的控制位来选择以下功能:

- 独立看门狗(IWDG):通过写入其使能寄存器或硬件选项启动 IWDG。一旦启动,除非复位,否则无法停止。

- 实时时钟(RTC):通过备份域控制寄存器中的 RTCEN 位进行配置。

- 外部 32.768 kHz 振荡器(LSE OSC):通过备份域控制寄存器中的 LSEON 位进行配置。

除非在进入停止模式之前将其禁用,否则 ADC 或 DAC 在停止模式下也可能会消耗功耗。

退出停止模式¶

参考表 3,了解如何退出停止模式的详细信息。

当通过中断或唤醒事件退出停止模式时,HSI RC 振荡器被选择为系统时钟。

表 3. 停止模式(Stop mode)

| 模式 | 描述 |

|---|---|

| 模式入口 | 使用 WFI(等待中断)或 WFE(等待事件),同时: – 在系统控制寄存器中设置 SLEEPDEEP 位 – 在电源控制寄存器(PWR_CR)中清除 PDDS 位。 注意:为了进入停止模式,所有 EXTI 线路挂起位(在挂起寄存器(EXTI_PR)中)、所有外设中断挂起位和 RTC 闹钟标志必须被重置。否则,停止模式入口过程会被忽略,程序执行将继续。 |

| 模式退出 | 如果使用 WFI 进入模式: 任何配置为中断模式的 EXTI 线路(对应的 EXTI 中断向量必须在 NVIC 中启用)。 参考:中断和异常向量。 如果使用 WFE 进入模式: 任何配置为事件模式的 EXTI 线路。 参考:唤醒事件管理。 |

| 唤醒延迟 | HSI RC 唤醒时间 |

5.6.5 待机模式(Standby mode)¶

待机模式允许实现最低的功耗。它基于深度睡眠模式,并且禁用了电压调节器。因此,1.2V 域断电,PLL、HSI 振荡器和 HSE 振荡器也被关闭。除备份域中的寄存器和待机电路外,SRAM 和寄存器内容丢失。

进入待机模式¶

参考表 4,了解如何进入待机模式的详细信息。

在待机模式下,可以通过编程单独的控制位来选择以下功能:

- 独立看门狗(IWDG):通过写入其使能寄存器或硬件选项启动 IWDG。一旦启动,除非复位,否则无法停止。

- 实时时钟(RTC):通过备份域控制寄存器中的 RTCEN 位进行配置。

- 外部 32.768 kHz 振荡器(LSE OSC):通过备份域控制寄存器中的 LSEON 位进行配置。

退出待机模式¶

微控制器在以下事件发生时退出待机模式:

- 外部复位(NRST 引脚)

- IWDG 复位

- WKUP 引脚上的上升沿或下降沿

- RTC 闹钟的上升沿

从待机模式唤醒后,所有寄存器将被复位。

唤醒后,程序执行将以与复位后的方式相同的方式重新启动。

电源控制/状态寄存器(PWR_CSR)中的 SBF 状态标志指示 MCU 曾处于待机模式。

参考表 4,了解如何退出待机模式的详细信息。

表 4. 待机模式(Standby mode)

| 模式 | 描述 |

|---|---|

| 模式入口 | 使用 WFI(等待中断)或 WFE(等待事件),同时: – 在系统控制寄存器中设置 SLEEPDEEP 位 – 在电源控制寄存器(PWR_CR)中设置 PDDS 位 – 在电源控制/状态寄存器(PWR_CSR)中清除 WUF 位 – 没有中断(对于 WFI)或事件(对于 WFE)挂起 |

| 模式退出 | WKUP 引脚的上升沿,RTC 闹钟事件的上升沿,外部复位(NRST 引脚),IWDG 复位 |

| 唤醒延迟 | 复位阶段 |

待机模式中的 I/O 状态¶

在待机模式下,除以下引脚外,所有 I/O 引脚都是高阻态:

- 复位引脚(仍然可用)

- CLKRTCOUT 引脚(如果配置为校准输出)

- WKUP 引脚(如果启用)

5.6.6 低功耗模式下的自动唤醒(AWU)¶

RTC 可用于在无需依赖外部中断的情况下从低功耗模式唤醒 MCU(自动唤醒模式)。RTC 提供了一个可编程的时间基准,用于在固定间隔后从停止模式或待机模式唤醒。为此,可以通过编程备份域控制寄存器(RCC_BDCR)中的 RTCSEL[1:0] 位,选择三种备用 RTC 时钟源中的两种:

-

低功耗 32.768 kHz 外部晶体振荡器(LSE OSC)

该时钟源提供精确的时间基准,并具有非常低的功耗。

-

低功耗内部 RC 振荡器(LSI RC)

该时钟源的优势在于节省了 32.768 kHz 晶体的成本。

6 中断控制器¶

AG32 设备嵌入了一个嵌套矢量中断控制器(NVIC),能够管理 16 个优先级级别,并处理最多 44 个可屏蔽的中断通道以及 RISC-V 核心的 16 个中断线路。

6.1 本地中断¶

4 个本地中断(LOCAL_INT0-3)直接连接到核心,并具有较低的延迟。它们具有固定的优先级。

6.2 外部中断¶

外部中断通过平台级中断控制器(PLIC)进行路由。它们具有可编程的优先级和阈值。中断号如下所示:

| 中断名称 | 中断编号 | 备注 |

|---|---|---|

| FLASH | 1 | |

| RTC | 2 | |

| FCB0 | 3 | |

| WATCHDOG0 | 4 | |

| SPI0 | 5 | |

| SPI1 | 6 | |

| GPIO0 | 7 | |

| GPIO1 | 8 | |

| GPIO2 | 9 | |

| GPIO3 | 10 | |

| GPIO4 | 11 | |

| GPIO5 | 12 | |

| GPIO6 | 13 | |

| GPIO7 | 14 | |

| GPIO8 | 15 | |

| GPIO9 | 16 | |

| TIMER0 | 17 | |

| TIMER1 | 18 | |

| GPTIMER0 | 19 | |

| GPTIMER1 | 20 | |

| GPTIMER2 | 21 | |

| GPTIMER3 | 22 | |

| GPTIMER4 | 23 | |

| UART0 | 24 | |

| UART1 | 25 | |

| UART2 | 26 | |

| UART3 | 27 | |

| UART4 | 28 | |

| CAN0 | 29 | |

| I2C0 | 30 | |

| I2C1 | 31 | |

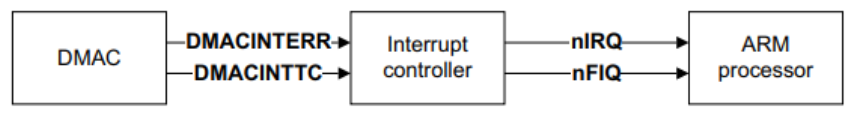

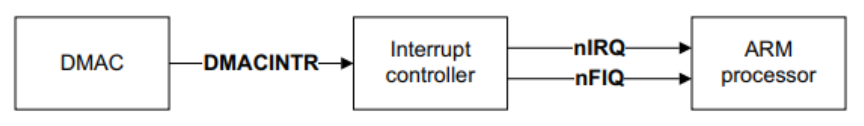

| DMAC0_INTR | 32 | DMA 合并中断 |

| DMAC0_INTTC | 33 | DMA 终端计数中断 |

| DMAC0_INTERR | 34 | DMA 错误中断 |

| USB0 | 35 | |

| MAC0 | 36 | |

| EXT_INT0 | 37 | |

| EXT_INT1 | 38 | |

| EXT_INT2 | 39 | |

| EXT_INT3 | 40 | |

| EXT_INT4 | 41 | |

| EXT_INT5 | 42 | |

| EXT_INT6 | 43 | |

| EXT_INT7 | 44 |

6.3 总体优先级¶

从最高优先级到最低优先级:

- LOCAL_INT3

- LOCAL_INT2

- LOCAL_INT1

- LOCAL_INT0

- 来自 PLIC 的外部中断

- 机器软件中断

- 机器定时器中断

6.4 中断使能¶

- 必须设置 RISC-V 机器状态寄存器(mstatus)中的机器中断使能(MIE)位,作为所有中断的全局使能。

-

必须为每种类型的中断设置 RISC-V 机器中断使能寄存器(mie)中的相应位,以使中断生效:

- MEIE 位:用于外部中断。

- MSIE 位:用于机器软件中断。

- MTIE 位:用于机器定时器中断。

- 位 16-19:分别用于 LOCAL_INT0-3 中断。

6.5 中断寄存器¶

-

机器软件中断挂起(MSIP)

- 地址:0x2000000

-

位 0:

- 写入 1 以触发机器软件中断

- 写入 0 以清除挂起状态

-

机器定时器比较低(MTIMECMP_LO)

- 地址:0x2004000

- 位 [31:0]:机器定时器比较寄存器的低 32 位

-

机器定时器比较高(MTIMECMP_HI)

- 地址:0x2004004

- 位 [31:0]:机器定时器比较寄存器的高 32 位

-

机器定时器低(MTIME_LO)

- 地址:0x200bFF8

- 位 [31:0]:机器定时器寄存器的低 32 位

-

机器定时器高(MTIME_HI)

- 地址:0x200bFFC

- 位 [31:0]:机器定时器寄存器的高 32 位

-

外部中断优先级(PRIORITY)

- 地址:0xC000000 + (中断号 * 4)

- 每个优先级寄存器存储对应中断的优先级级别

- 有效的优先级范围从 0(最低,禁用中断)到 15(最高)

-

外部中断挂起(PENDING)

- 地址:0xC001000

- 每个中断有 1 位挂起状态。位偏移由中断号决定。

- 当对应的中断触发时,硬件会自动设置该位,并在对应中断具有最高优先级时,通过读取 CLAIM_COMPLETE 寄存器自动清除该位。

-

外部中断使能(ENABLE)

- 地址:0xC002000

- 每个中断有 1 位使能。位偏移由中断号决定。

- 每个位可以由软件设置或清除。

-

外部中断阈值(THRESHOLD)

- 地址:0xC200000

- 位 [3:0]:由软件设置,用于确定外部中断阈值。只有优先级高于阈值的外部中断才会触发中断到 CPU 核心。

-

外部中断声明与完成(CLAIM_COMPLETE)

- 地址:0xC200004

- 读取该寄存器会返回具有最高优先级的挂起中断号,并清除对应的挂起位(仅对于使能且优先级高于阈值的中断)。由于中断从 1 开始编号,读取值为 0 表示没有活动中断。写入该寄存器将完成中断,并使写入的中断号准备好再次响应。

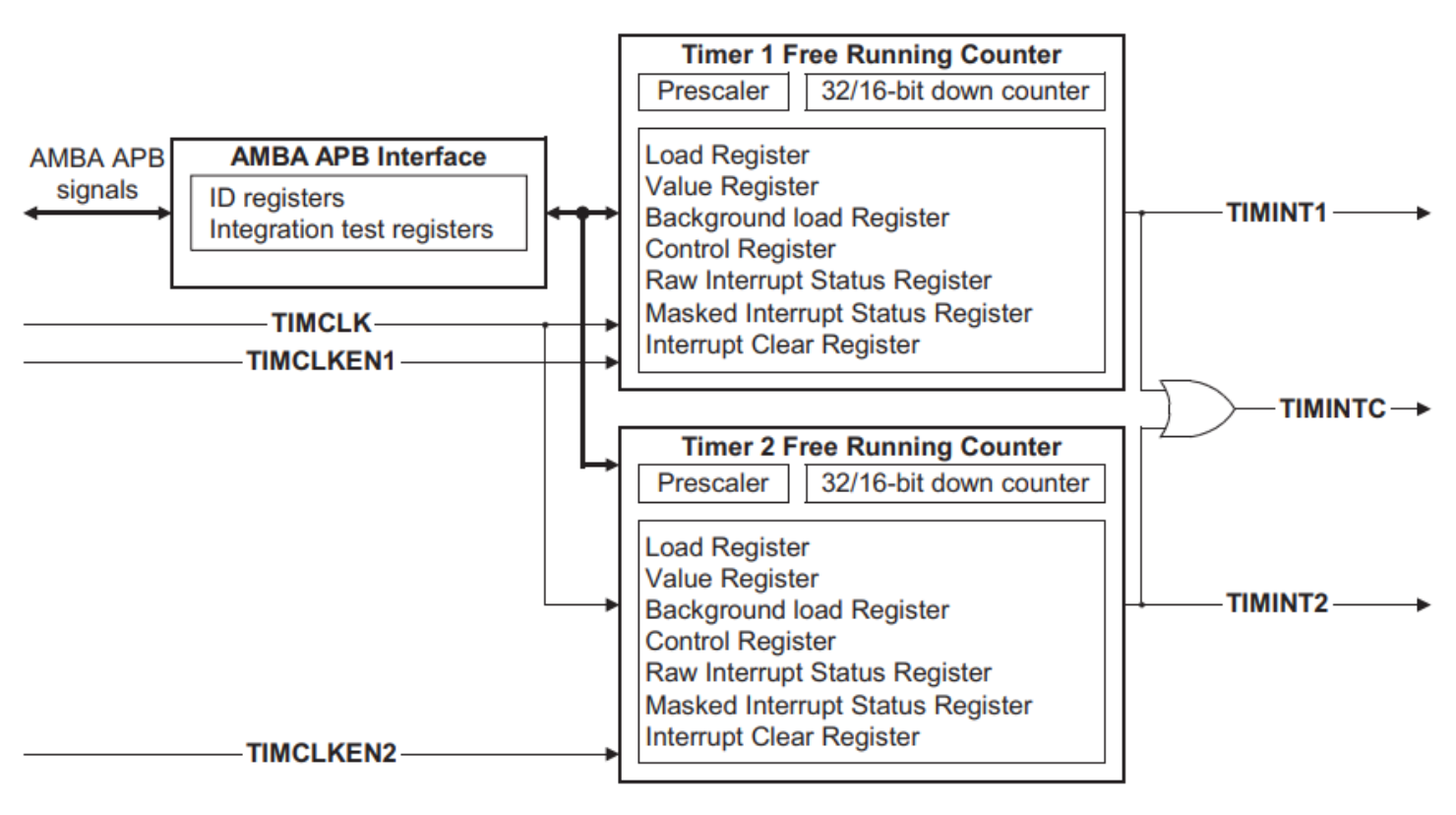

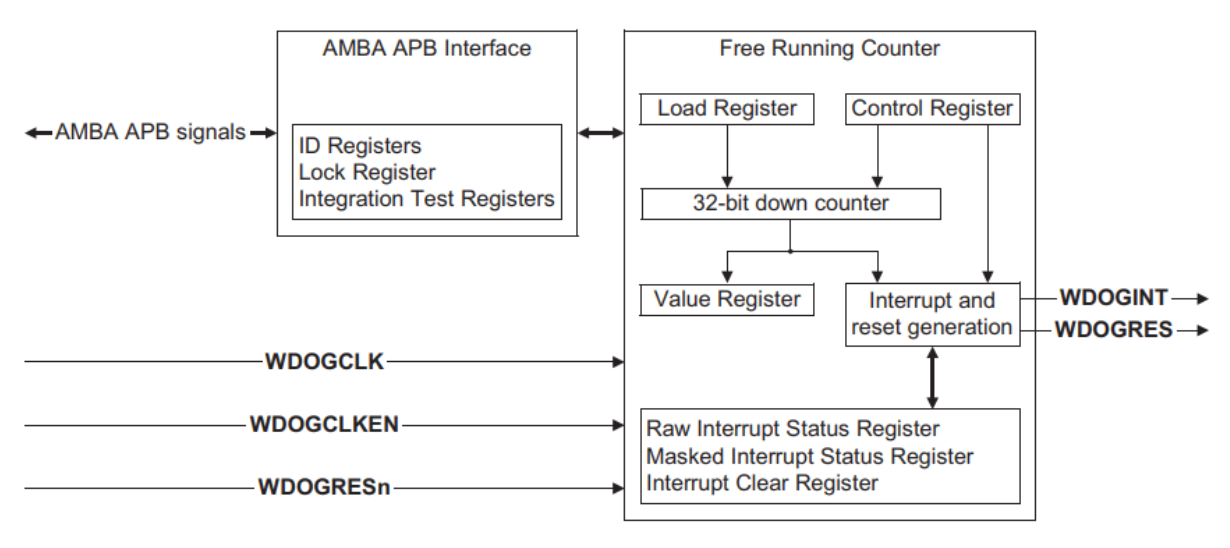

7 双定时器(基本定时器)¶

7.1 介绍¶

双定时器模块由两个可编程的 32 位/16 位向下计数器组成,这些计数器在达到零时可以生成中断。

- 两个 32 位/16 位向下计数器,支持自由运行、周期性和单次模式。

- 共享时钟,并且每个定时器有独立的时钟使能,提供灵活的定时器间隔控制。

- 在定时器计数到零时生成中断输出。

- 唯一标识双定时器模块的标识寄存器,软件可以使用这些寄存器来自动配置自身。

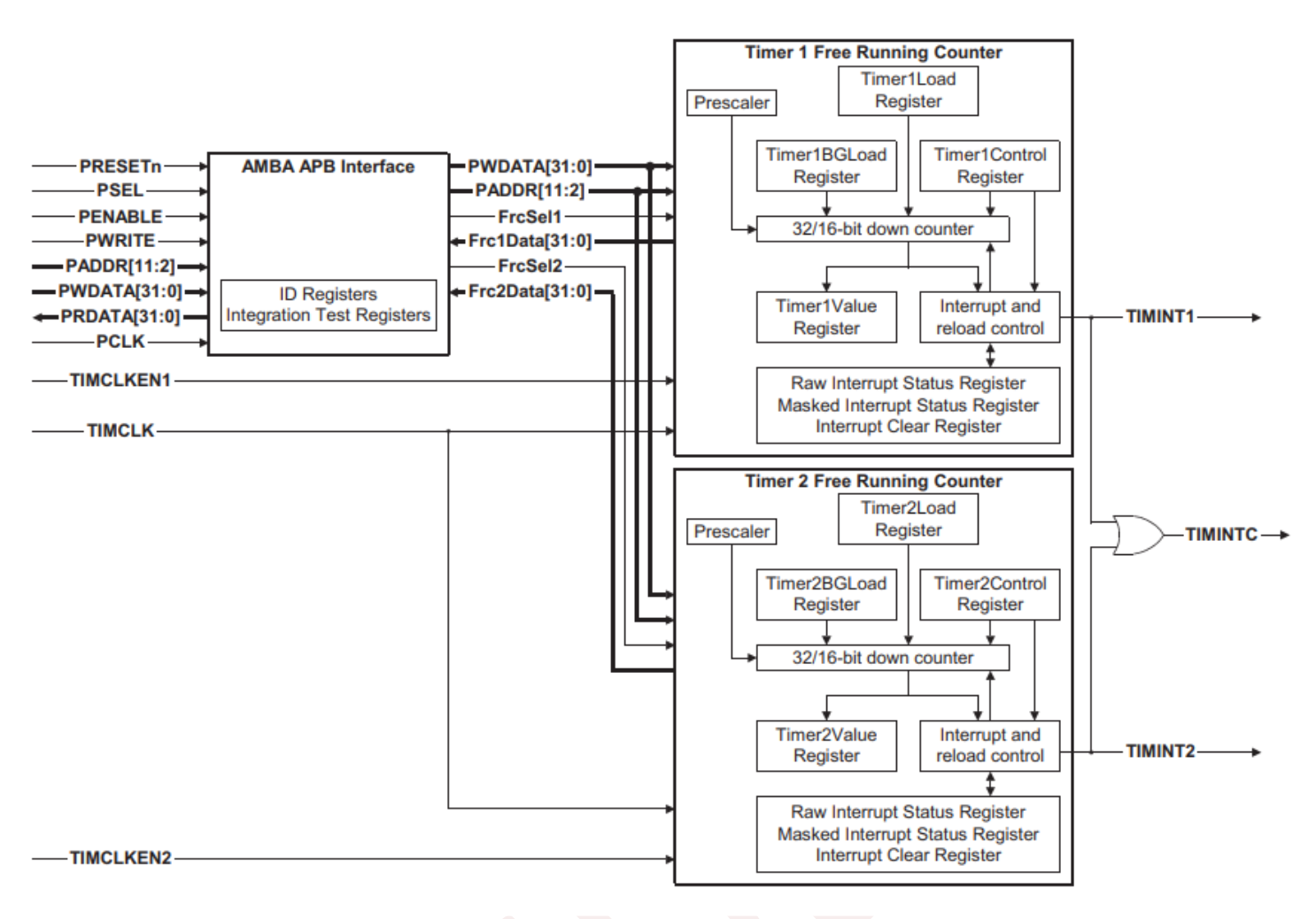

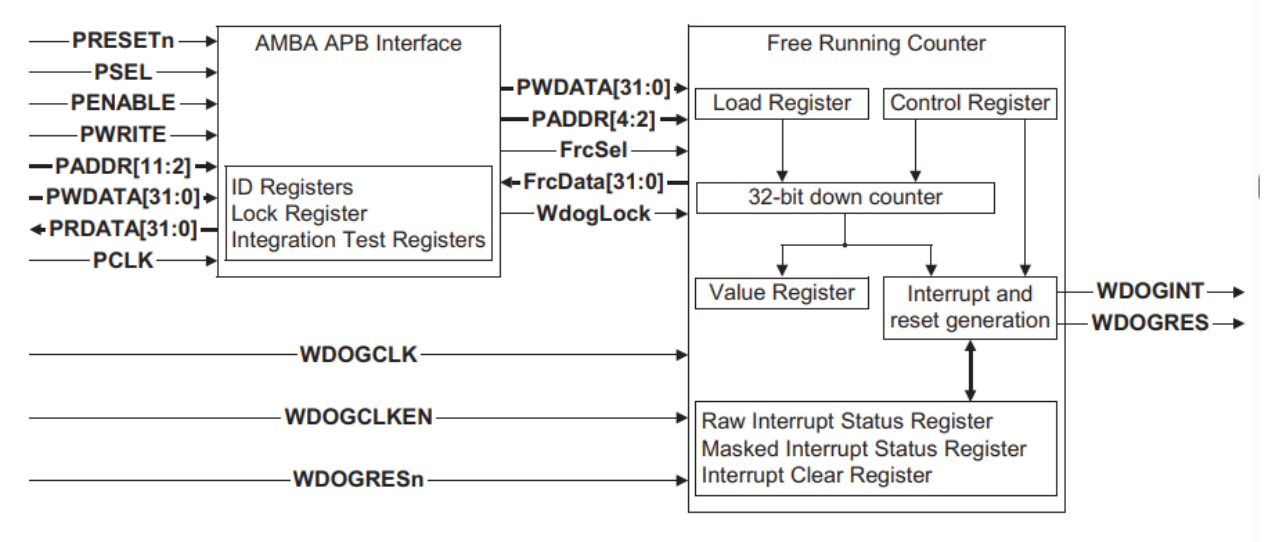

下图显示了该模块的简化框图。

7.2 功能概述¶

7.2.1 概述¶

双定时器模块由两个相同的可编程自由运行计数器(FRC)组成,这些计数器可以配置为 32 位或 16 位操作,并支持三种定时器模式之一:

- 自由运行模式

- 周期性模式

- 单次模式

FRCs 共享一个公共定时器时钟 TIMCLK,每个 FRC 拥有自己的时钟使能输入 TIMCLKEN1 和 TIMCLKEN2。每个 FRC 还具有一个预分频器,可以将启用的 TIMCLK 时钟频率分频为 1、16 或 256,从而使每个 FRC 的计数速率可以通过其独立的时钟使能和预分频器来独立控制。

TIMCLK 可以等于或是 PCLK 频率的子倍频。然而,TIMCLK 和 PCLK 的正向沿必须是同步和平衡的。

每个定时器模块的操作是相同的。通过控制寄存器,可以将定时器模块编程为 32 位或 16 位计数器大小,并选择三种定时器模式之一。这三种模式为:

- 自由运行模式:计数器连续运行,每当计数器达到零时,它会回绕至其最大值。

- 周期性模式:计数器连续运行,每当计数器达到零时,从加载寄存器重新加载值。

- 单次模式:通过写入加载寄存器,计数器加载新值,计数器递减到零后停止,直到重新编程。

定时器计数通过写入加载寄存器进行加载,并且如果启用了定时器,计数器将按照由 TIMCLK、TIMCLKENX 和预分频器设置确定的速率递减。当定时器计数已经在运行时,写入加载寄存器将使计数器立即从新值重新启动。

加载定时器计数的另一种方式是通过写入后台加载寄存器。这不会立即影响当前计数,但计数器会继续递减。当计数器达到零时,如果处于周期性模式,定时器计数将从新加载值重新加载。

当定时器计数达到零时,会生成中断。通过写入中断清除寄存器可以清除该中断。外部中断信号可以通过中断屏蔽寄存器进行屏蔽。

当前计数器值可以随时从 值寄存器 读取。

7.2.2 功能描述¶

双定时器模块的框图如下所示。

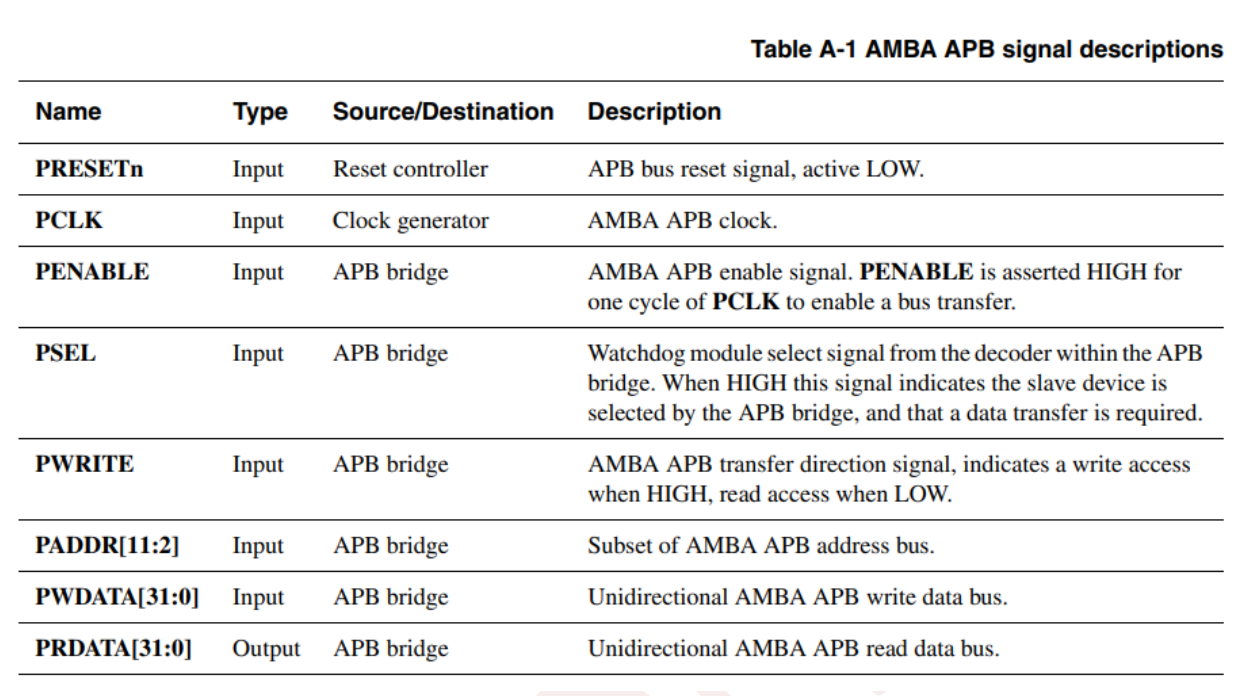

7.2.2.1 AMBA APB 接口¶

AMBA APB 从接口为双定时器模块中的所有寄存器的访问生成读写解码。

7.2.2.2 自由运行计数器块¶

这两个 FRC 是相同的,并包含 32 位/16 位向下计数器和中断功能。计数器逻辑由 TIMCLK 时钟驱动,并且独立于 PCLK 工作,同时配合时钟使能 TIMCLKENX,尽管 PCLK 和 TIMCLK 之间存在约束。

虽然两个 FRC 都由共享时钟 TIMCLK 驱动,但每个定时器的计数速率可以通过各自的时钟使能 TIMCLKEN1 和 TIMCLKEN2 独立控制。每个 FRC 中的预分频器进一步独立地控制每个 FRC 的计数速率。

7.2.2.3 接口复位¶

双定时器模块由全局复位信号 PRESETn 复位。

PRESETn 可以异步于 PCLK 触发,但必须与 PCLK 的上升沿同步释放。PRESETn 用于重置双定时器模块寄存器的状态。双定时器模块要求 PRESETn 至少在 PCLK 的一个周期内保持低电平。总之,定时器在复位后初始化为以下状态:

- 计数器被禁用

- 选择自由运行模式

- 选择 16 位计数器模式

- 预分频器设置为 1

- 中断被清除但仍然使能

- 加载寄存器设置为零

- 计数器值设置为 0xFFFFFFFF

7.2.2.4 时钟信号和时钟使能¶

双定时器模块使用两个输入时钟:

- PCLK 用于计时所有对双定时器模块寄存器的 APB 访问。

- TIMCLK 通过时钟使能 TIMCLKEN1 和 TIMCLKEN2 进行有效性验证,并用于驱动预分频器、计数器及其相关的中断逻辑。此有效的 TIMCLK 时钟频率称为实际定时器时钟频率。预分频器计数器仅在 TIMCLKENX 为高时,在 TIMCLK 的上升沿递减。定时器计数器仅在 TIMCLKENX 为高且预分频器计数器生成使能时,才在 TIMCLK 的上升沿递减。

TIMCLK 和 PCLK 之间的关系必须满足以下约束:

- TIMCLK 的上升沿必须与 PCLK 的上升沿同步和平衡。

- TIMCLK 的频率不能大于 PCLK 的频率。

TIMCLK、TIMCLKEN1 和 TIMCLKEN2 可以按以下方式使用:

- TIMCLK 等于 PCLK 且 TIMCLKENX 等于 1

- TIMCLK 等于 PCLK 且 TIMCLKENX 为脉冲信号

- TIMCLK 小于 PCLK 且 TIMCLKENX 等于 1

- TIMCLK 小于 PCLK 且 TIMCLKENX 为脉冲信号

注:除非另有说明,这些示例使用的预分频设置为分频 1。这些示例适用于模块中的 Timer1 或 Timer2。TIMCLKENX 指代 TIMCLKEN1 或 TIMCLKEN2。

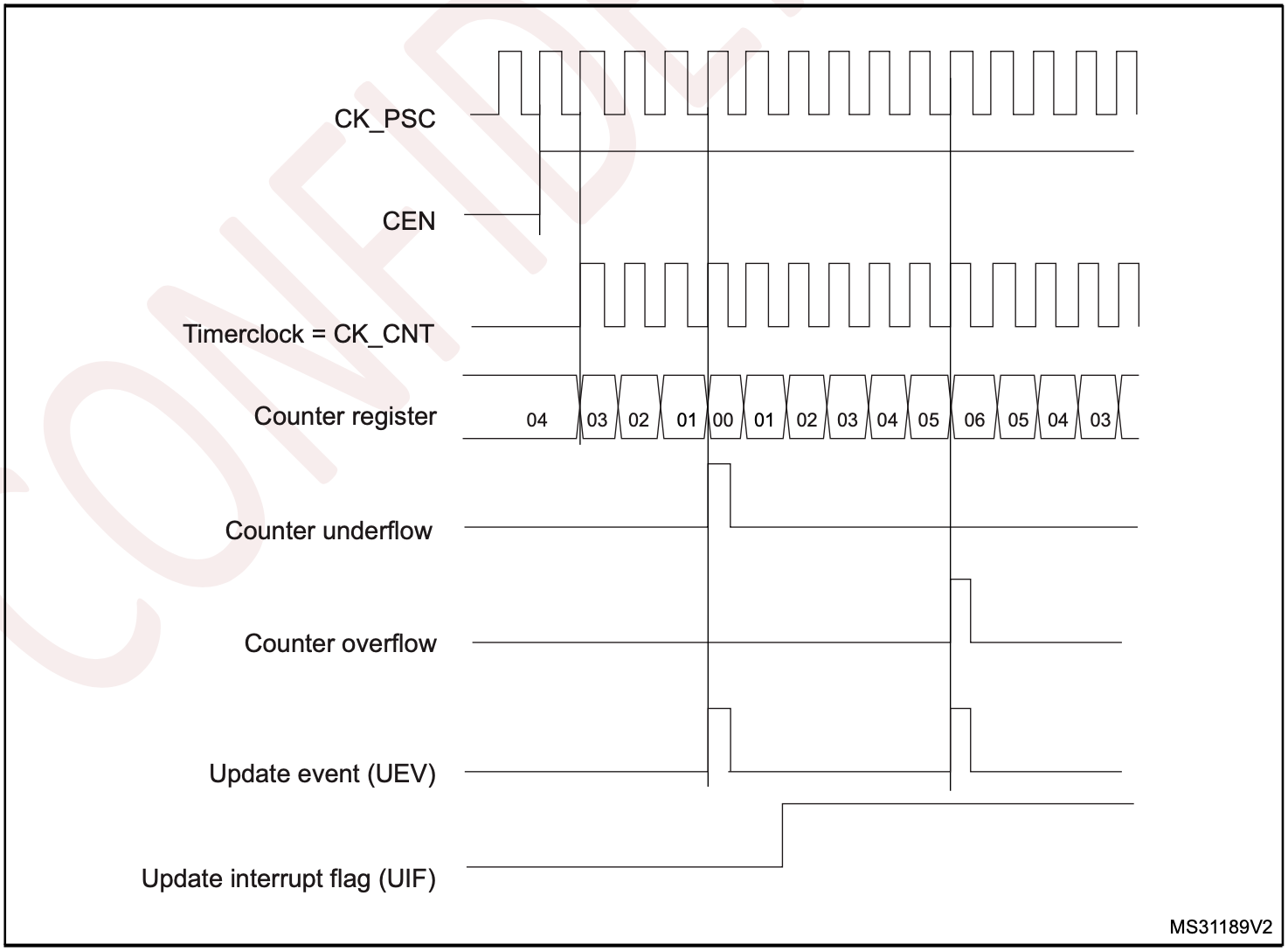

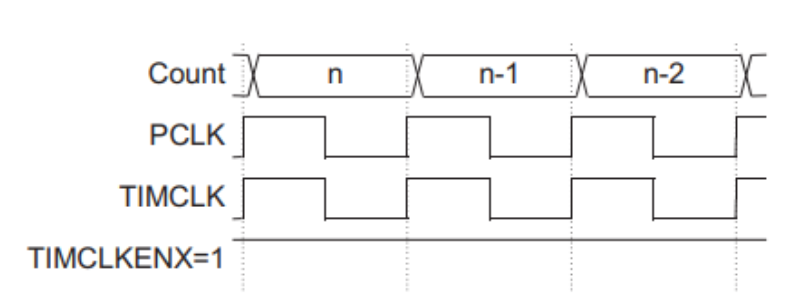

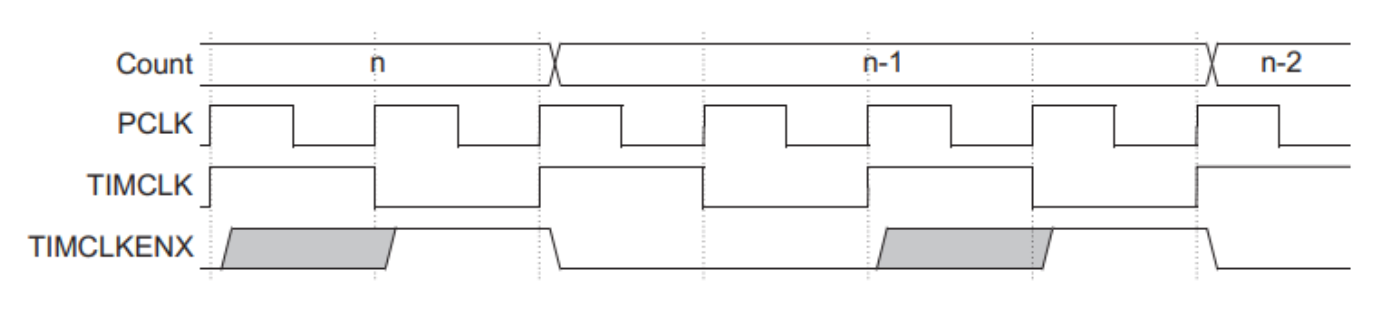

TIMCLK 等于 PCLK 且 TIMCLKENX 等于 1

下图展示了 TIMCLK 与 PCLK 相同且 TIMCLKENX 始终使能的情况。在这种情况下,计数器会在每个 TIMCLK 上升沿递减。

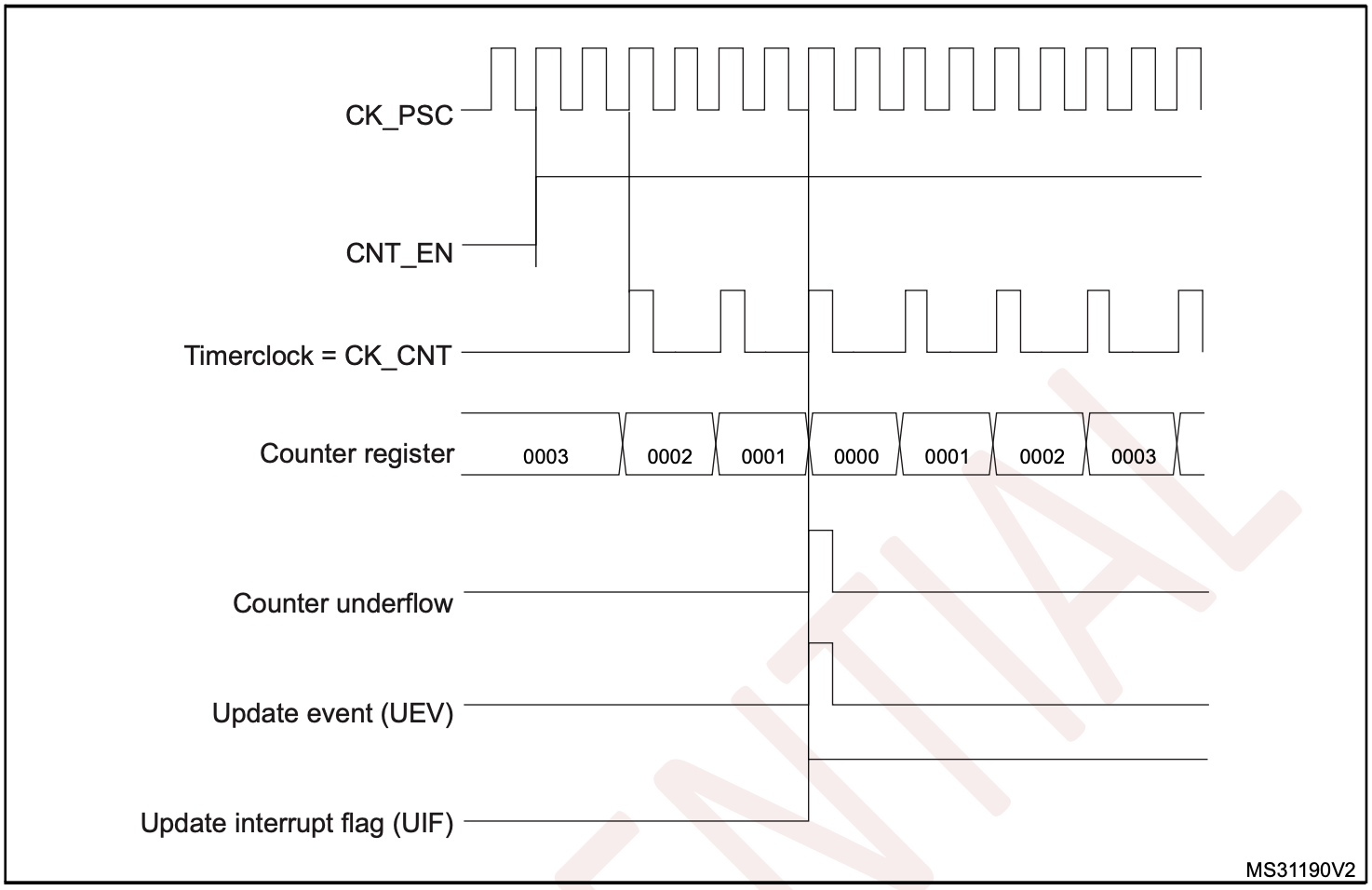

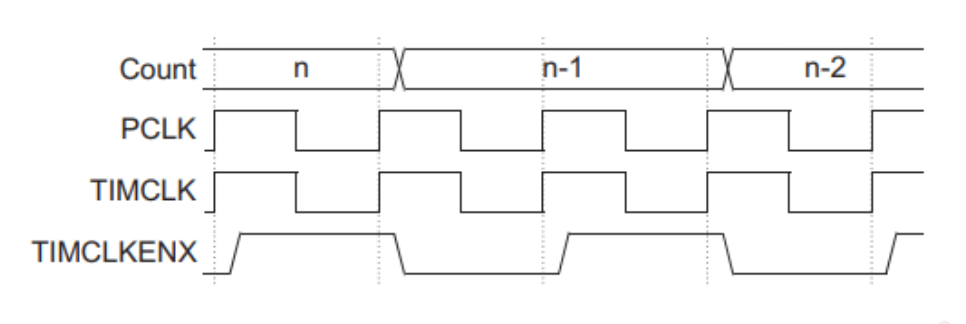

TIMCLK 等于 PCLK 且 TIMCLKENX 为脉冲信号

下图展示了 TIMCLK 与 PCLK 相同,但 TIMCLKENX 仅在每两个 TIMCLK 上升沿时使能的情况。在这种情况下,计数器会在每两个 TIMCLK 上升沿中的第二个递减。

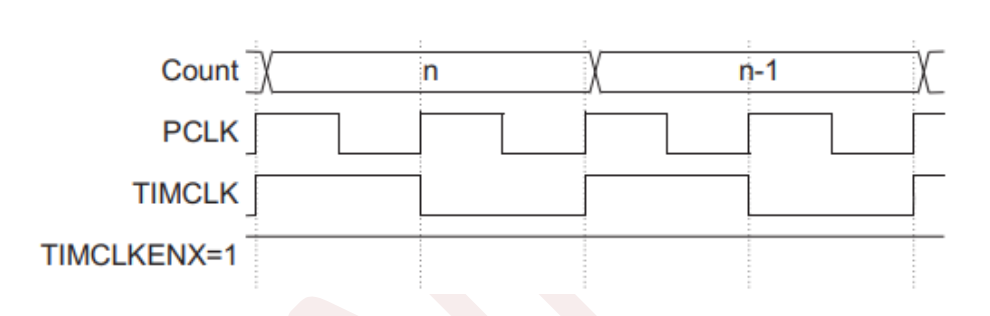

TIMCLK 小于 PCLK 且 TIMCLKENX 等于 1

下图展示了 TIMCLK 的频率是 PCLK 频率的子倍数,但 TIMCLK 的上升沿与 PCLK 的上升沿是同步且平衡的情况。TIMCLKENX 始终使能。在这种情况下,计数器会在每个 TIMCLK 上升沿递减。

TIMCLK 小于 PCLK 且 TIMCLKENX 为脉冲信号

下图展示了 TIMCLK 的频率是 PCLK 频率的子倍数,但 TIMCLK 的上升沿与 PCLK 的上升沿是同步且平衡的情况。TIMCLKENX 仅在每两个 TIMCLK 上升沿时使能。在这种情况下,计数器会在每两个 TIMCLK 上升沿中的第二个递减。

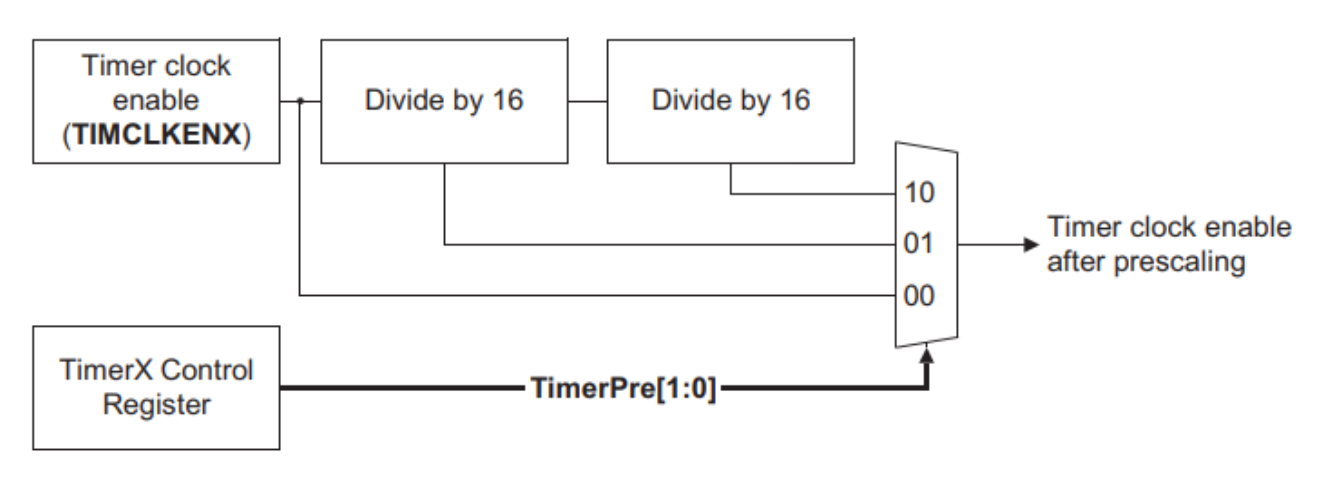

7.2.2.5 预分频器操作¶

预分频器生成一个定时器时钟使能,用于以以下速率启用定时器计数器的递减:

- 有效的定时器时钟速率,其中 TIMCLK 通过 TIMCLKENX 进行有效性验证

- 有效的定时器时钟速率除以 16

- 有效的定时器时钟速率除以 256

下图展示了预分频器如何生成定时器时钟使能。

下图展示了预分频器如何生成定时器时钟使能,假设预分频器设置为分频 16 的情况。

7.2.2.6 定时器操作¶

在初始应用和 PRESETn 释放之后,定时器状态初始化如下:

- 计数器被禁用,TimerEn=0

- 选择自由运行模式,TimerMode=0 且 OneShot=0

- 选择 16 位计数器模式,TimerSize=0

- 预分频器设置为分频 1,TimerPre=0x0

- 中断被清除但已使能,IntEnable=1

- 加载寄存器设置为零

- 计数器值设置为 0xFFFFFFFF

三种定时器模式中的每种操作描述如下:

- 自由运行模式

- 周期性模式

- 单次模式

自由运行模式¶

自由运行模式通过在 TimerControl Register 中设置以下位来选择:

- 设置 TimerMode 位为 1

- 设置 OneShot 位为 0

32 位或 16 位计数器操作通过在 TimerControl Register 中适当设置 TimerSize 位来选择。

在复位时,定时器值初始化为 0xFFFFFFFF,如果计数器已启用,则计数器会在每个 TIMCLK 正向沿时递减,前提是 TIMCLKENX 为高且预分频器生成使能脉冲。或者,可以通过写入 TimerXLoad Register 来加载新的初始计数器值,若计数器已启用,计数器将从该值开始递减。

在 32 位模式下,当计数器值达到零(0x00000000)时,会生成一个中断,计数器无论 TimerXLoad Register 中的值如何都会回绕到 0xFFFFFFFF。计数器重新开始递减,整个周期会一直重复,直到计数器被禁用。

在 16 位模式下,只有计数器的最低有效 16 位会递减,当计数值达到 0x0000 时,会生成一个中断,计数器无论 TimerXLoad Register 中的值如何都会回绕到 0xFFFF。

如果通过清除 TimerEn 位来禁用计数器,则计数器会停止并保持当前值。如果计数器重新启用,则计数器将从当前值继续递减。

计数器值可以通过读取 TimerXValue Register 在任何时间被读取。

周期性模式¶

周期性模式通过在 TimerControl Register 中设置以下位来选择:

- 设置 TimerMode 位为 0

- 设置 OneShot 位为 0

32 位或 16 位计数器操作通过在 TimerControl Register 中适当设置 TimerSize 位来选择。

可以通过写入 TimerXLoad Register 来加载初始计数器值,如果计数器已启用,则计数器将从该值开始递减。

在 32 位模式下,计数器的全部 32 位都会递减,当计数器值达到零(0x00000000)时,会生成一个中断,计数器会用 TimerXLoad Register 中的值重新加载。计数器重新开始递减,整个周期会一直重复,直到计数器被禁用。

在 16 位模式下,只有计数器的最低有效 16 位会递减,当计数器值达到 0x0000 时,会生成一个中断,计数器会用 TimerXLoad Register 中的值重新加载。计数器重新开始递减,整个周期会一直重复,直到计数器被禁用。

如果计数器在运行时通过写入 TimerXLoad Register 加载了一个新值,则计数器将在下一个 TIMCLK 上升沿(当 TIMCLKENX 为高时)切换到新加载的值。

如果计数器在运行时通过写入后台加载寄存器 TimerXBGLoad 加载了一个新值,则 TimerXLoad Register 也会更新为相同的加载值,但计数器会继续递减至零。当计数器达到零时,它会用新加载的值重新加载,并且在周期性模式下每次重新加载时都使用这个新加载值,直到定时器被禁用。

如果通过清除 TimerEn 位来禁用计数器,则计数器会停止并保持当前值。如果计数器重新启用,则计数器将从当前值继续递减。

单次模式¶

单次定时器模式通过在 TimerControl Register 中将 OneShot 位设置为 1 来选择。在单次模式下,TimerMode 位没有作用。

32 位或 16 位计数器操作通过在 TimerControl Register 中适当设置 TimerSize 位来选择。

要在单次模式下启动计数倒计时序列,可以向 TimerXLoad Register 写入新的加载值,如果计数器已启用,则计数器将从该值开始递减。

在 32 位模式下,计数器的全部 32 位都会递减,当计数器值达到零(0x00000000)时,会生成一个中断,计数器停止。

在 16 位模式下,只有计数器的最低有效 16 位会递减,当计数器值达到 0x0000 时,会生成一个中断,计数器停止。

单次模式可以通过向 TimerXLoad Register 写入新值来重新触发。计数器将在下一个 TIMCLK 上升沿(当 TIMCLKENX 为高时)切换到新加载的值。

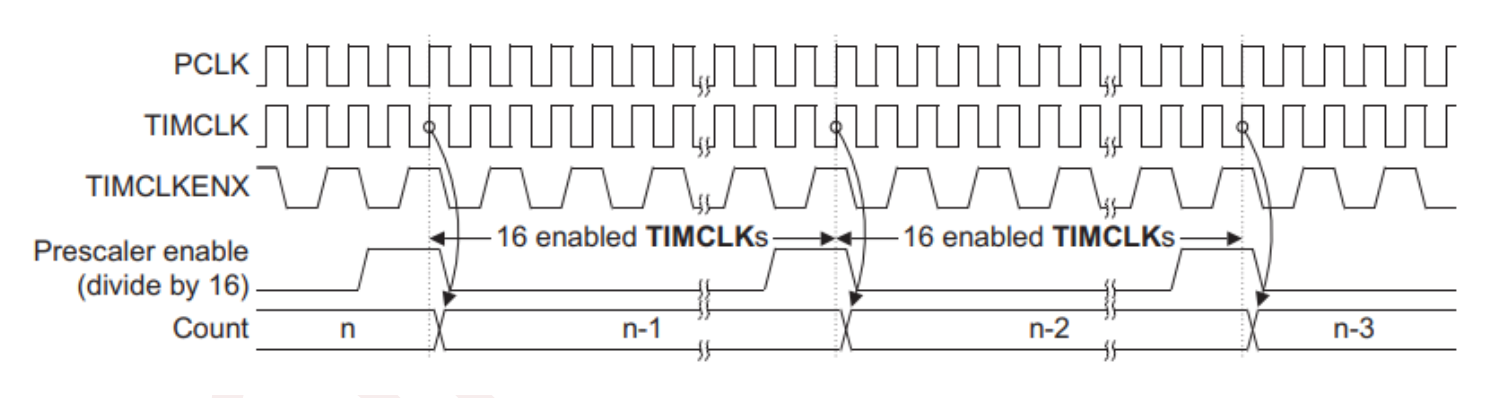

7.2.2.7 中断行为¶

当 IntEnable = 1 且在 32 位模式下计数器达到 0x00000000,或在 16 位模式下计数器达到 0xXXXX0000 时,会生成中断。

在 16 位模式下,计数器的高 16 位将被忽略。

当定时器模块通过拉高 TIMINTX 信号来发起中断时,该信号的时序是基于由 TIMCLKENX 启用的 TIMCLK 的上升沿生成的。

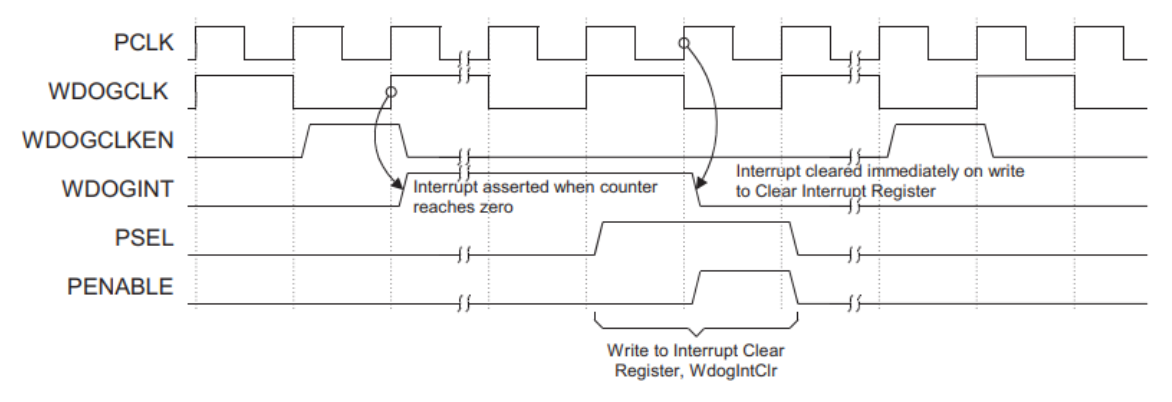

当通过写入中断清除寄存器 TimerXIntClr 来清除中断时,TIMINTX 信号将在 PCLK 时钟域内立即被拉低,而不会等待下一个被启用的 TIMCLK 上升沿。

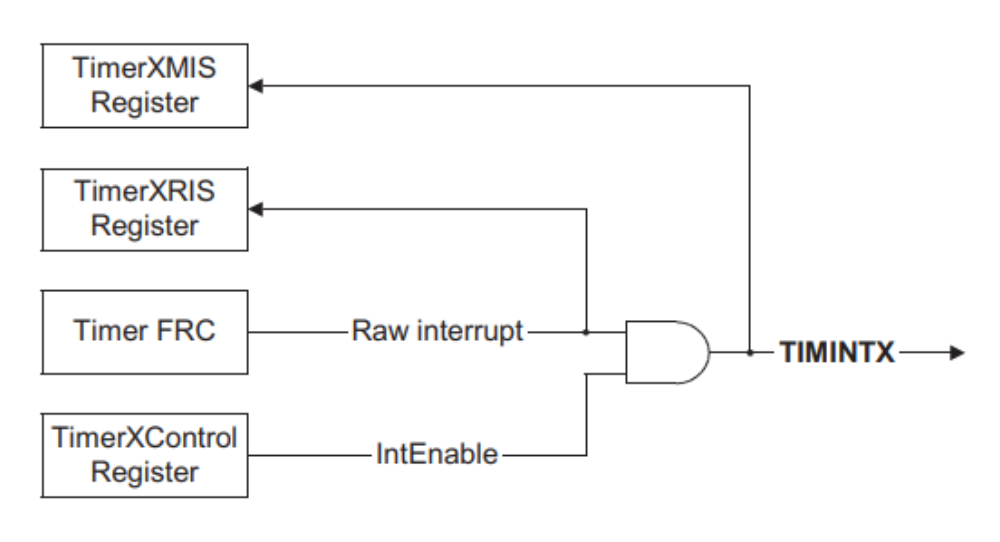

下图展示了一个中断触发与清除时序的示例。

由定时器模块生成的中断信号 TIMINT1 和 TIMINT2,可以通过将 TimerXControl 寄存器中的 IntEnable 位设置为 0 来屏蔽。

在屏蔽之前的原始中断状态可以通过 TimerXRIS 寄存器读取,而屏蔽后的中断状态可以通过 TimerXMIS 寄存器读取。

下图展示了如何访问原始和屏蔽后的中断状态。

7.2.2.8 定时器间隔的编程¶

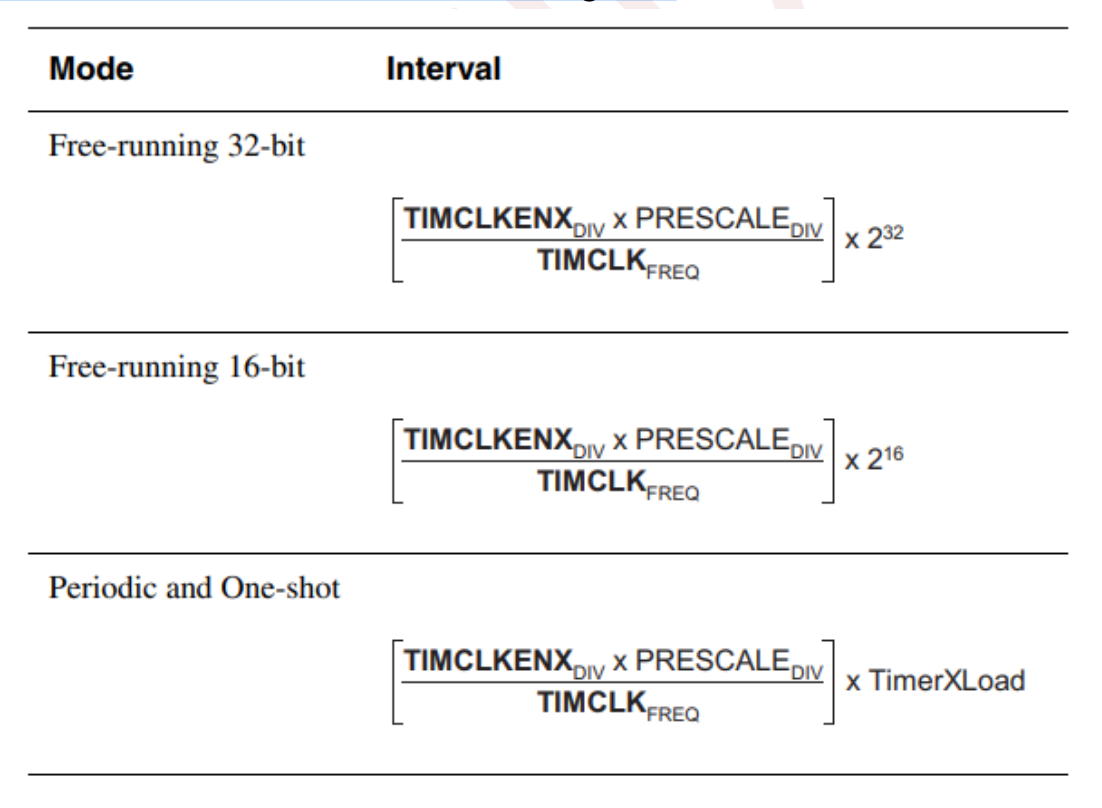

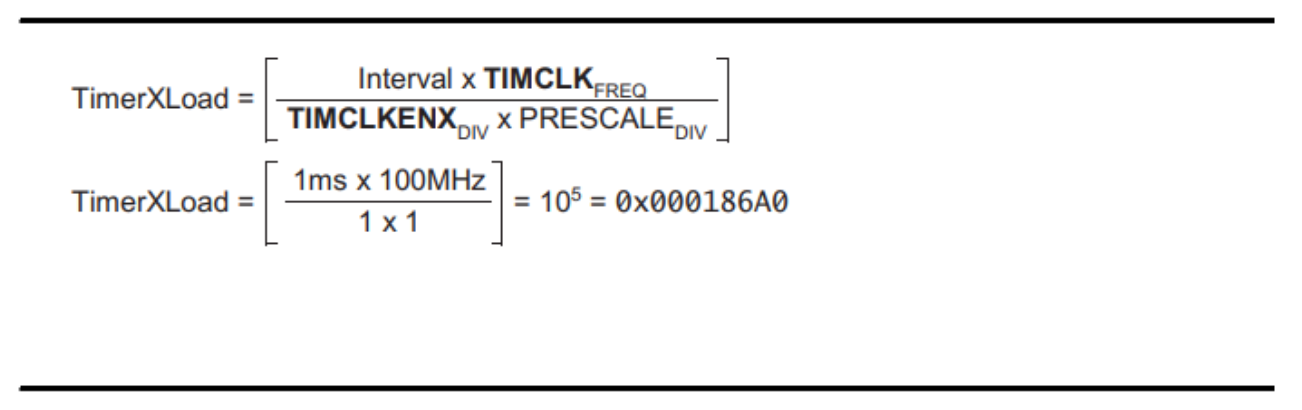

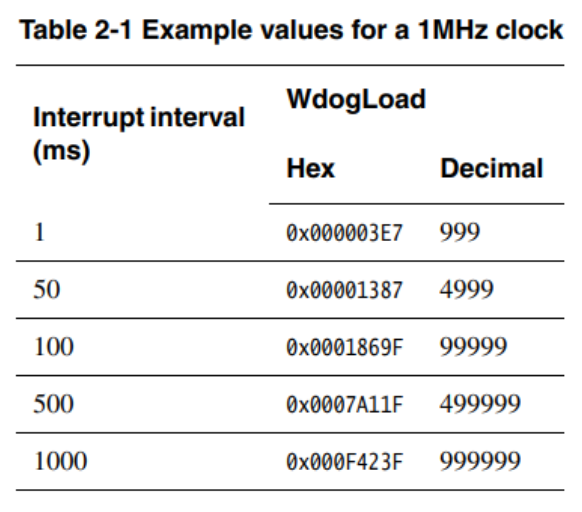

下表展示了用于计算每种定时器模式下生成的定时器间隔的公式,涉及以下参数:

TIMCLKFREQ:TIMCLK的频率。TIMCLKENXDIV:由时钟使能信号TIMCLKENX引起的TIMCLK有效分频。例如,如果TIMCLKENX每四个TIMCLK边沿使能一次,则TIMCLKENXDIV = 4。PRESCALEDIV:预分频因子,可为 1、16 或 256。由控制寄存器的位[3:2]决定。TimerXLoad:加载寄存器中的值。

例如,若 TIMCLK = 100MHz、TIMCLKENXDIV = 1 且 PRESCALEDIV = 1,则为了实现 1ms 周期性间隔,所需的 TimerXLoad 值如下例所示计算。

7.3 编程模型(Programmer’s Model)¶

7.3.1 寄存器概览(Summary of Registers)¶

| 地址偏移 | 类型 | 位宽 | 复位值 | 名称 | 描述 |

|---|---|---|---|---|---|

| Base+0x00 | 读/写 | 32 | 0x00000000 | Timer1Load | 参见第 3.2.1 节的加载寄存器 TimerXLoad |

| Base+0x04 | 只读 | 32 | 0xFFFFFFFF | Timer1Value | 参见第 3.2.2 节的当前值寄存器 TimerXValue |

| Base+0x08 | 读/写 | 8 | 0x20 | Timer1Control | 参见第 3.2.3 节的控制寄存器 TimerXControl |

| Base+0x0C | 写 | - | - | Timer1IntClr | 参见第 3.2.4 节的中断清除寄存器 TimerXIntClr |

| Base+0x10 | 只读 | 1 | 0x0 | Timer1RIS | 参见第 3.2.5 节的原始中断状态寄存器 TimerXRIS |

| Base+0x14 | 只读 | 1 | 0x0 | Timer1MIS | 参见第 3.2.6 节的屏蔽中断状态寄存器 TimerXMIS |

| Base+0x18 | 读/写 | 32 | 0x00000000 | Timer1BGLoad | 参见第 3.2.7 节的后台加载寄存器 TimerXBGLoad |

| Base+0x20 | 读/写 | 32 | 0x00000000 | Timer2Load | 参见第 3.2.1 节的加载寄存器 TimerXLoad |

| Base+0x24 | 只读 | 32 | 0xFFFFFFFF | Timer2Value | 参见第 3.2.2 节的当前值寄存器 TimerXValue |

| Base+0x28 | 读/写 | 8 | 0x20 | Timer2Control | 参见第 3.2.3 节的控制寄存器 TimerXControl |

| Base+0x2C | 写 | - | - | Timer2IntClr | 参见第 3.2.4 节的中断清除寄存器 TimerXIntClr |

| Base+0x30 | 只读 | 1 | 0x0 | Timer2RIS | 参见第 3.2.5 节的原始中断状态寄存器 TimerXRIS |

| Base+0x34 | 只读 | 1 | 0x0 | Timer2MIS | 参见第 3.2.6 节的屏蔽中断状态寄存器 TimerXMIS |

| Base+0x38 | 读/写 | 32 | 0x00000000 | Timer2BGLoad | 参见第 3.2.7 节的后台加载寄存器 TimerXBGLoad |

7.4 寄存器描述¶

7.4.1 加载寄存器(Load Register),TimerXLoad¶

TimerXLoad 寄存器是一个 32 位的寄存器,包含计数器将要递减的起始值。当启用了周期模式(Periodic mode)且当前计数值减至零时,该值会被用于重新加载计数器。

当该寄存器被直接写入新值时,在下一个由 TIMCLKENX 使能的 TIMCLK 上升沿,当前计数器值将立即重置为该新值。

注意:

TimerXLoad的最小有效值为 1。如果设置为 0,则会立即触发一次中断。

当写入 TimerXBGLoad 寄存器时,该值也会覆盖 TimerXLoad 寄存器的内容,但不会立即影响当前计数值。

如果在某一由 TIMCLKENX 使能的 TIMCLK 上升沿之前,同时对 TimerXLoad 和 TimerXBGLoad 寄存器进行了写入操作,则在下一个 TIMCLK 上升沿时,写入 TimerXLoad 的值会取代当前计数值。随后,每次计数器归零时,当前计数值将重置为 TimerXBGLoad 中写入的值。

在上述两个写操作完成后,任何时刻读取 TimerXLoad 寄存器,将返回写入 TimerXBGLoad 的值。也就是说,读取 TimerXLoad 始终返回下一个周期内周期模式将生效的值。

7.4.2 当前值寄存器(Current Value Register),TimerXValue¶

TimerXValue 寄存器是一个 32 位的只读寄存器,用于提供当前递减计数器的数值。

当通过写入 TimerXLoad 设定了新的加载值后,TimerXValue 会立即在 PCLK 时钟域 中反映该新加载值,而无需等待由 TIMCLKENX 使能的下一个 TIMCLK 上升沿。

注意:

当处于 16 位定时器模式 时,TimerXValue的高 16 位不会被自动清零。如果定时器之前处于 32 位模式,而在切换为 16 位模式后尚未对TimerXLoad进行写操作,则TimerXValue的高 16 位可能包含非零值。

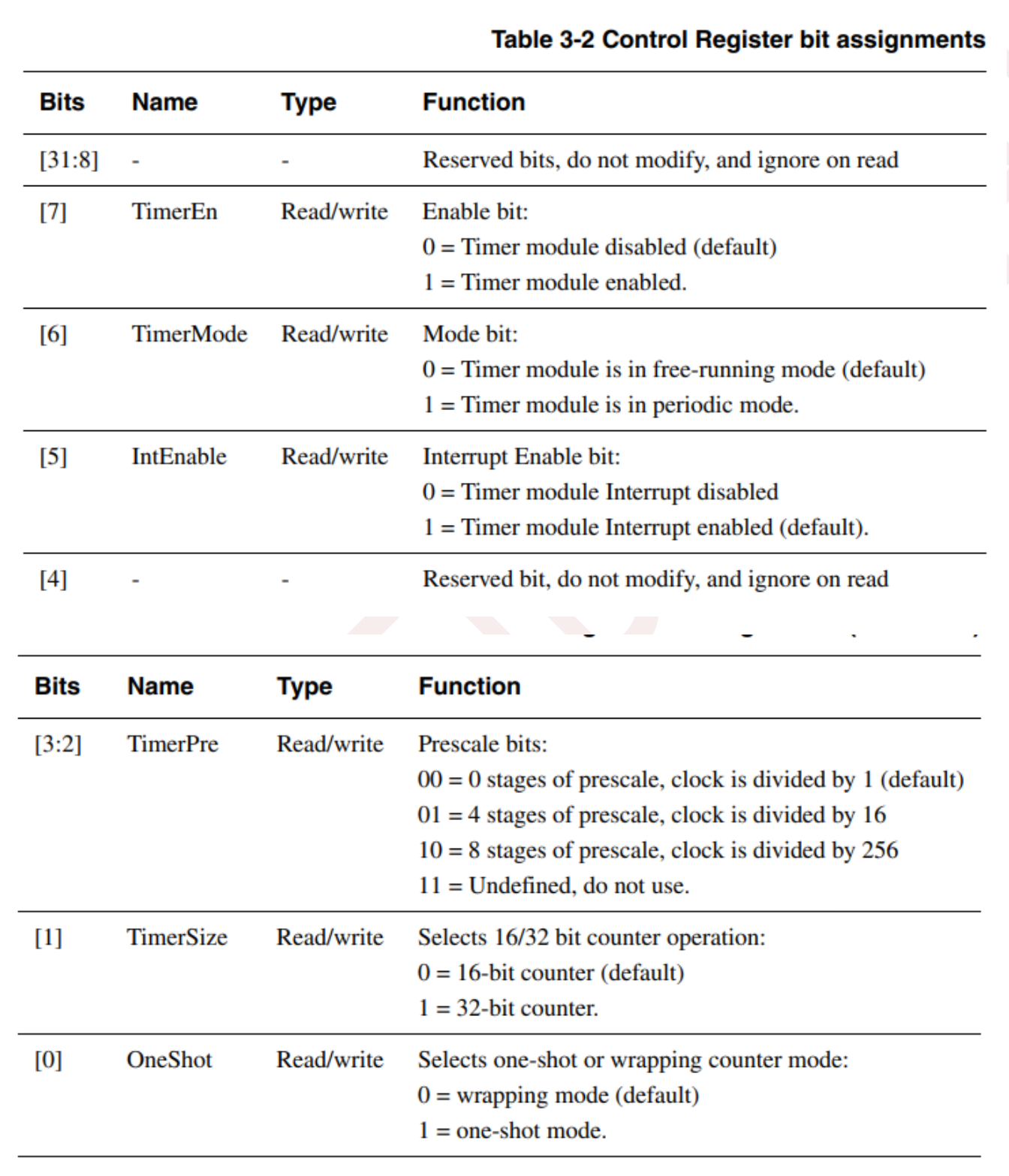

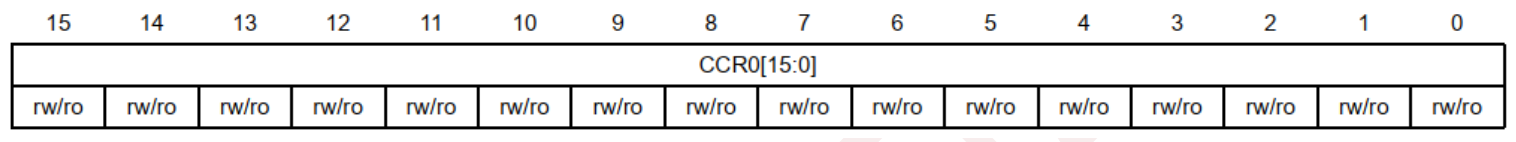

7.4.3 控制寄存器(Control Register),TimerXControl¶

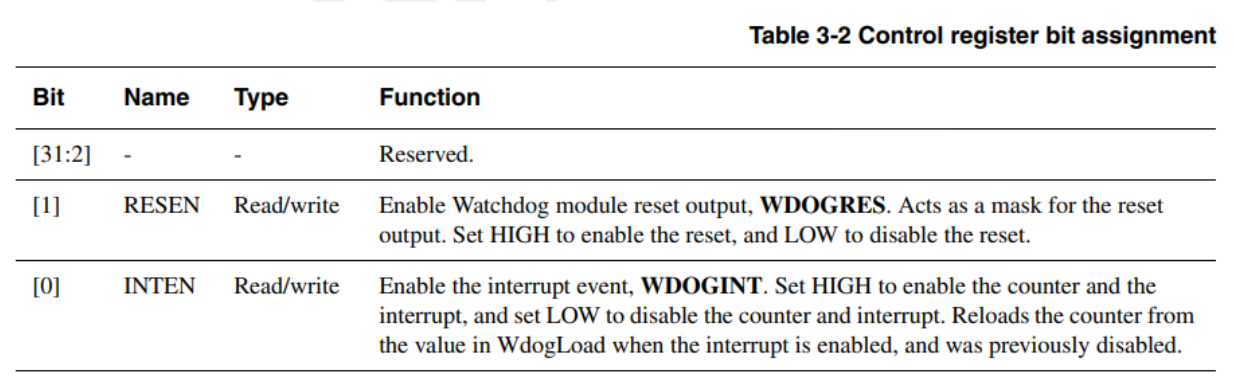

控制寄存器的位分配如下面的表格所示。

⚠️ 注意:

在定时器模块运行时,不得更改计数模式、计数器位宽或预分频器设置。

如果需要应用新的配置,必须遵循以下流程:

- 禁用定时器模块;

- 向相关寄存器写入新的配置值;

- 完成配置更改后,再重新使能定时器模块。

如果不按照此顺序操作,可能会导致器件行为不可预测。

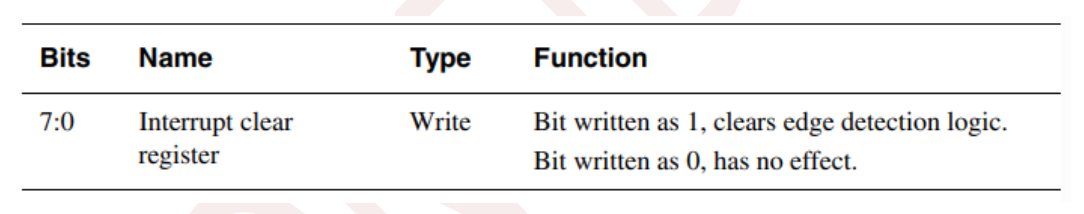

7.4.4 中断清除寄存器(Interrupt Clear Register),TimerXIntClr¶

对该寄存器的任意写操作都会清除来自计数器的中断输出。

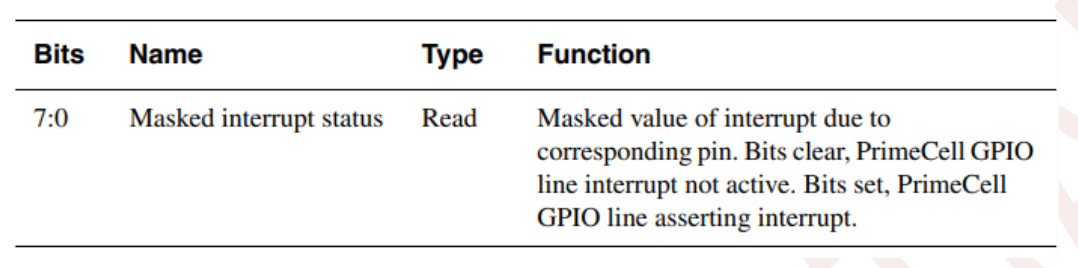

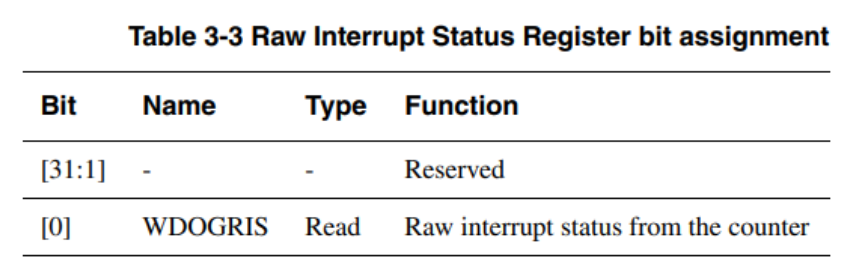

7.4.5 原始中断状态寄存器(Raw Interrupt Status Register),TimerXRIS¶

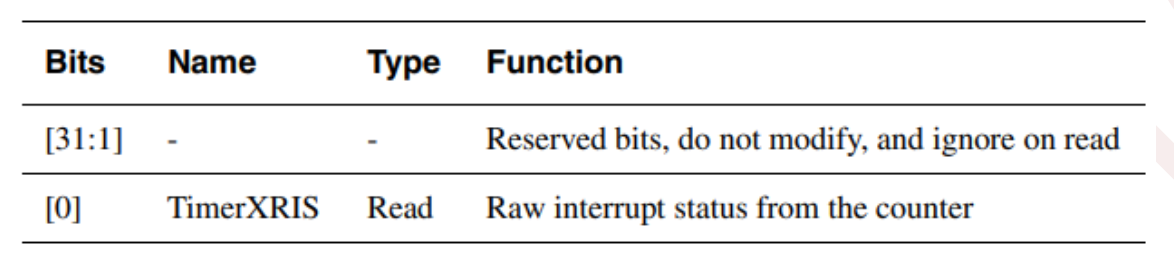

TimerXRIS 寄存器用于指示来自计数器的原始中断状态。

位分配详见下表。

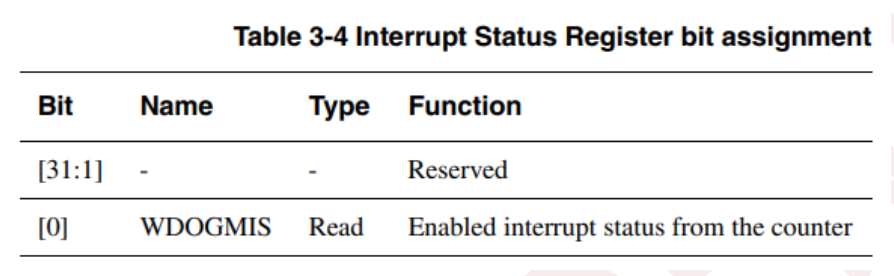

7.4.6 屏蔽中断状态寄存器(Masked Interrupt Status Register),TimerXMIS¶

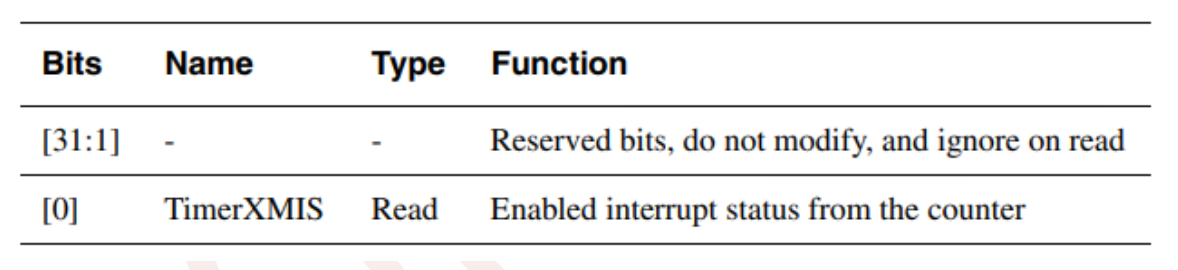

TimerXMIS 寄存器用于指示来自计数器的屏蔽中断状态。

该值是原始中断状态与控制寄存器中的定时器中断使能位(Interrupt Enable bit)的逻辑与(AND)运算结果,

并且与输出至中断引脚 TIMINTX 的值一致。

位分配详见下表。

7.4.7 背景装载寄存器(Background Load Register),TimerXBGLoad¶

TimerXBGLoad 是一个 32 位寄存器,包含计数器用于递减的初始值。

当启用周期模式(Periodic mode)并且当前计数器值减至零时,将使用该寄存器中的值重新装载计数器。

该寄存器提供了一种间接访问 TimerXLoad 寄存器的方式。不同之处在于:

- 写入 TimerXBGLoad 并不会立即使计数器从新值开始重计。

从该寄存器读取时,返回的值与读取 TimerXLoad 时相同。

详细信息请参见前文的装载寄存器(TimerXLoad)。

8 高级控制定时器¶

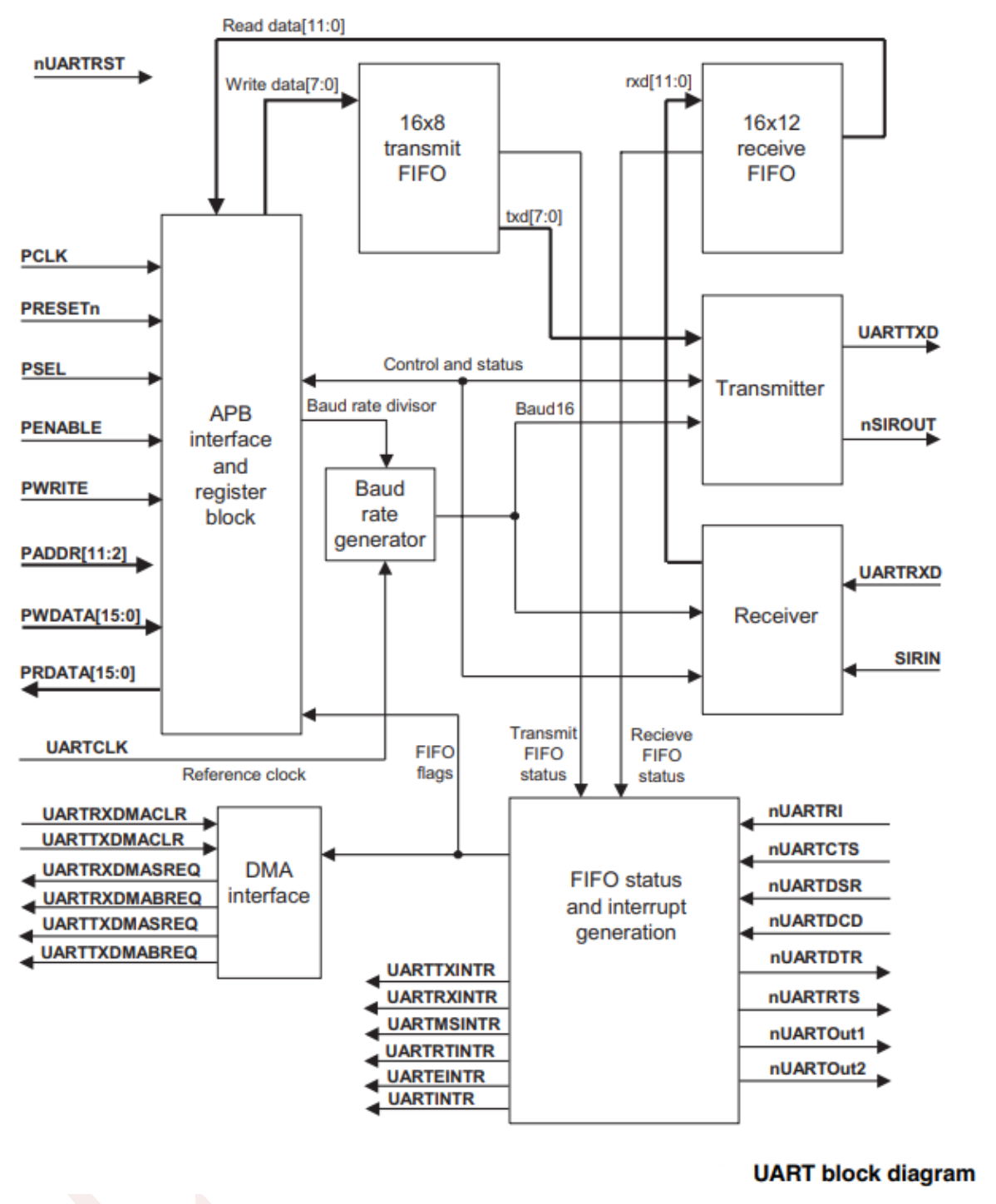

8.1 简介¶

高级控制定时器包含一个由可编程预分频器驱动的 32 位自动重载计数器。

它可用于多种目的,包括:

- 测量输入信号的脉冲长度(输入捕获)

- 生成输出波形(输出比较、PWM、带死区时间插入的互补 PWM)

通过定时器预分频器和 RCC 时钟控制器的分频器,可以将脉冲长度和波形周期调节为从几微秒到数毫秒的范围。

高级控制定时器和通用定时器是完全独立的,不共享任何资源。

8.2 主要特性¶

定时器的主要功能包括:

- 32 位自动重载计数器,支持向上计数、向下计数、向上/向下计数模式。

- 16 位可编程预分频器,允许将计数器时钟频率划分为 1 到 65536 之间的任意因数(支持动态更改)。

-

最多 4 个独立通道,可用于:

- 输入捕获(Input Capture)

- 输出比较(Output Compare)

- PWM 生成(边沿对齐或中心对齐模式)

- 单脉冲模式输出(One-Pulse Mode)

-

互补输出,支持可编程死区时间插入(Dead-time Insertion)

- 同步电路,用于通过外部信号控制定时器或将多个定时器互联。

- 重复计数器,允许在计数器经历指定次数周期后才更新定时器寄存器。

- 断路输入(Break Input),用于将定时器输出信号置于复位状态或已知状态。

-

中断/DMA 生成,可响应以下事件:

- 更新事件(计数器溢出/下溢、通过软件或内部/外部触发器初始化)

- 触发事件(计数器开始、停止、初始化,或通过内部/外部触发器进行计数)

- 输入捕获事件

- 输出比较事件

- 断路输入事件

-

支持增量式(正交)编码器和霍尔传感器,用于位置检测。

- 触发输入,可用于外部时钟或逐周期电流管理。

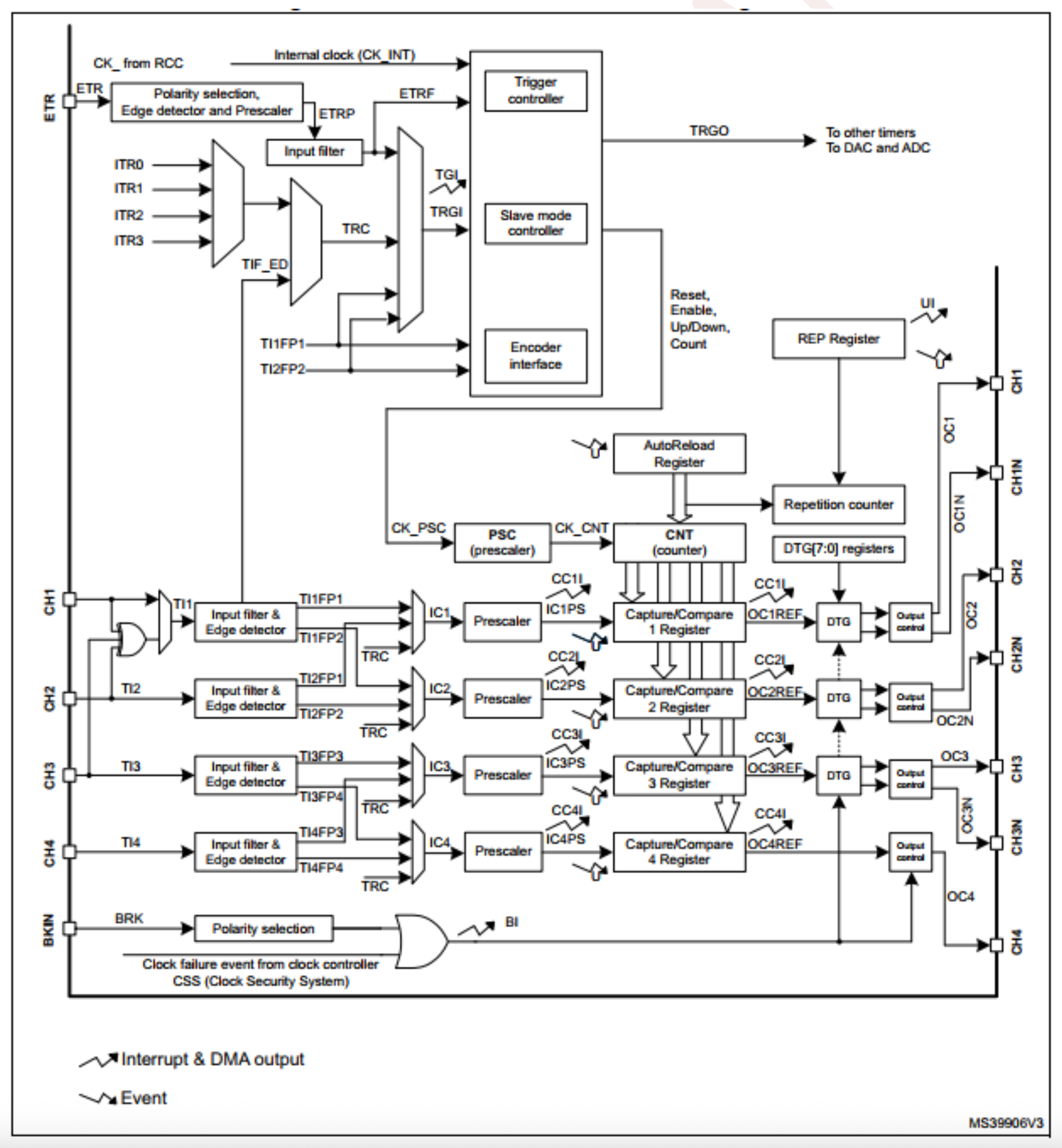

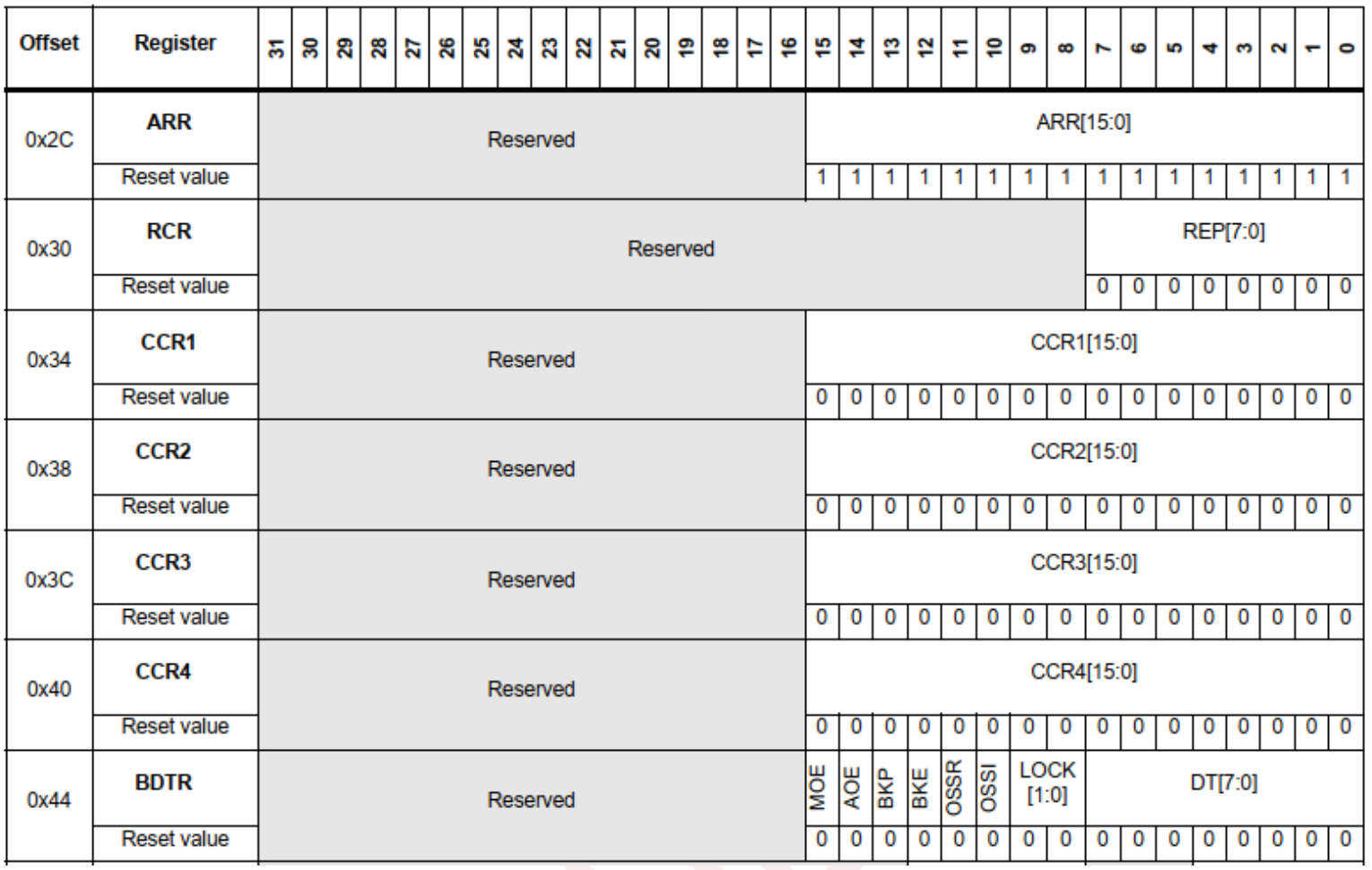

图 1:高级控制定时器框图

8.3 功能描述¶

8.3.1 时间基准单元¶

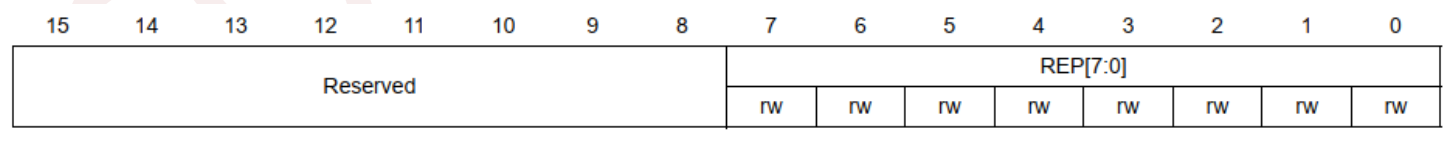

可编程高级控制定时器的主要模块是一个 16 位计数器及其相关的自动重载寄存器。该计数器可以向上计数、向下计数或向上/向下计数。计数器时钟可以通过预分频器进行分频。

计数器、自动重载寄存器和预分频器寄存器可以由软件读取或写入,即使计数器正在运行。

时间基准单元包括:

- 计数器寄存器(TCNT)

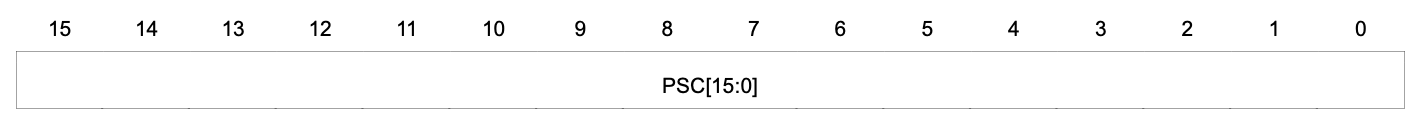

- 预分频器寄存器(PSC)

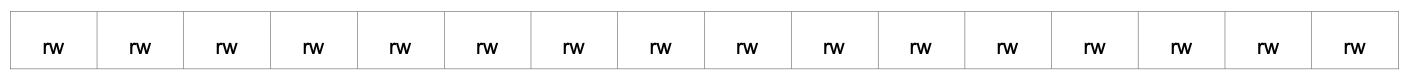

- 自动重载寄存器(ARR)

- 重复计数器寄存器(RCR)

自动重载寄存器是预加载的。写入或读取自动重载寄存器时访问的是预加载寄存器。预加载寄存器的内容会根据 CR1 寄存器中的 ARPE 位 传输到影子寄存器中,传输的时机有以下两种:

- 永久传输

- 在每次更新事件(UEV)时传输

更新事件在计数器溢出(向上计数)或下溢(向下计数)时发生,且 CR1 寄存器中的 UDIS 位 为 0 时触发。它也可以由软件触发。每种配置下更新事件的生成方式在后续有详细描述。

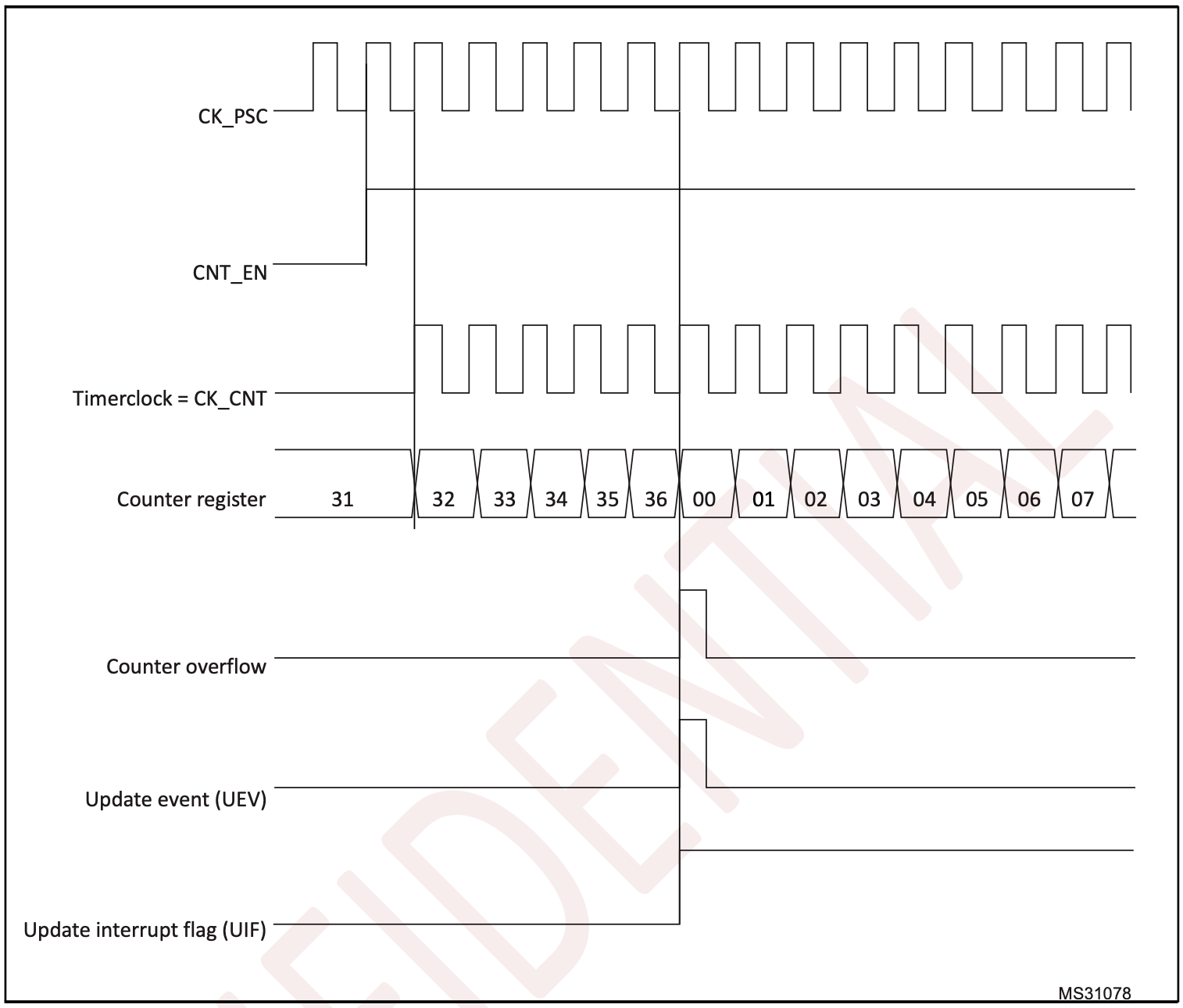

计数器由预分频器输出 CK_CNT 提供时钟,只有当 CR1 寄存器中的 CEN 位 被设置时,CK_CNT 才会启用(请参见从属模式控制器描述,获取更多关于计数器启用的详细信息)。注意,计数器将在设置 CEN 位后的下一个时钟周期开始计数。

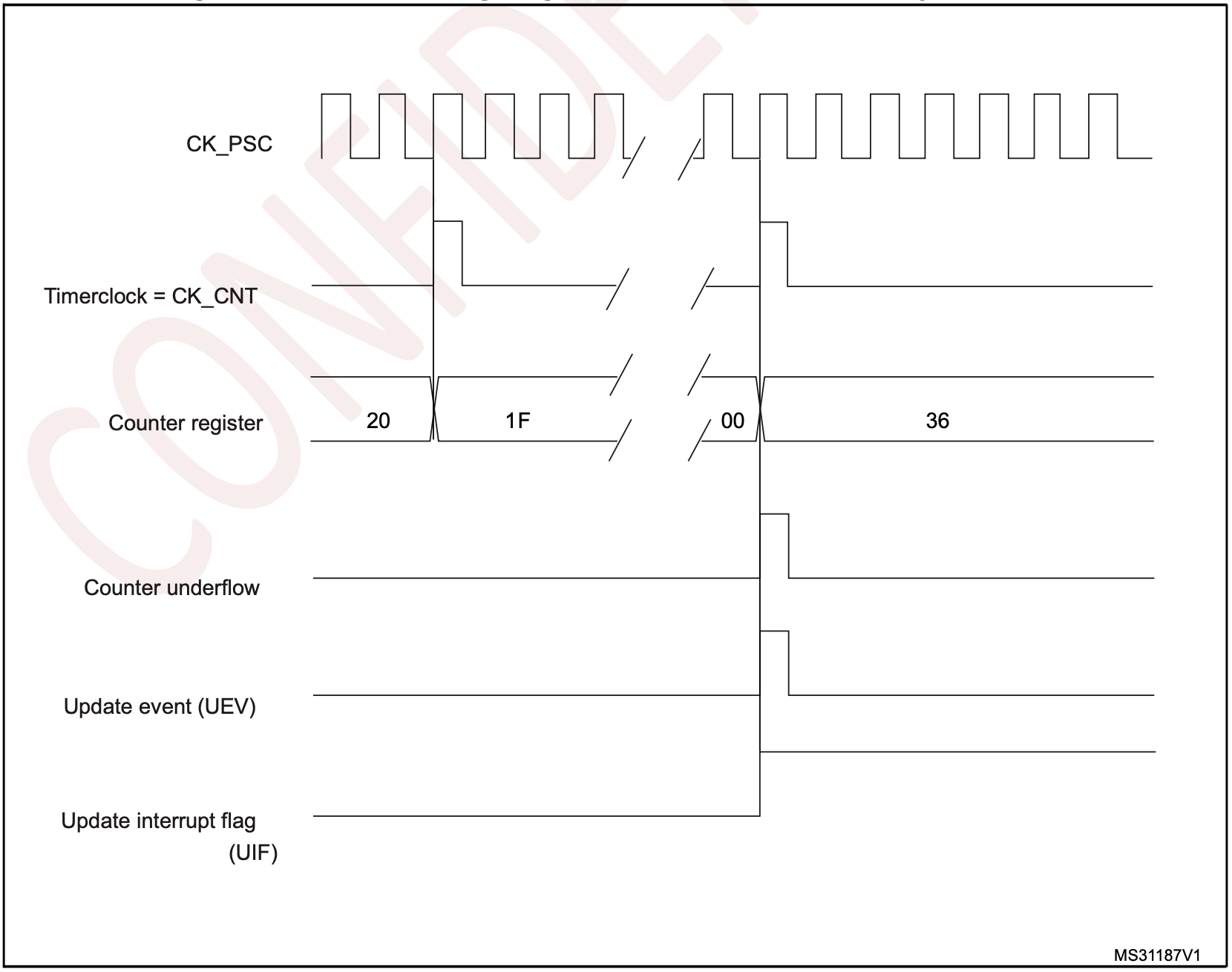

预分频器描述¶

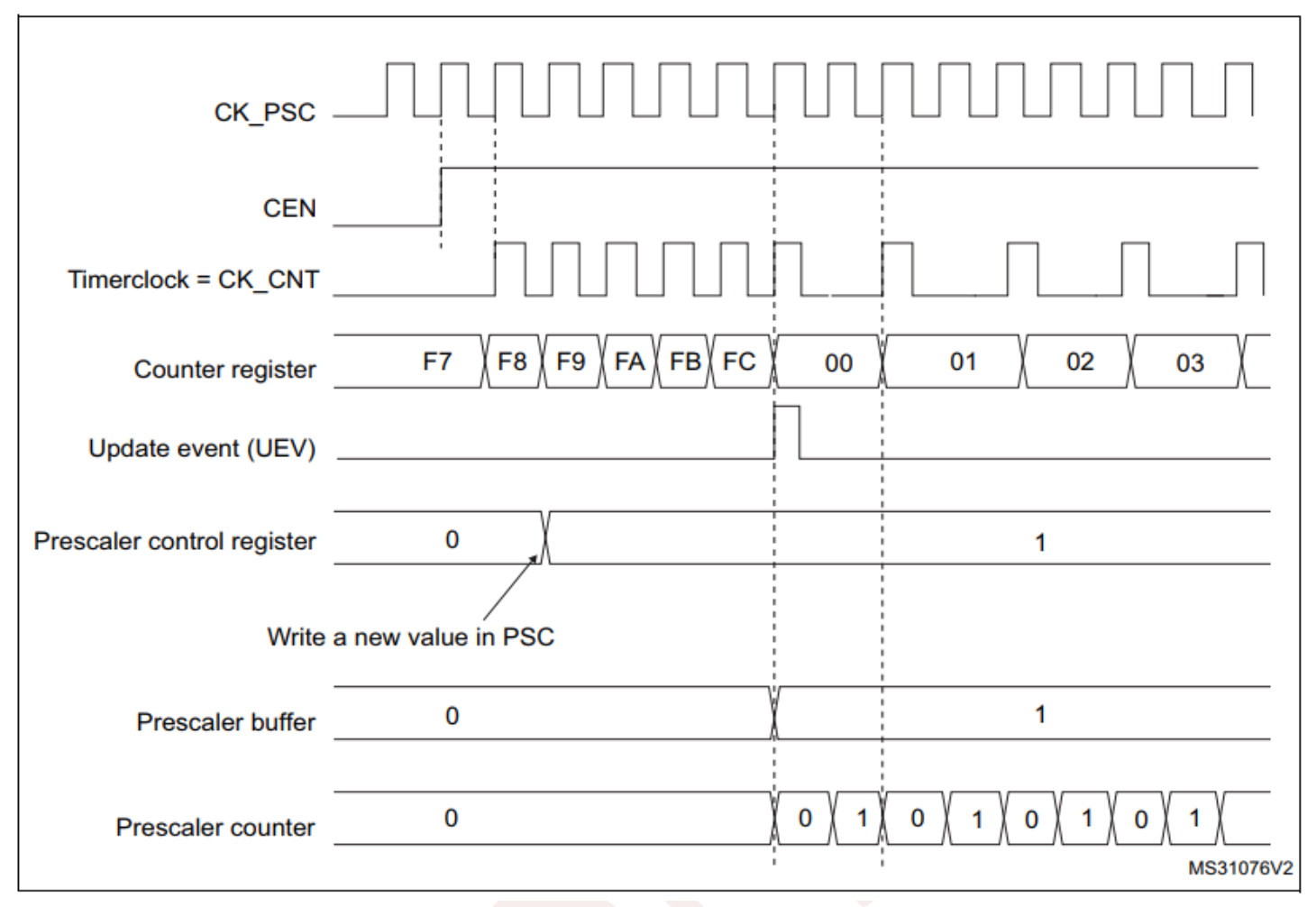

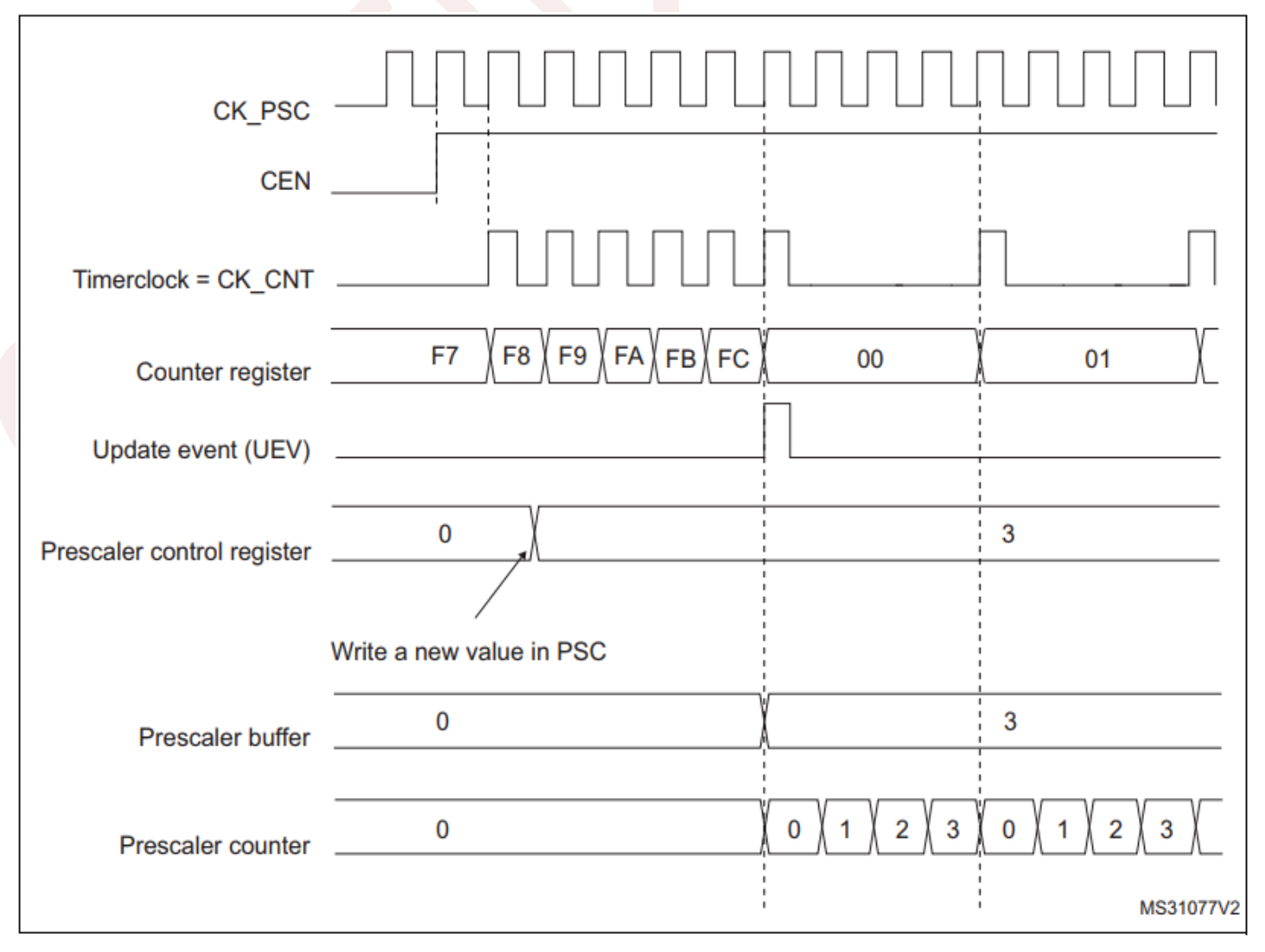

预分频器可以将计数器时钟频率按任意因数从 1 到 65536 进行分频。它基于一个 16 位计数器,通过一个 16 位寄存器(在 PSC 寄存器中)控制。由于该控制寄存器是缓冲的,因此可以动态修改预分频比,新的预分频比将在下一个更新事件时生效。

图 2 和图 3 给出了在动态修改预分频器比值时,计数器行为的一些示例:

图 2:预分频器从 1 更改为 2 时的计数器时序图

图 3:预分频器从 1 更改为 4 时的计数器时序图

8.3.2 计数器模式¶

向上计数模式¶

在向上计数模式中,计数器从 0 计数到自动重装值(即 ARR 寄存器中的内容),然后从 0 重新开始计数,并生成一个计数器溢出事件。

- 如果使用了重复计数器(repetition counter),则在重复计数达到重复计数器寄存器中设定的值加一(

RCR+1)次后,会生成一次更新事件(UEV)。否则,每次计数器溢出都会生成一个更新事件。 - 通过软件或使用从模式控制器设置

EGR寄存器中的UG位,也会生成一个更新事件。 - 可以通过软件设置

CR1寄存器中的UDIS位来禁用更新事件 UEV。这是为了在向预装寄存器中写入新值时避免更新影子寄存器。在UDIS位被设置为 0 之前,将不会发生更新事件。不过,计数器仍从 0 重新开始,同时预分频器的计数器也会重置(但预分频率不变)。

如果

CR1寄存器中的URS位(更新请求选择)被设置,则设置UG位会生成更新事件UEV,但不会设置UIF标志位(因此不会产生中断或 DMA 请求)。这样做是为了在捕获事件清除计数器时避免同时生成更新和捕获中断。

当更新事件发生时,所有寄存器都会被更新,并设置更新标志(SR 寄存器中的 UIF 位),具体取决于 URS 位的设置:

- 重复计数器会重新加载

RCR寄存器的内容, - 自动重装影子寄存器会用预装值(

ARR)进行更新, - 预分频器的缓冲器会用预装值(

PSC寄存器的内容)重新加载。

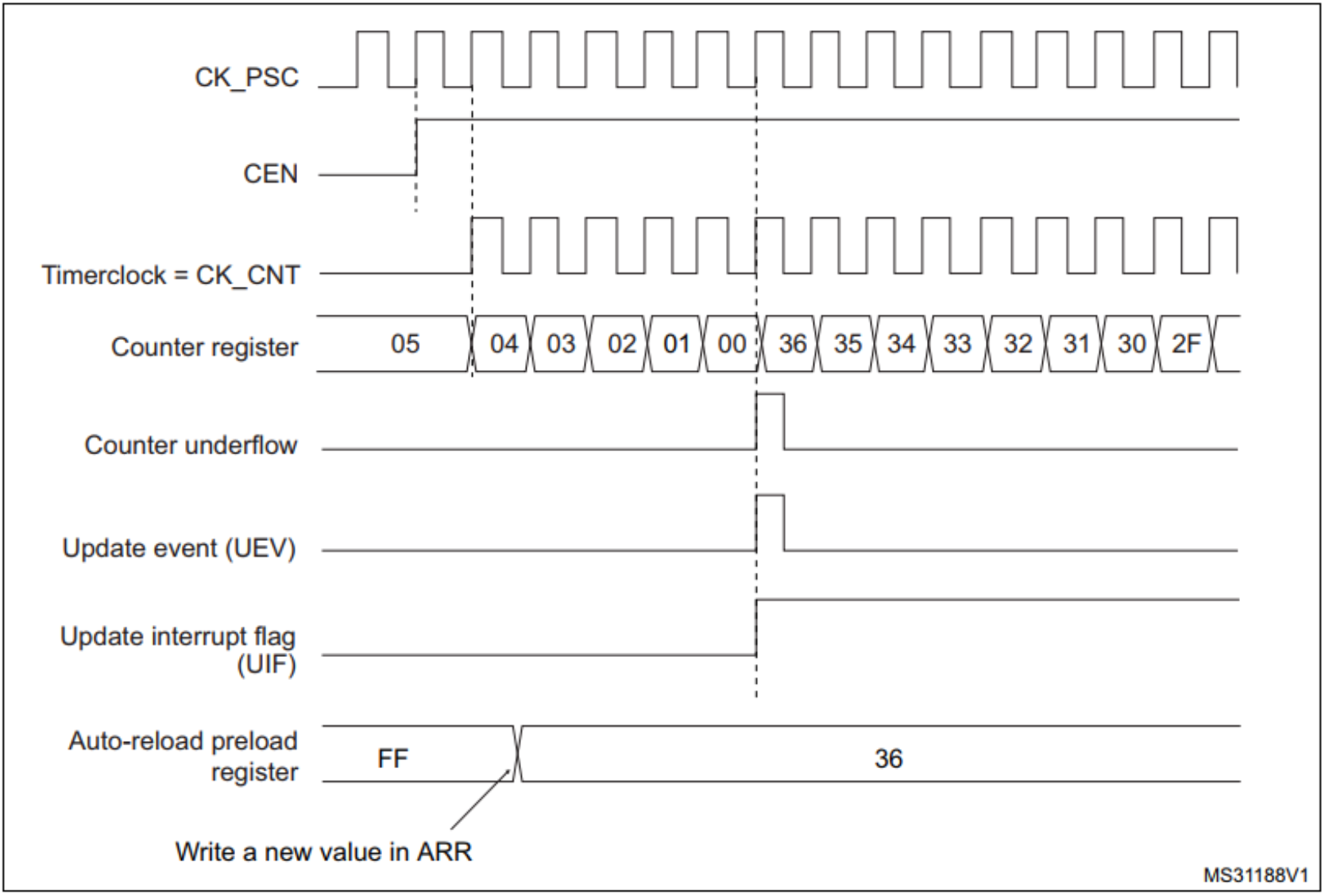

接下来的图示展示了在 ARR =

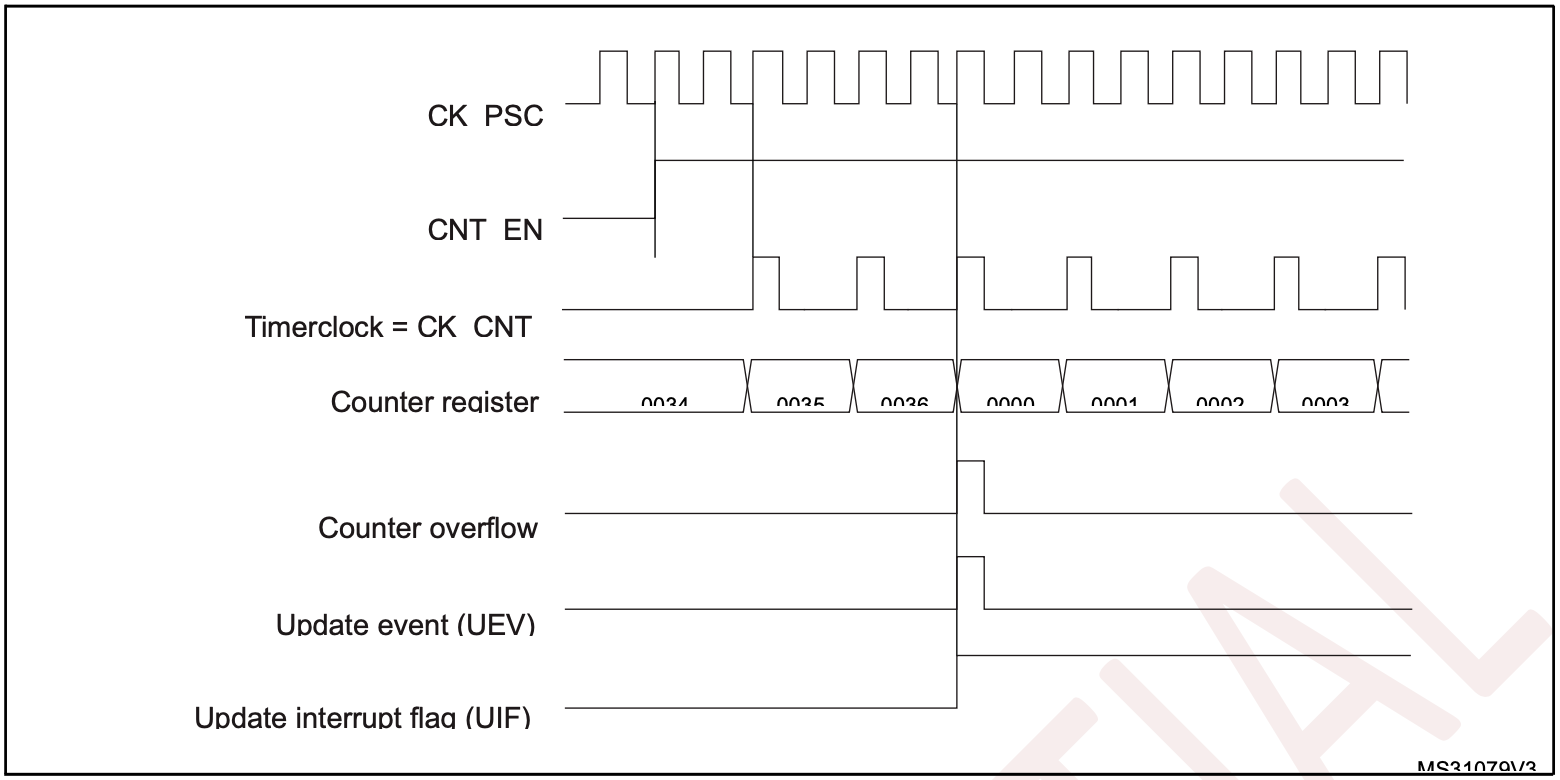

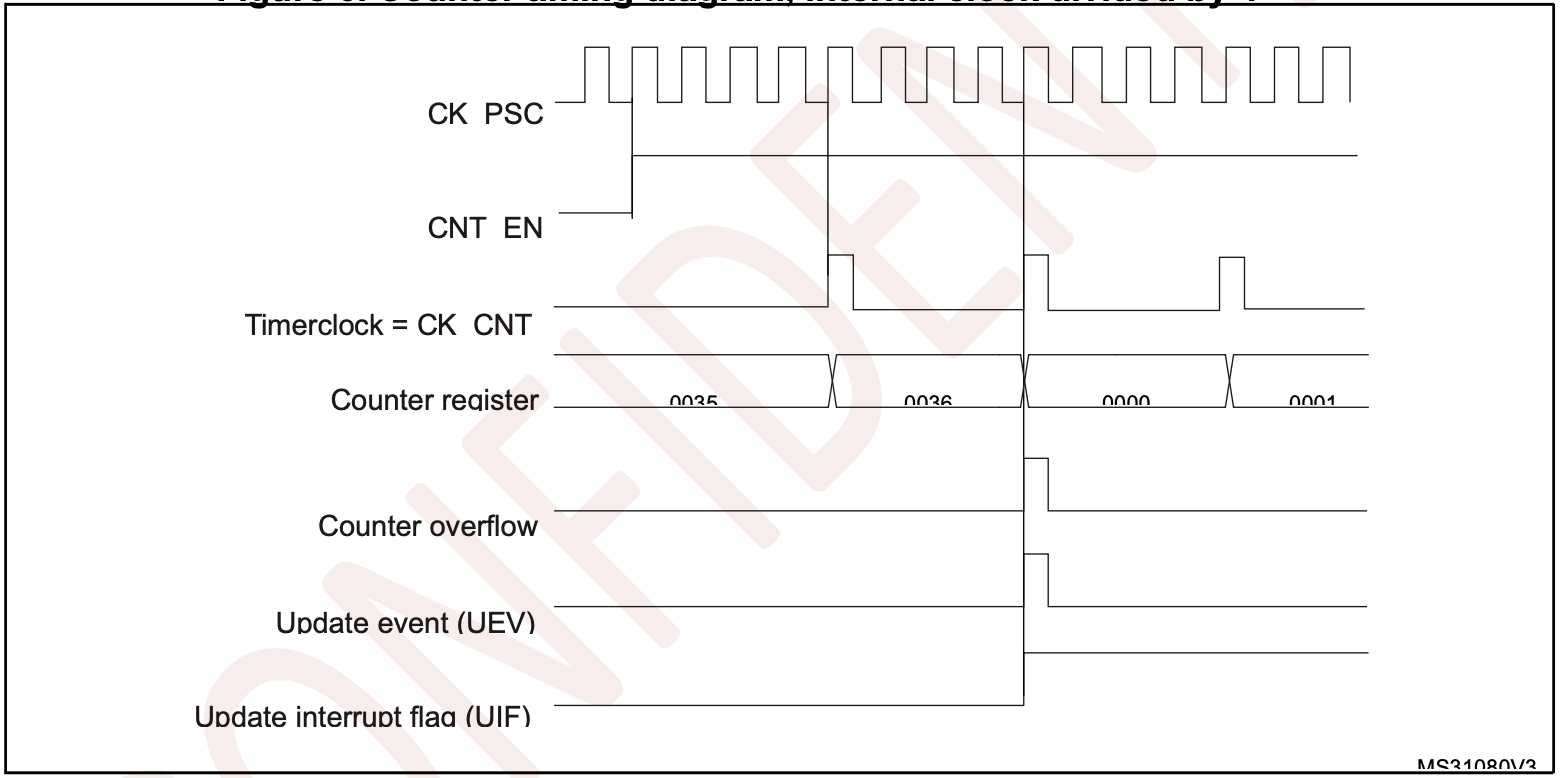

0x36时,在不同时钟频率下计数器的行为示例。图4:计数器时序图,内部时钟不分频(除以1)

图5:计数器时序图,内部时钟除以2

图6:计数器时序图,内部时钟除以4

图7:计数器时序图,内部时钟除以N

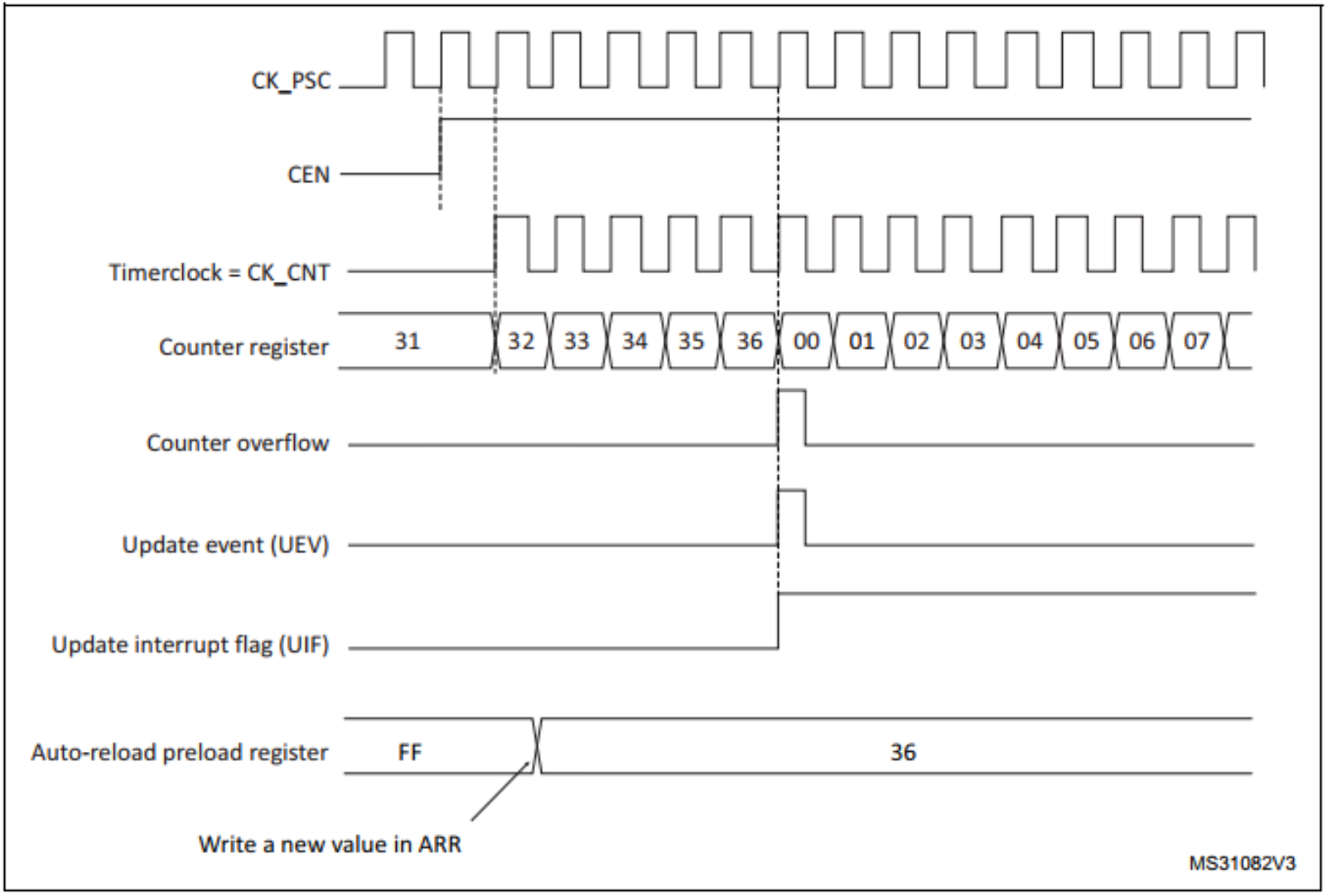

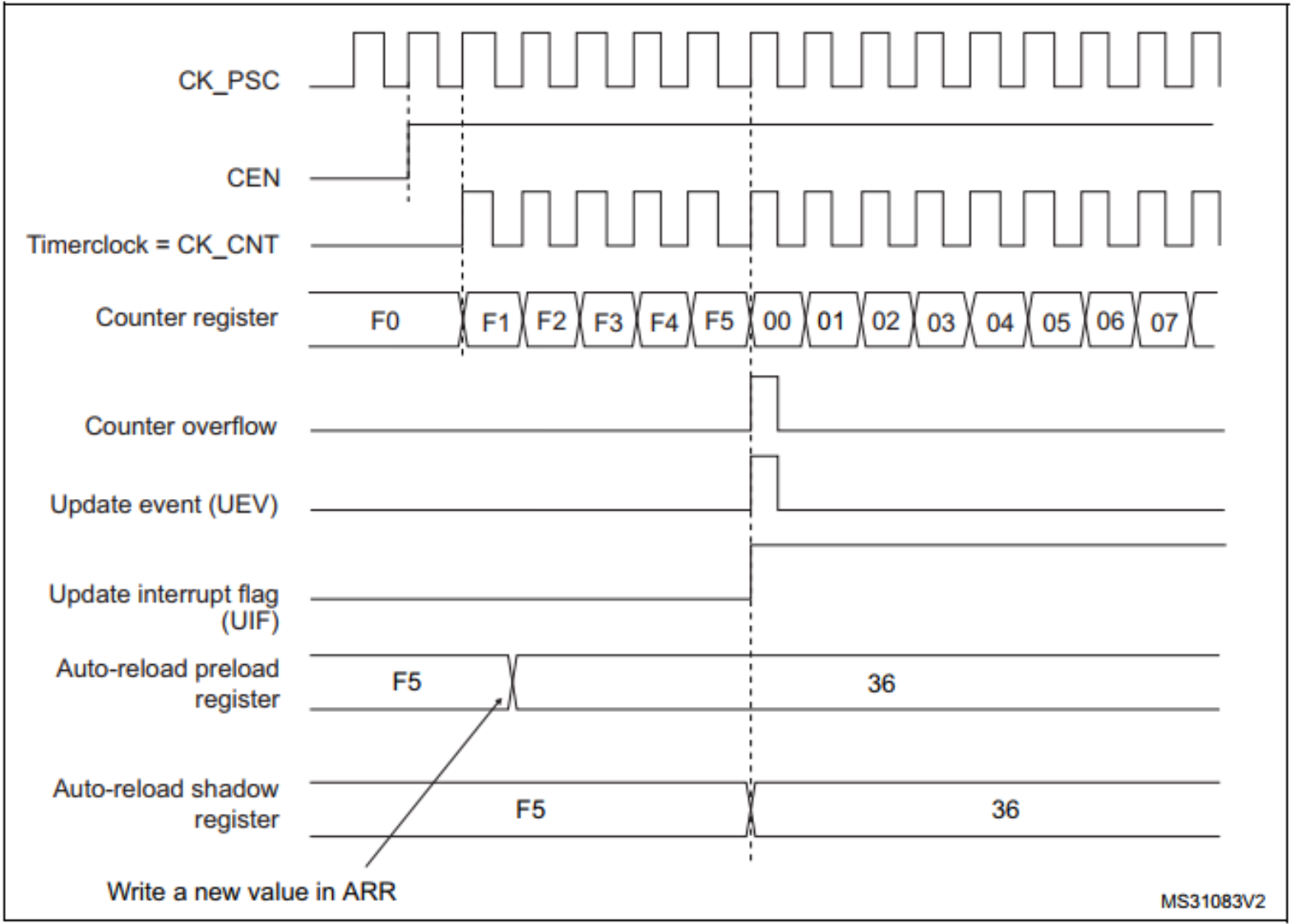

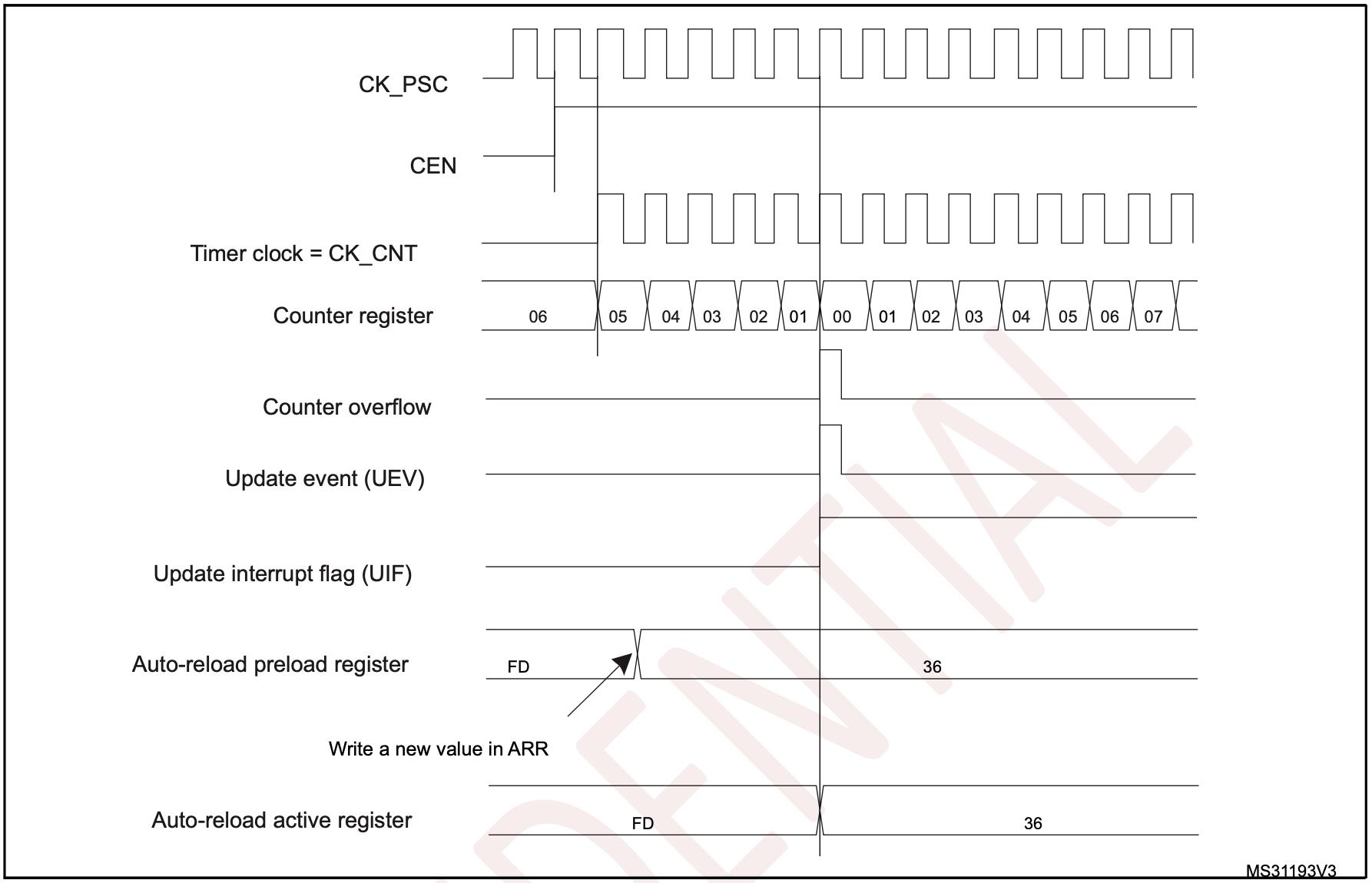

图8:计数器时序图,ARPE=0 时的更新事件(ARR 未预装载)

图9:计数器时序图,ARPE=1 时的更新事件(ARR 已预装载)

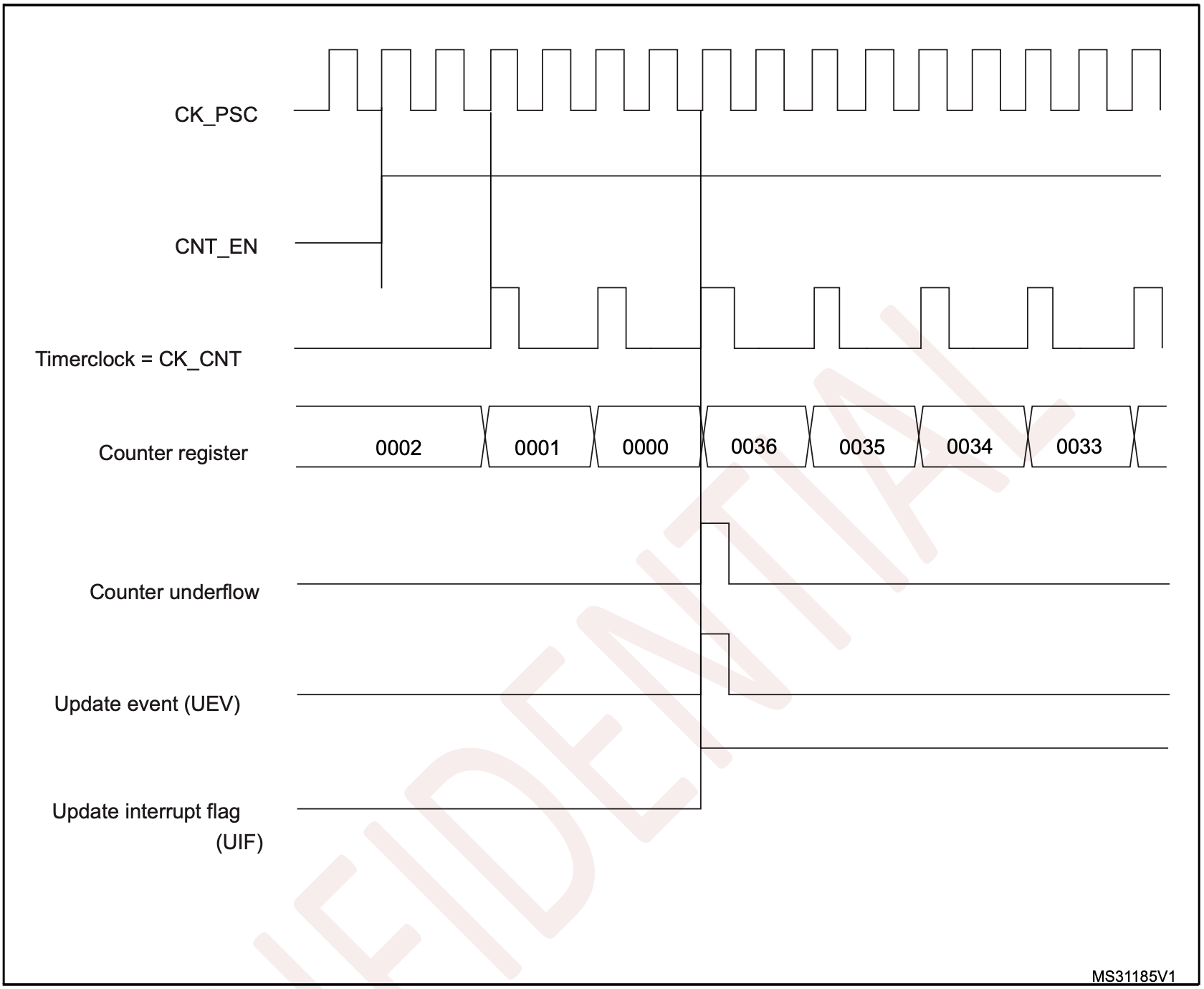

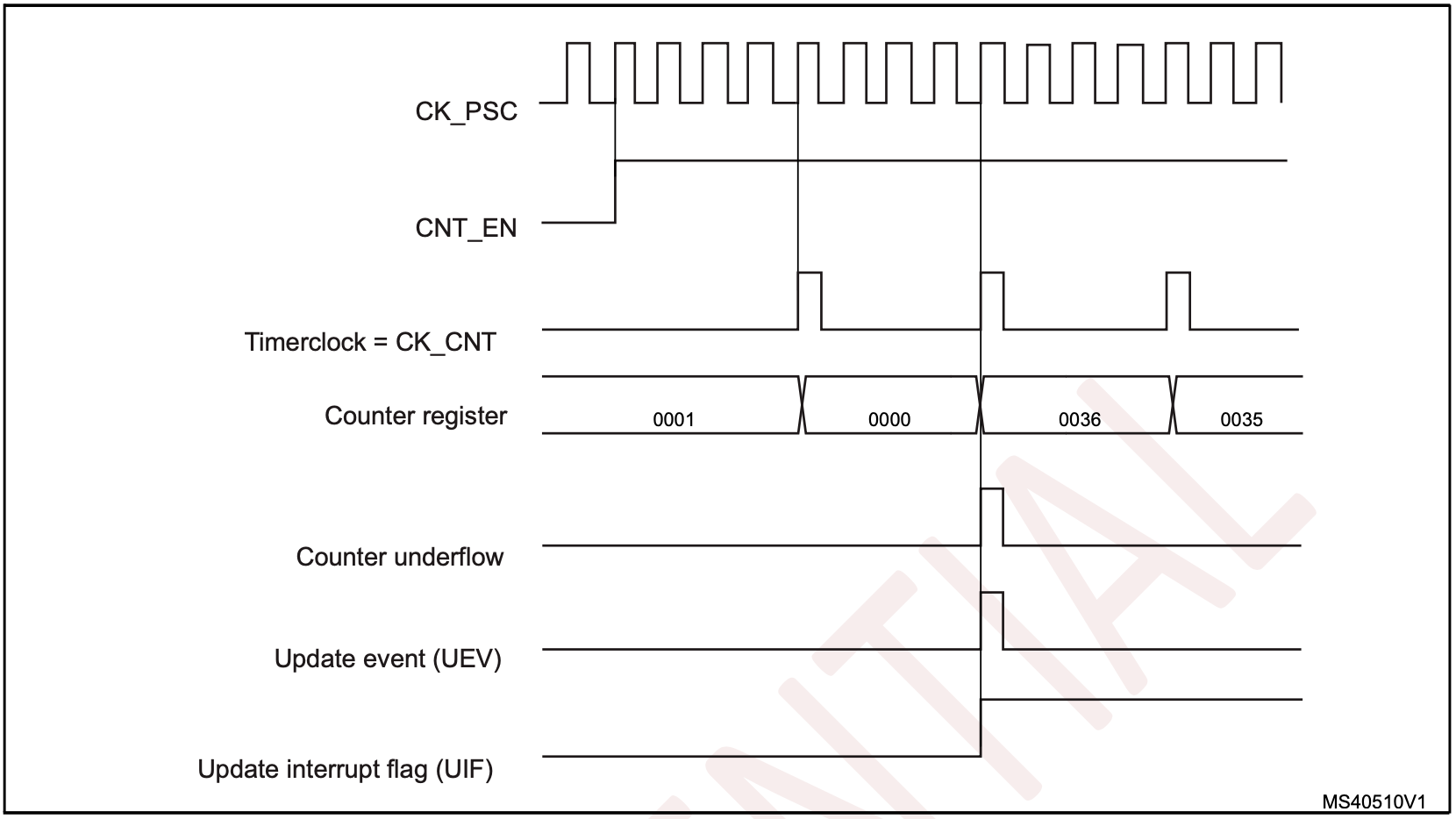

倒计数模式(Downcounting mode)¶

在倒计数模式下,计数器从自动重装值(ARR寄存器的内容)开始向下计数至0,然后重新从自动重装值开始,并生成一个计数器下溢事件。

如果使用了重复计数器,则在重复计数器寄存器中设定的次数加一(RCR+1)次倒计数完成后,才会生成一次更新事件(UEV)。如果未使用重复计数器,则每次计数器下溢时都会生成一次更新事件。

通过软件或从模式控制器设置EGR寄存器中的UG位,也会生成一次更新事件。

可以通过设置CR1寄存器中的UDIS位来禁止软件生成更新事件(UEV),以避免在向预装载寄存器写入新值时更新影子寄存器。此时不会产生任何更新事件,直到将UDIS位重新写为0。然而,计数器仍会从当前的自动重装值重新开始,而预分频器的计数器从0开始(但预分频比率保持不变)。

此外,如果CR1寄存器中的URS位(更新请求选择)被设置,那么设置UG位会生成一个更新事件(UEV),但不会设置UIF标志位(即不会触发中断或DMA请求)。这样可以避免在捕获事件清除计数器时同时生成更新中断和捕获中断。

当发生更新事件时,所有寄存器将被更新,并设置更新标志(SR寄存器中的UIF位,具体取决于URS位):

- 重复计数器将被RCR寄存器的内容重新加载;

- 预分频器的缓冲器将被PSC寄存器的预装值重新加载;

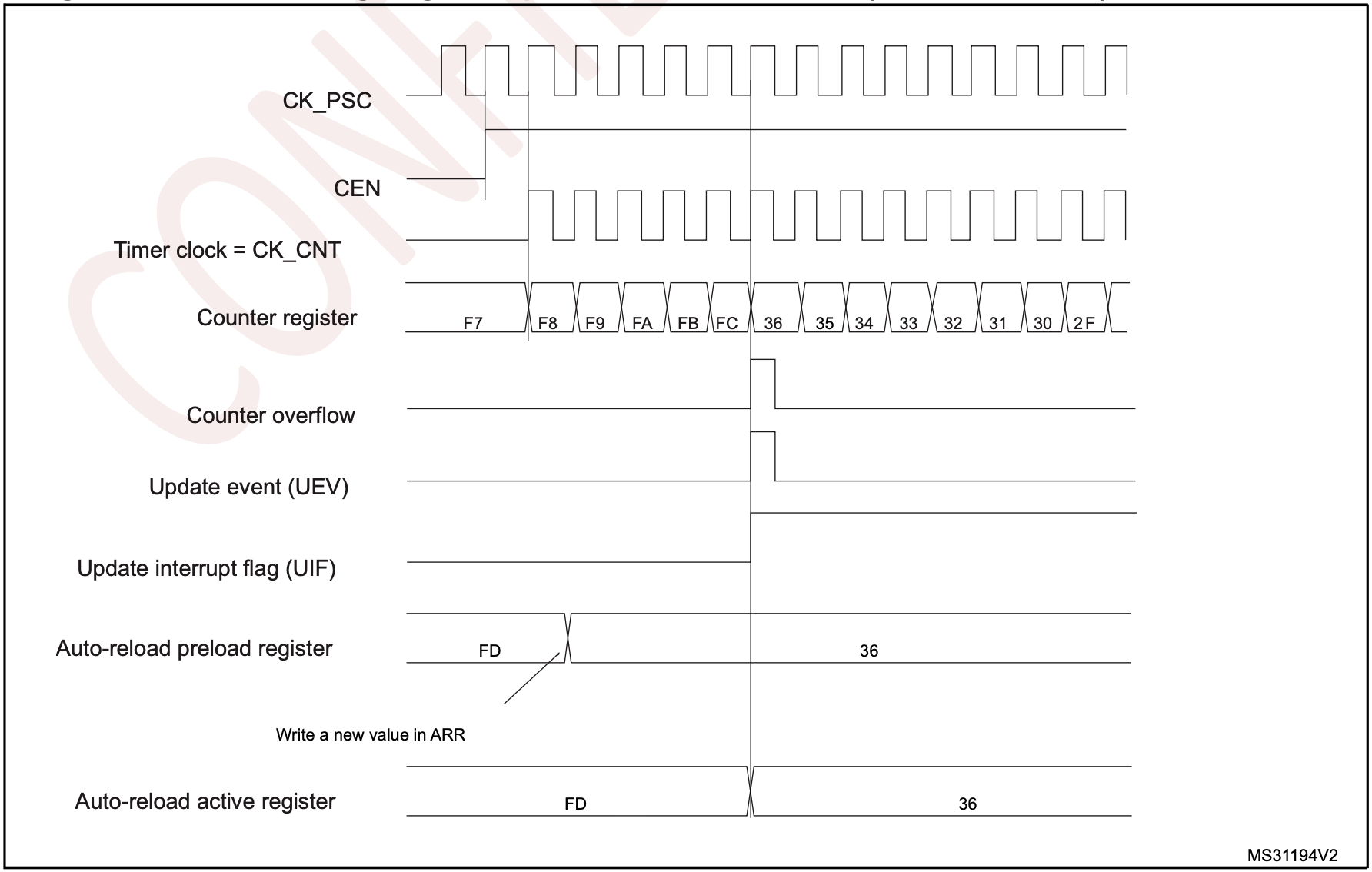

- 自动重装活动寄存器将被ARR寄存器的预装值更新。注意:自动重装寄存器会在计数器重载之前更新,从而确保下一周期是预期值。

💡 后续图示展示了在不同时钟频率下,当ARR=0x36时计数器的行为示例。

图 10. 计数器时序图,内部时钟除以 1

图 11. 计数器时序图,内部时钟除以 2

图 12. 计数器时序图,内部时钟除以 4

图 13. 计数器时序图,内部时钟除以 N

图 14. 计数器时序图,未使用重复计数器时的更新事件

中心对齐模式(向上/向下计数)¶

在中心对齐模式下,计数器从 0 计数到自动重载值(ARR 寄存器的内容)减去 1,产生计数器溢出事件,然后从自动重载值向下计数到 1,产生计数器下溢事件。然后,计数器重新从 0 开始计数。

当 CR1 寄存器中的 CMS 位不等于 '00' 时,中心对齐模式处于激活状态。配置为输出的通道的输出比较中断标志在以下情况下被置位:

- 计数器向下计数(中心对齐模式 1,CMS = "01")

- 计数器向上计数(中心对齐模式 2,CMS = "10")

- 计数器向上和向下计数(中心对齐模式 3,CMS = "11")

在此模式下,CR1 寄存器中的 DIR 方向位无法写入。它由硬件更新,并给出计数器的当前方向。

更新事件可以在每次计数器溢出和每次计数器下溢时产生,或者通过设置 EGR 寄存器中的 UG 位(通过软件或使用从模式控制器)也会产生更新事件。在这种情况下,计数器将重新从 0 开始计数,预分频器的计数器也会重新开始计数。

可以通过软件设置 CR1 寄存器中的 UDIS 位来禁用 UEV 更新事件。这是为了避免在写入新值到预装载寄存器时更新影像寄存器。此时,直到 UDIS 位被写入 0,更新事件才会发生。然而,计数器仍将根据当前的自动重载值继续上下计数。

此外,如果 CR1 寄存器中的 URS 位(更新请求选择)被设置,则设置 UG 位将生成 UEV 更新事件,但不会设置 UIF 标志(因此不会发送中断或 DMA 请求)。这是为了避免在捕获事件清除计数器时生成更新和捕获中断。

当发生更新事件时,所有寄存器将被更新,并且更新标志(SR 寄存器中的 UIF 位)将被置位(根据 URS 位的不同):

- 重复计数器被重新加载为 RCR 寄存器的内容

- 预分频器的缓冲区被重新加载为预装载值(PSC 寄存器的内容)

- 自动重载激活寄存器被更新为预装载值(ARR 寄存器的内容)。需要注意的是,如果更新源是计数器溢出,自动重载将在计数器重新加载之前更新,以确保下一个周期是预期的(计数器将加载新值)。

💡 以下图示展示了不同时钟频率下计数器行为的一些示例。

图 15. 计数器时序图,内部时钟除以 1,ARR = 0x6

图 16. 计数器时序图,内部时钟除以 2

图 17. 计数器时序图,内部时钟除以 4,ARR = 0x36

图 18. 计数器时序图,内部时钟除以 N

图 19. 计数器时序图,更新事件,当 ARPE = 1 时(计数器下溢)

图 20. 计数器时序图,更新事件,当 ARPE = 1 时(计数器溢出)

8.3.3 重复计数器¶

时间基准单元描述了如何根据计数器的溢出/下溢生成更新事件(UEV)。实际上,只有当重复计数器的值达到零时,更新事件才会被生成。这在生成 PWM 信号时非常有用。

这意味着数据将在每 N+1 次计数器溢出或下溢时从预装载寄存器传输到影像寄存器(ARR 自动重载寄存器、PSC 预分频器寄存器,还包括在比较模式下的 CCRx 捕获/比较寄存器),其中 N 是 RCR 重复计数器寄存器中的值。

重复计数器的值会在以下情况下递减:

- 在向上计数模式下的每次计数器溢出时

- 在向下计数模式下的每次计数器下溢时

- 在中心对齐模式下的每次计数器溢出和计数器下溢时

尽管这限制了最大重复次数为 128 个 PWM 周期,但它使得可以在每个 PWM 周期内更新两次占空比。在中心对齐模式下,每个 PWM 周期只刷新一次比较寄存器时,最大分辨率为 2xTck,这是由于模式的对称性。

重复计数器是自动重载类型;重复率保持为 RCR 寄存器值定义的值(参见图 21)。当更新事件由软件生成(通过设置 EGR 寄存器中的 UG 位)或通过从模式控制器硬件生成时,它会立即发生,无论重复计数器的值是多少,并且重复计数器将被重新加载为 RCR 寄存器的内容。

在中心对齐模式下,对于 RCR 的奇数值,更新事件要么在溢出时发生,要么在下溢时发生,具体取决于 RCR 寄存器何时写入以及计数器何时启动。如果在启动计数器之前写入 RCR,则 UEV 会在溢出时发生。如果在启动计数器之后写入 RCR,则 UEV 会在下溢时发生。例如,对于 RCR = 3,UEV 会在每第 4 次溢出或下溢事件中生成,具体取决于 RCR 是何时写入的。

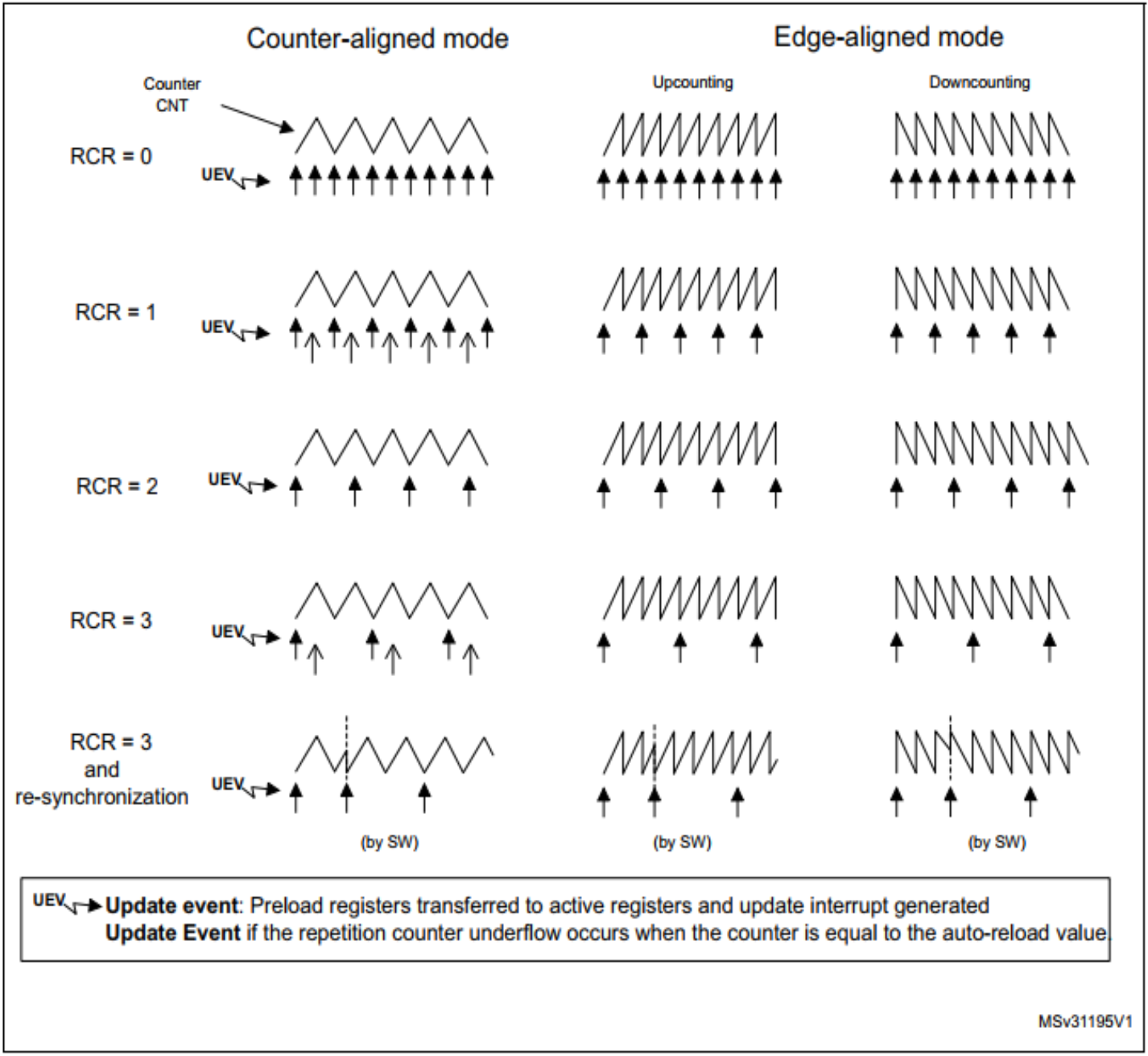

图 21. 根据模式和 RCR 寄存器设置的更新率示例

8.3.4 时钟选择¶

计数器时钟可以由以下时钟源提供:

- 内部时钟(CK_INT)

- 外部时钟模式1:外部输入引脚

- 外部时钟模式2:外部触发输入 ETR

- 内部触发输入(ITRx):使用一个定时器作为另一个定时器的预分频器,例如,用户可以配置定时器 1 作为定时器 2 的预分频器。有关更多详细信息,请参见“使用一个定时器作为另一个定时器的预分频器”。

内部时钟源(CK_INT)¶

如果从模式控制器被禁用(SMS=000),则 CEN、DIR(在 CR1 寄存器中)和 UG 位(在 EGR 寄存器中)为实际控制位,且只能通过软件更改(除非 UG 位,它会自动被清除)。一旦 CEN 位被写入 1,预分频器就会由内部时钟 CK_INT 驱动。

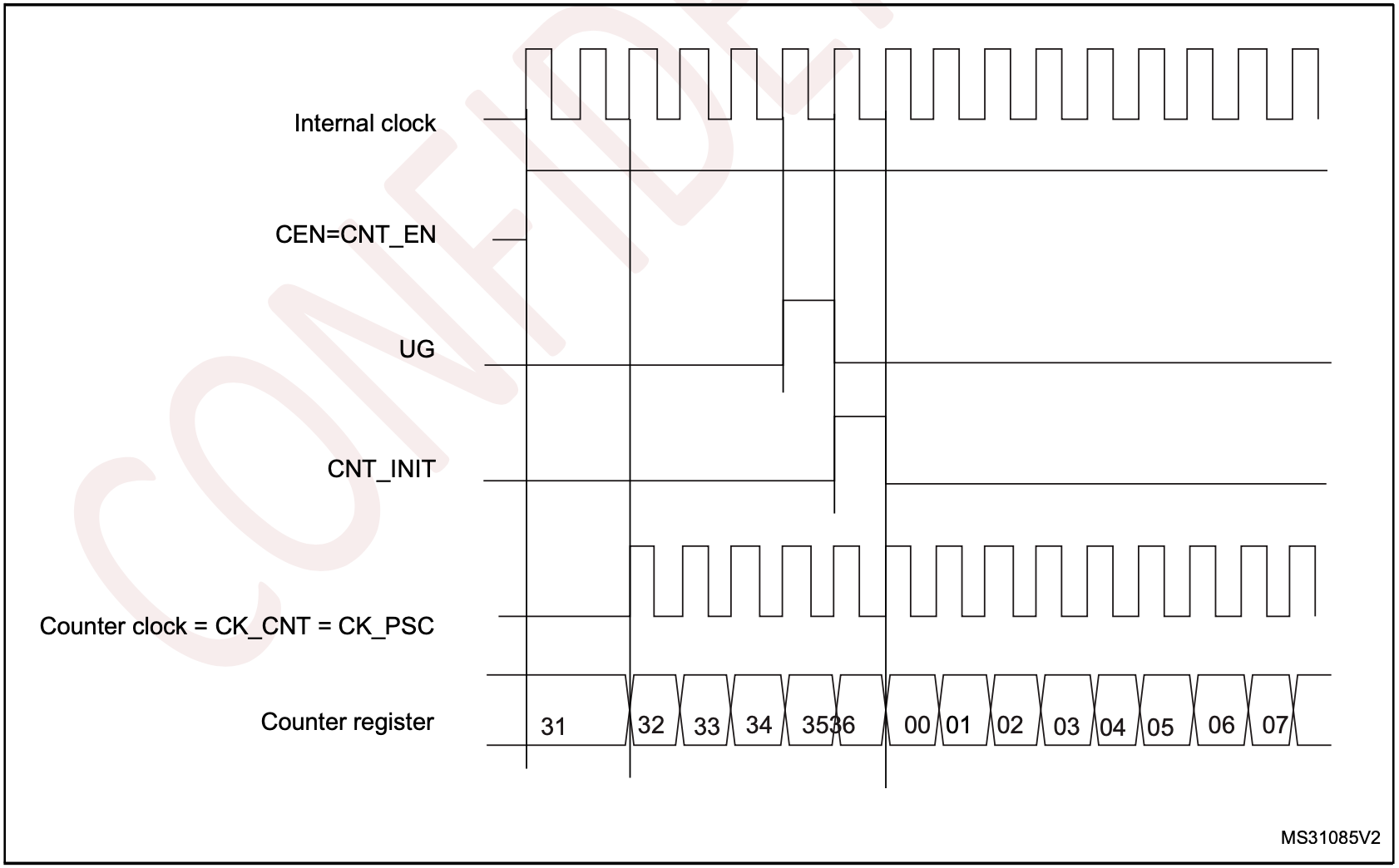

💡 图 22 显示了在正常模式下,无预分频器时控制电路和向上计数器的行为。

图 22. 正常模式下的控制电路,内部时钟除以 1

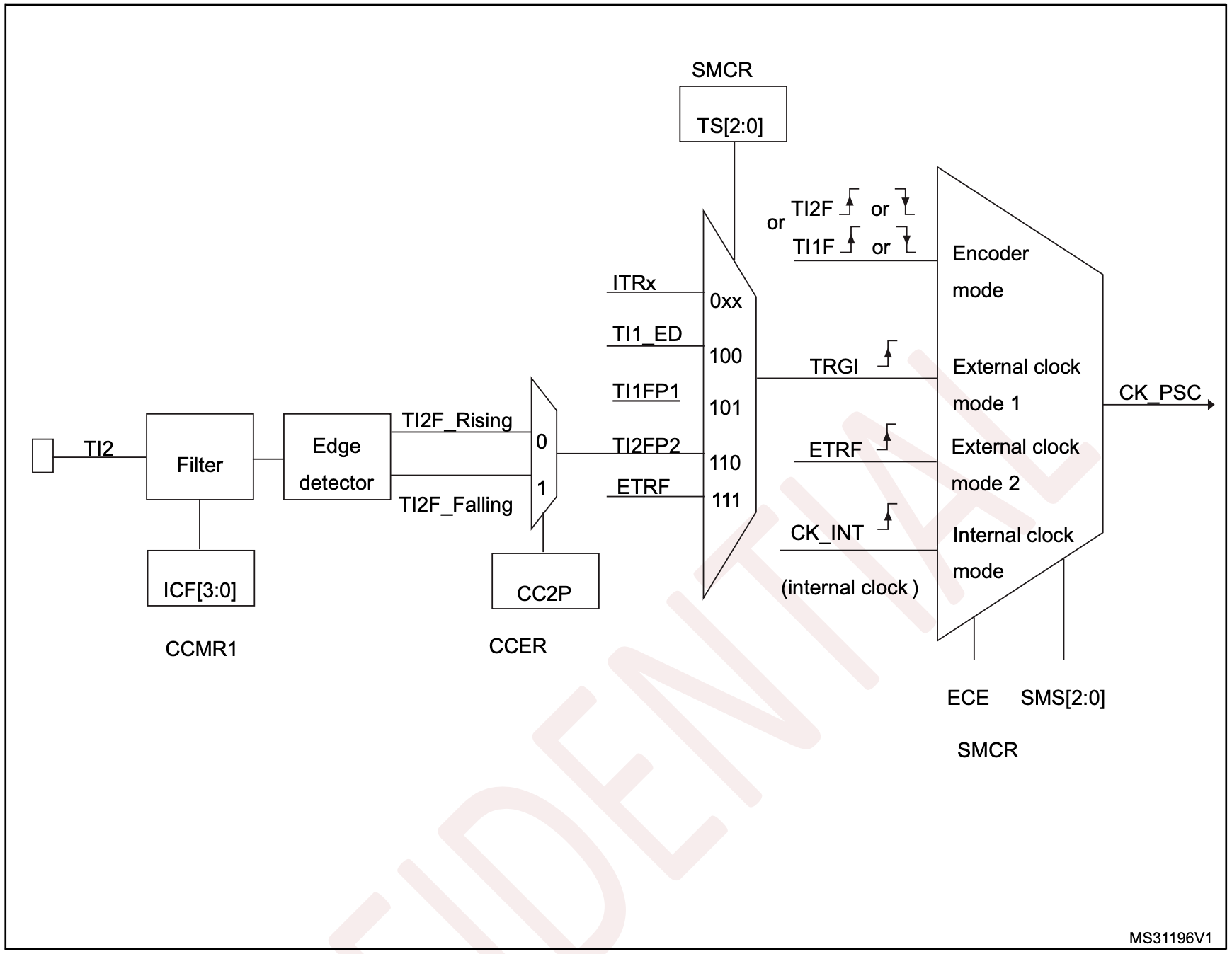

外部时钟源模式 1¶

当 SMCR 寄存器中的 SMS=111 时,选择此模式。计数器可以在选定输入的每个上升沿或下降沿进行计数。

图 23. TI2 外部时钟连接示例

注意:例如,要配置向上计数器以响应 TI2 输入的上升沿进行计数,请按照以下步骤操作:

- 通过在 CCMR1 寄存器中写入 CC2S = ‘01’,配置通道 1 以检测 TI2 输入的上升沿。

- 通过在 CCMR1 寄存器中写入 IC2F[3:0] 位来配置输入滤波器持续时间(如果不需要滤波器,则保持 IC2F=0000)。

- 通过在 CCER 寄存器中写入 CC2P=0,选择上升沿极性。

- 通过在 SMCR 寄存器中写入 SMS=111,配置定时器为外部时钟模式 1。

- 通过在 SMCR 寄存器中写入 TS=110,选择 TI2 作为触发输入源。

- 通过在 CR1 寄存器中写入 CEN=1,启用计数器。

捕获预分频器不用于触发,因此用户不需要配置它。

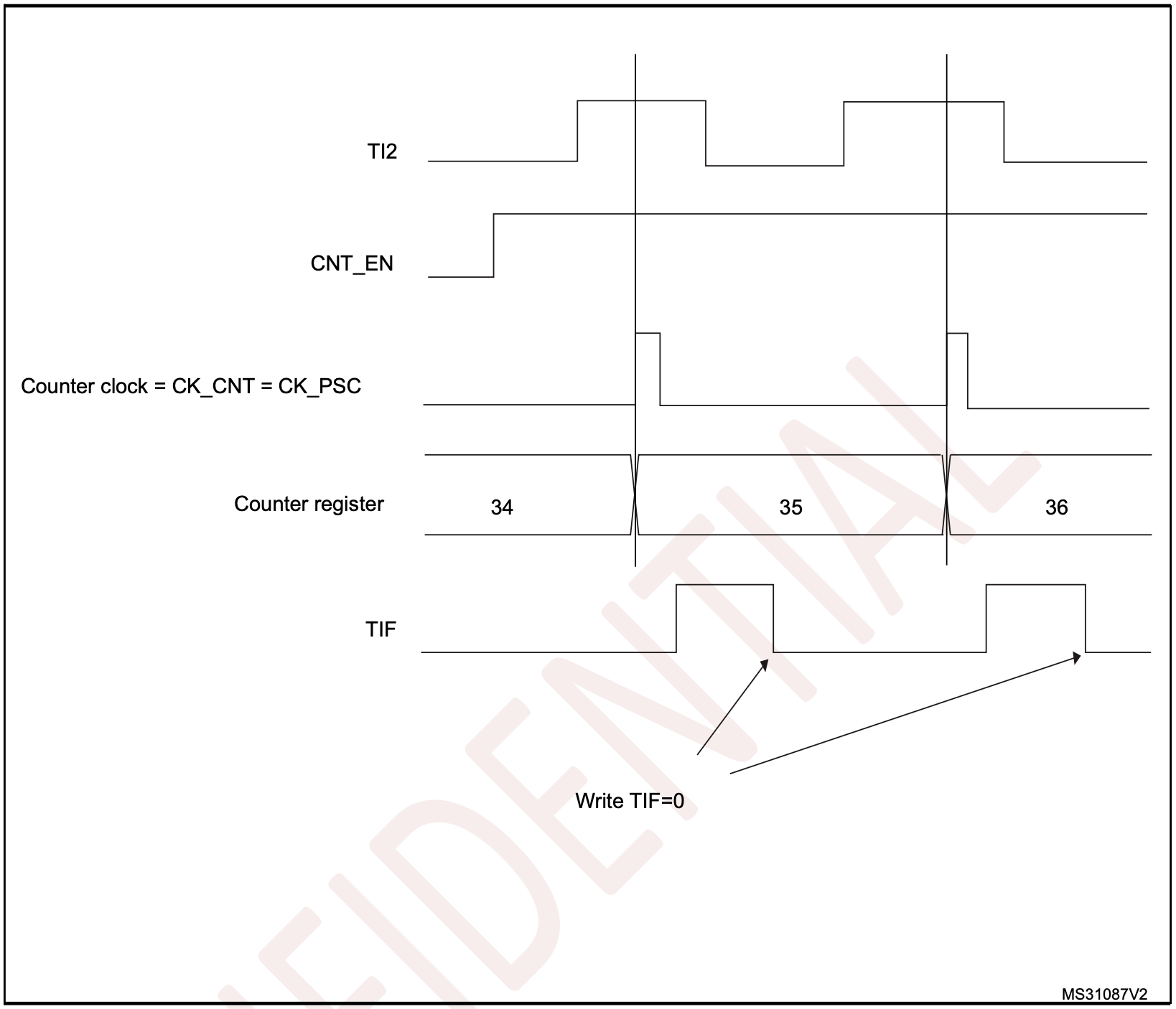

当 TI2 上发生上升沿时,计数器计数一次,并设置 TIF 标志。

TI2 上的上升沿与计数器的实际时钟之间的延迟是由于 TI2 输入的重同步电路。

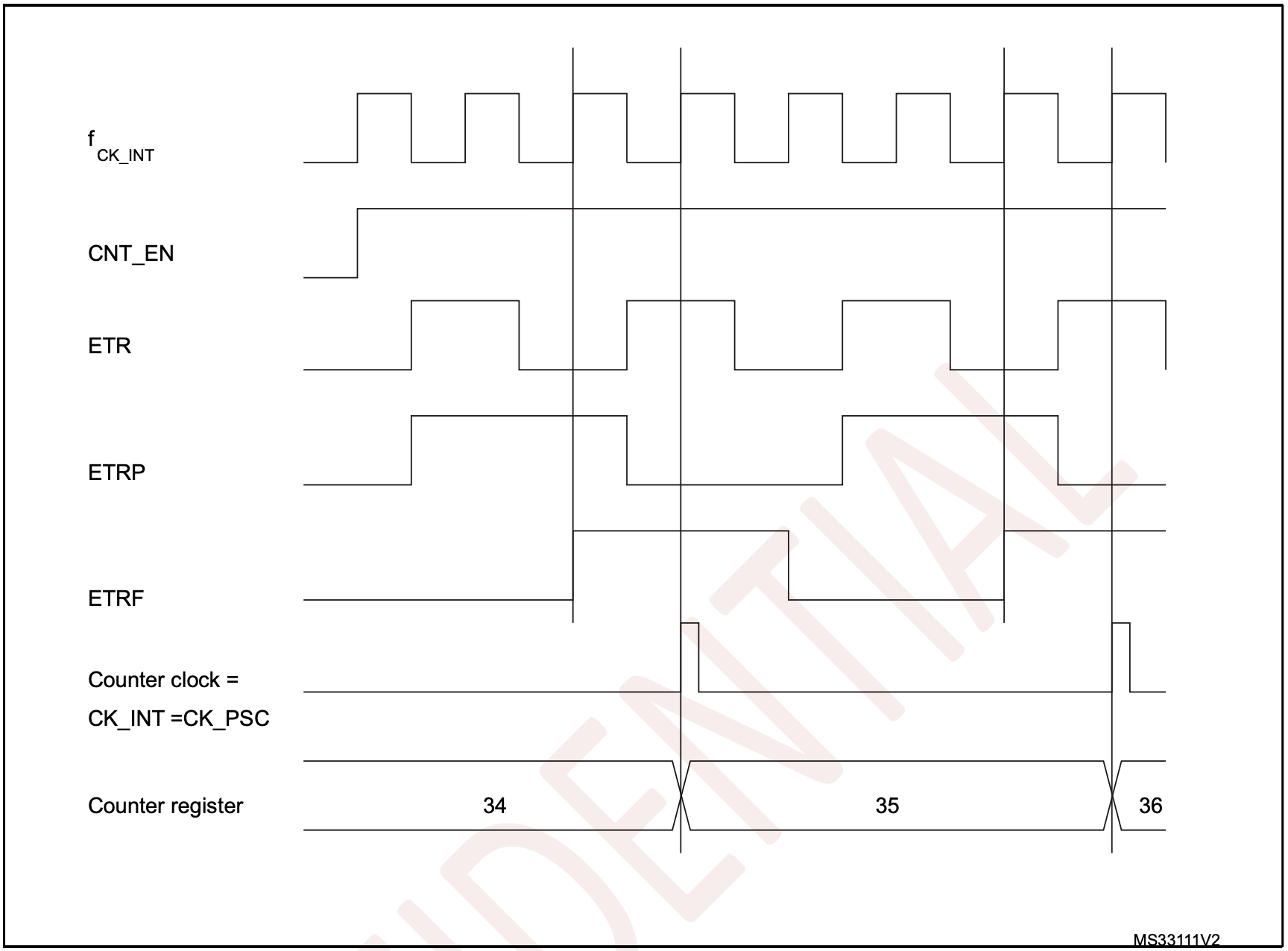

图 24. 外部时钟模式 1 下的控制电路

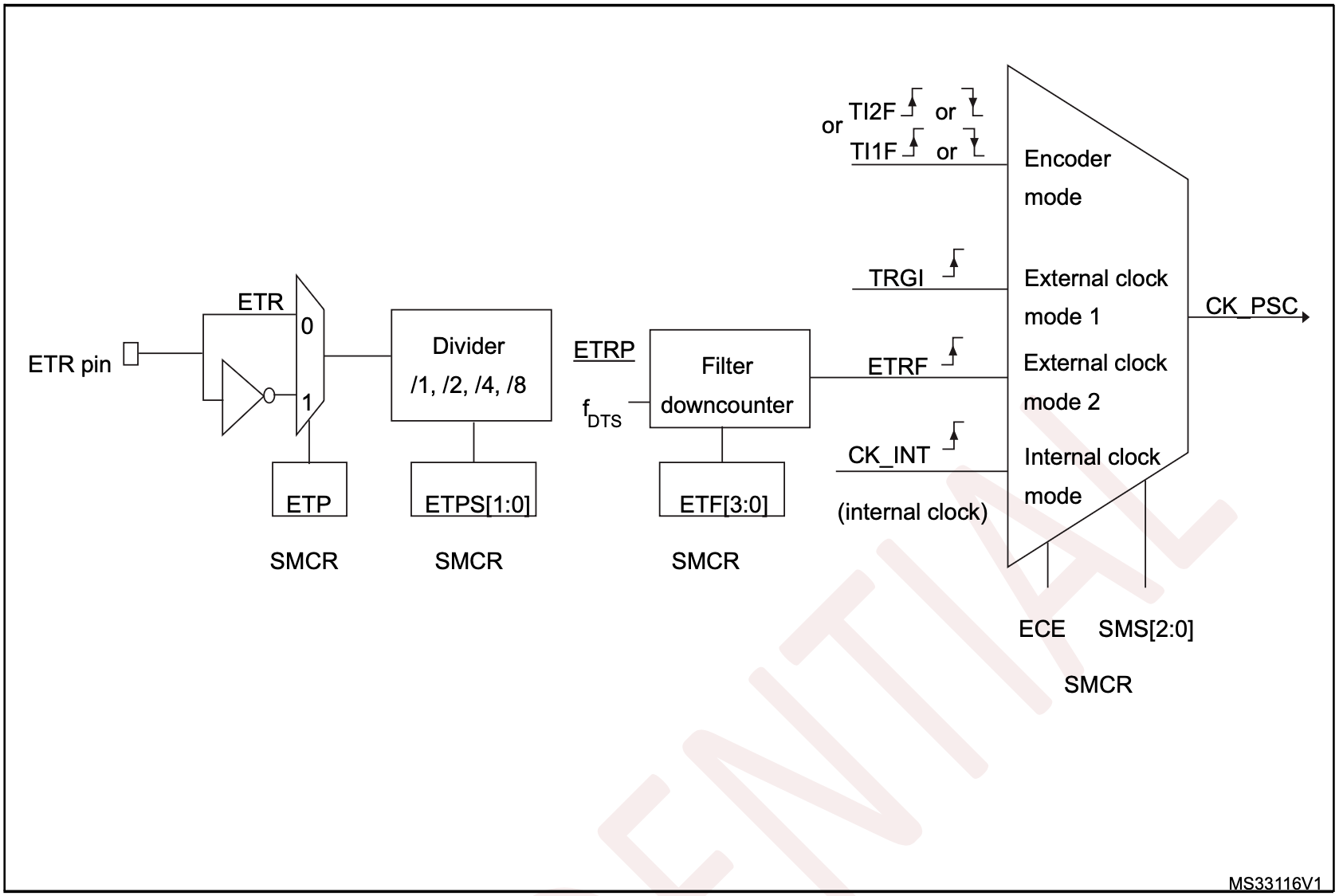

外部时钟源模式 2¶

通过在 SMCR 寄存器中写入 ECE=1 来选择此模式。计数器可以在外部触发输入 ETR 的每个上升沿或下降沿进行计数。

图 25 给出了外部触发输入块的概述。

图 25. 外部触发输入块

例如,要配置向上计数器以在每 2 个 ETR 上升沿上进行计数,请按照以下步骤操作:

- 由于在此示例中不需要滤波器,在 SMCR 寄存器中写入 ETF[3:0]=0000。

- 通过在 SMCR 寄存器中写入 ETPS[1:0]=01 来设置预分频器。

- 通过在 SMCR 寄存器中写入 ETP=0,选择 ETR 引脚上的上升沿检测。

- 通过在 SMCR 寄存器中写入 ECE=1,启用外部时钟模式 2。

- 通过在 CR1 寄存器中写入 CEN=1,启用计数器。

计数器在每 2 个 ETR 上升沿时计数一次。

ETR 上的上升沿与计数器的实际时钟之间的延迟是由于 ETRP 信号上的重同步电路。

图 26. 外部时钟模式 2 下的控制电路

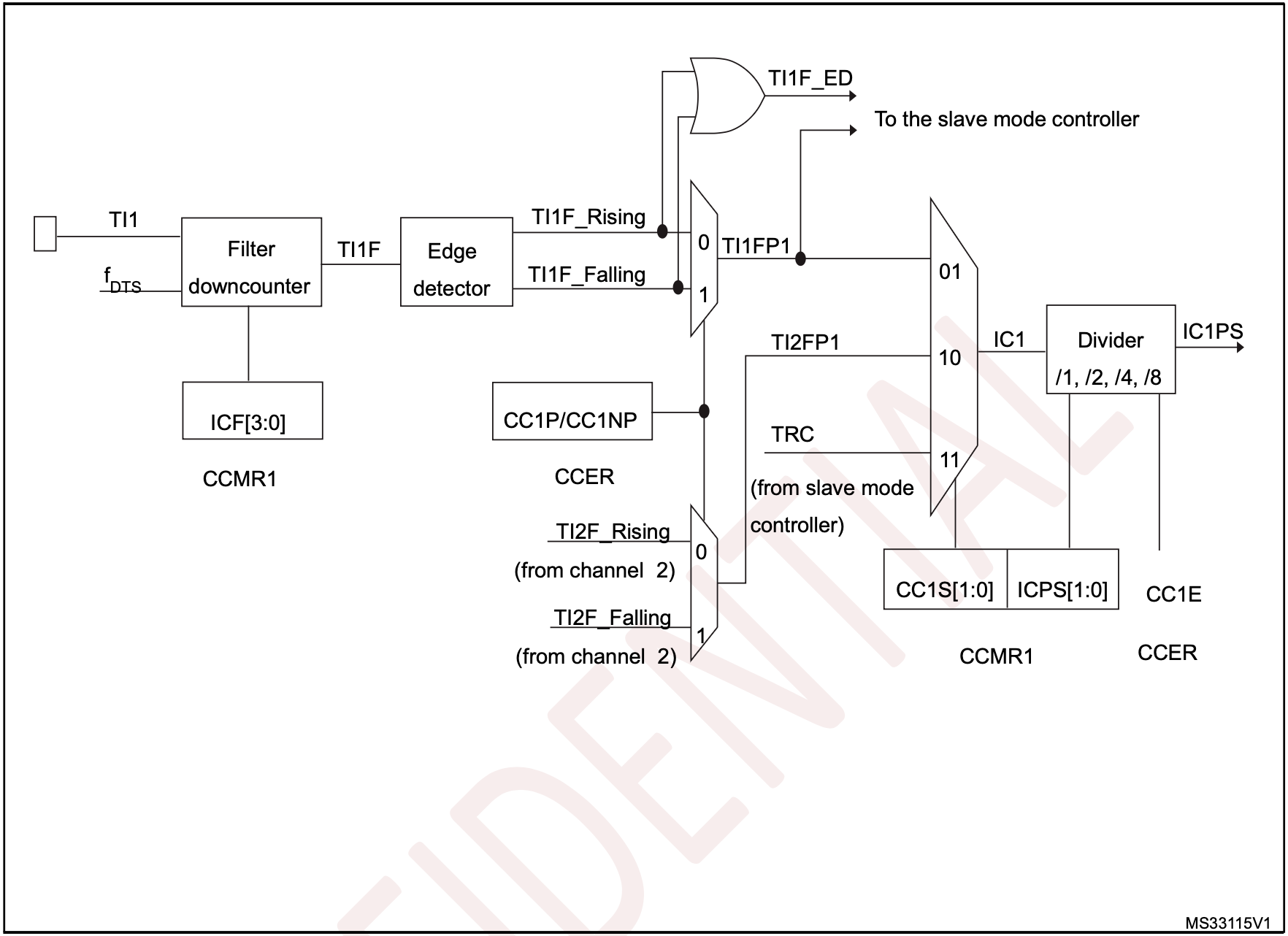

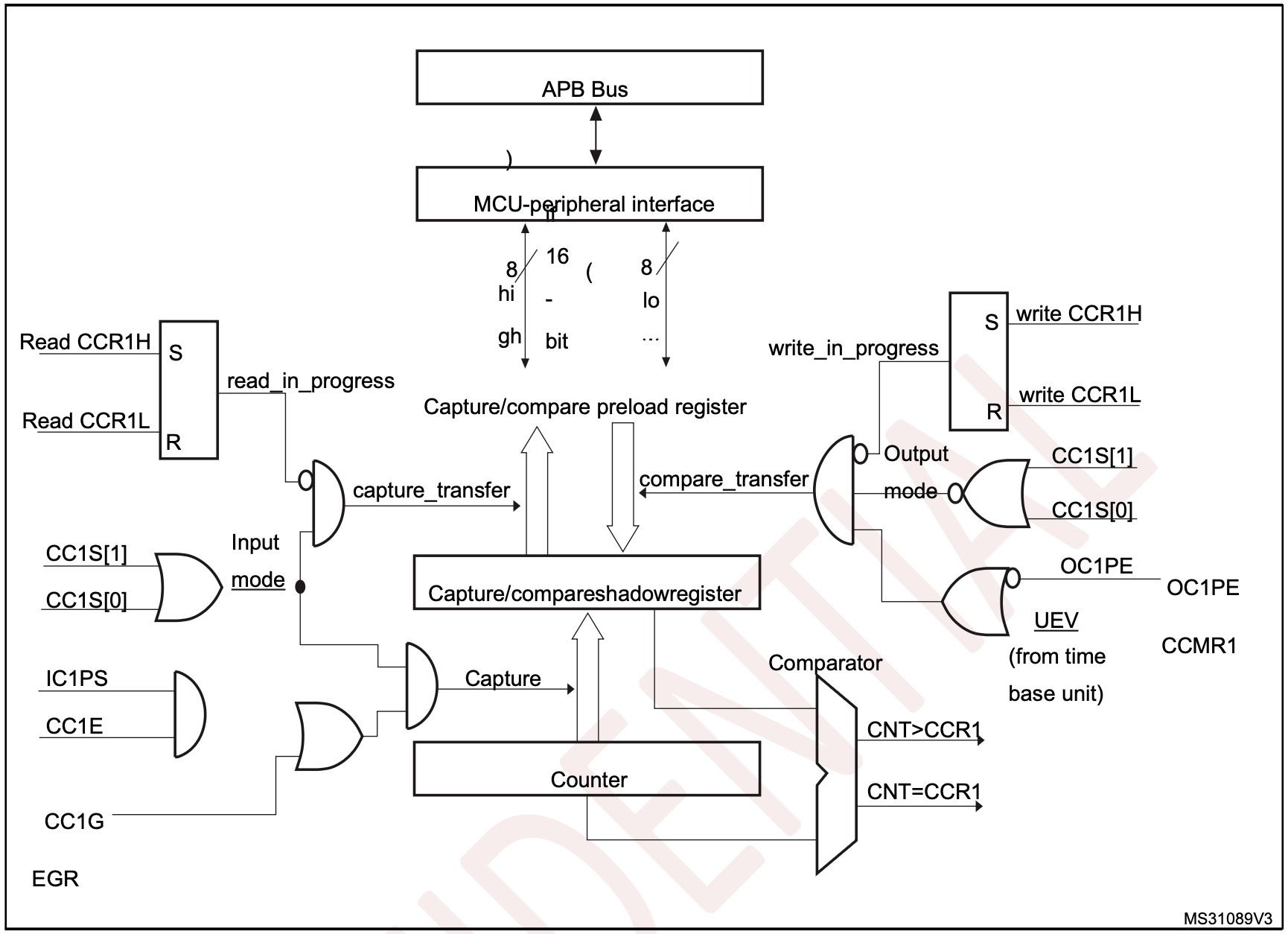

8.3.5 捕获/比较通道¶

每个捕获/比较通道由一个捕获/比较寄存器(包括影像寄存器)、一个用于捕获的输入阶段(带有数字滤波器、多路复用和预分频器)以及一个输出阶段(带有比较器和输出控制)组成。

图 27 到图 30 给出了一个捕获/比较通道的概述。

输入阶段对相应的 TIx 输入进行采样,以生成滤波后的信号 TIxF。然后,带有极性选择的边缘检测器生成一个信号(TIxFPx),该信号可用作从模式控制器的触发输入或作为捕获命令。在捕获寄存器之前进行预分频(ICxPS)。

图 27. 捕获/比较通道(示例:通道 0 输入阶段)

输出阶段生成一个中间波形,然后用作参考: OCxRef(有效高)。极性在链条的末端起作用。

图 28. 捕获/比较通道 0 主电路

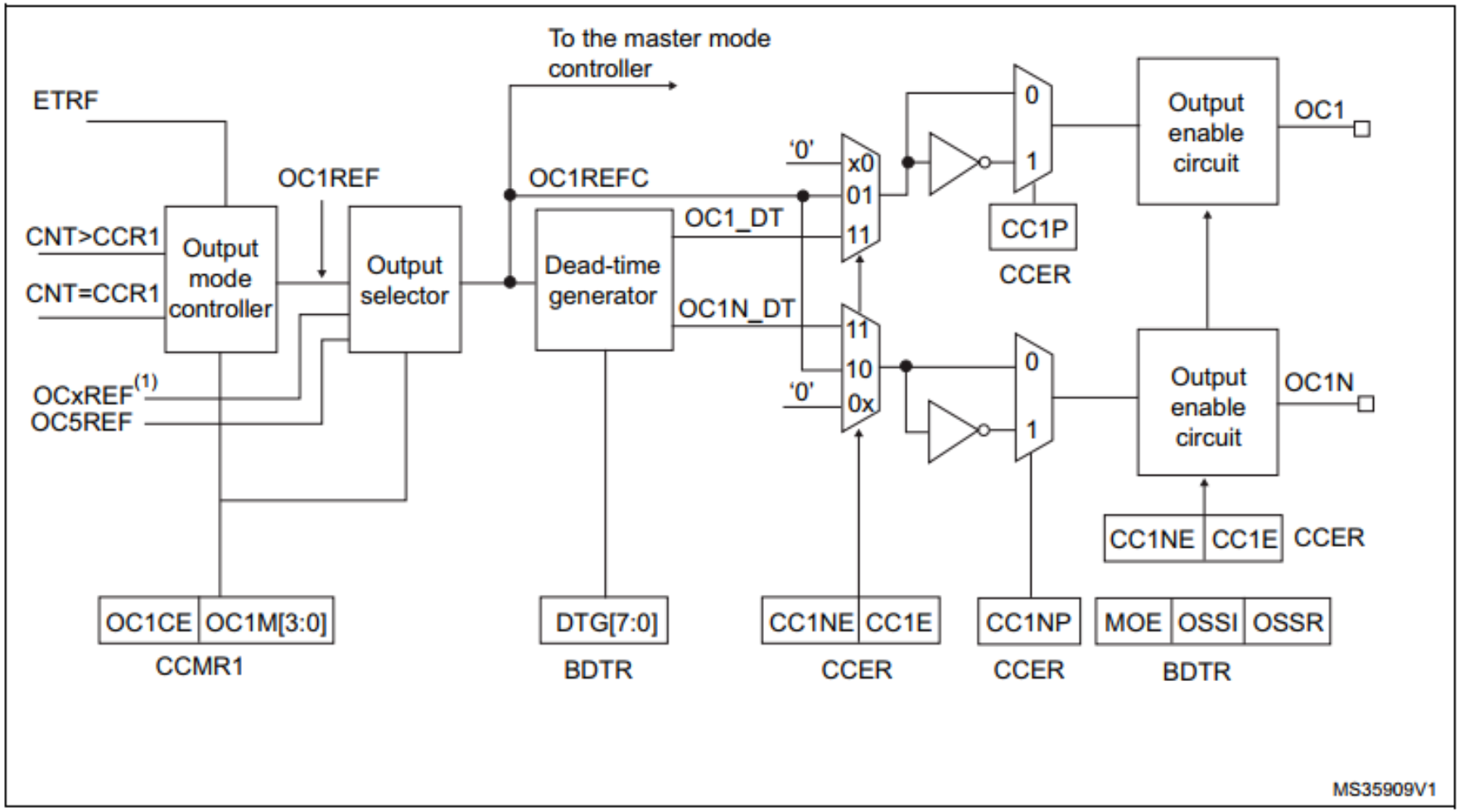

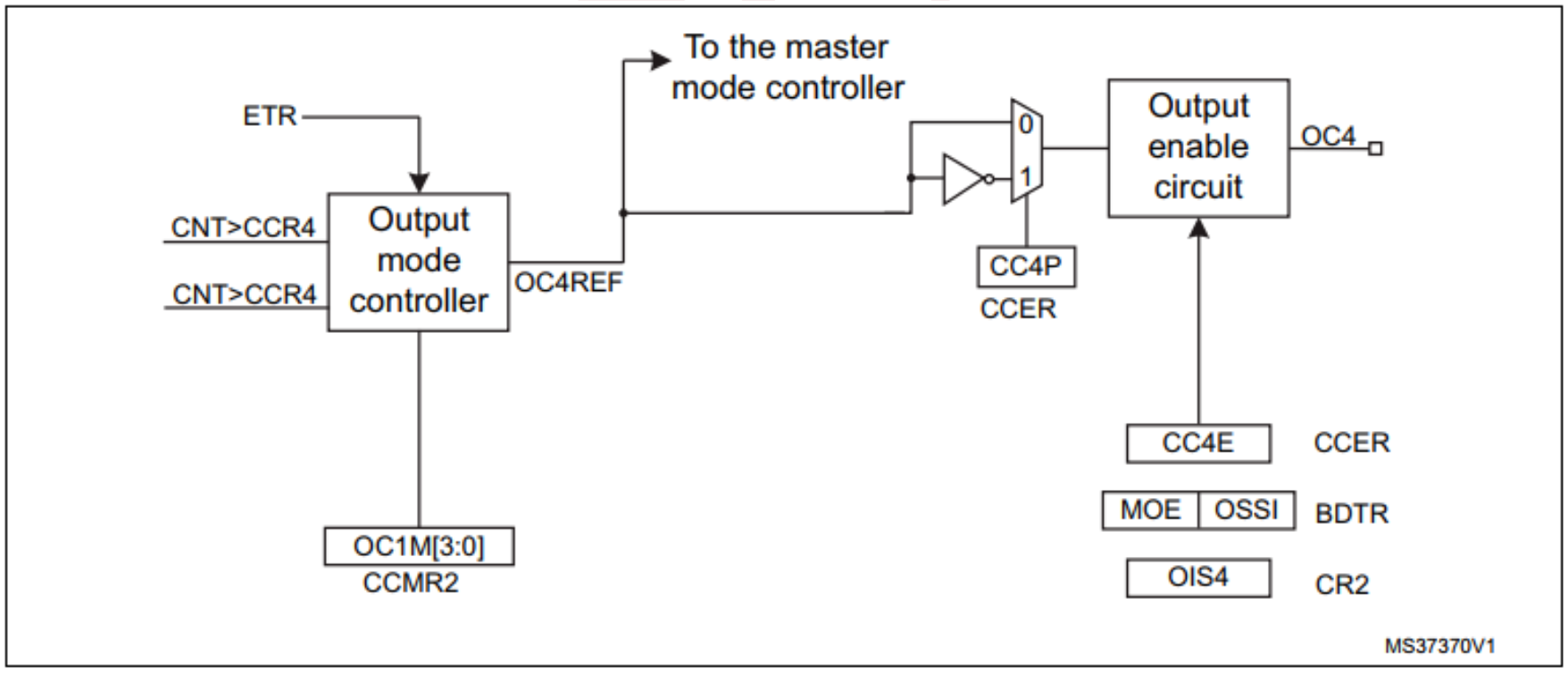

图 29. 捕获/比较通道的输出阶段(通道 1 至 3)

图 30. 捕获/比较通道的输出阶段(通道 4)

捕获/比较模块由一个预装载寄存器和一个影像寄存器组成。写入和读取始终访问预装载寄存器。

在捕获模式下,捕获实际上发生在影像寄存器中,捕获内容被复制到预装载寄存器。

在比较模式下,预装载寄存器的内容被复制到影像寄存器中,并与计数器进行比较。

8.3.6 输入捕获模式¶

在输入捕获模式下,捕获/比较寄存器(CCRx)用于在检测到相应的 ICx 信号过渡后锁存计数器的值。当捕获发生时,相应的 CCXIF 标志(SR 寄存器)会被置位,并且如果启用了中断或 DMA 请求,可以发送它们。如果在 CCxIF 标志已经为高时发生捕获,则会设置溢出捕获标志 CCxOF(SR 寄存器)。可以通过软件将 CCxIF 写为 '0' 或读取存储在 CCRx 寄存器中的捕获数据来清除 CCxIF。写入 '0' 时,CCxOF 被清除。

以下示例展示了如何在 TI1 输入上升沿时捕获 CCR1 中的计数器值。为此,请按照以下步骤操作:

- 选择有效输入:CCR1 必须连接到 TI1 输入,因此在 CCMR1 寄存器中将 CC1S 位写为 01。只要 CC1S 不再为 00,通道就会配置为输入,CCR1 寄存器变为只读。

- 根据连接到定时器的信号编程所需的输入滤波器持续时间(如果输入是 TIx 输入,则在 CCMRx 寄存器中编程 ICxF 位)。假设在翻转时,输入信号在至少五个内部时钟周期内不稳定。我们必须编程一个比这五个时钟周期更长的滤波持续时间。我们可以在检测到 8 个连续的样本后确认 TI1 上的过渡(以 fDTS 频率采样)。然后在 CCMR1 寄存器中将 IC1F 位写为 0011。

- 通过在 CCER 寄存器中写入 CC1P 位为 0(此时为上升沿),选择 TI1 通道的有效过渡边缘。

- 编程输入预分频器。在我们的示例中,我们希望在每个有效过渡时执行捕获,因此禁用预分频器(在 CCMR1 寄存器中将 IC1PS 位写为 ‘00’)。

- 通过在 CCER 寄存器中设置 CC1E 位启用从计数器到捕获寄存器的捕获。

- 如果需要,通过在 DIER 寄存器中设置 CC1IE 位启用相关的中断请求,和/或通过在 DIER 寄存器中设置 CC1DE 位启用 DMA 请求。

当发生输入捕获时:

- CCR1 寄存器将获得计数器在有效过渡时的值。

- CC1IF 标志被置位(中断标志)。如果至少发生了两个连续的捕获且标志未被清除,CC1OF 也会被置位。

- 根据 CC1IE 位生成中断。

- 根据 CC1DE 位生成 DMA 请求。

为了处理溢出捕获,建议在溢出捕获标志之前读取数据。这样可以避免在读取标志后和读取数据之前错过溢出捕获。

注意:可以通过软件设置相应的 CCxG 位在 EGR 寄存器中生成 IC 中断和/或 DMA 请求。

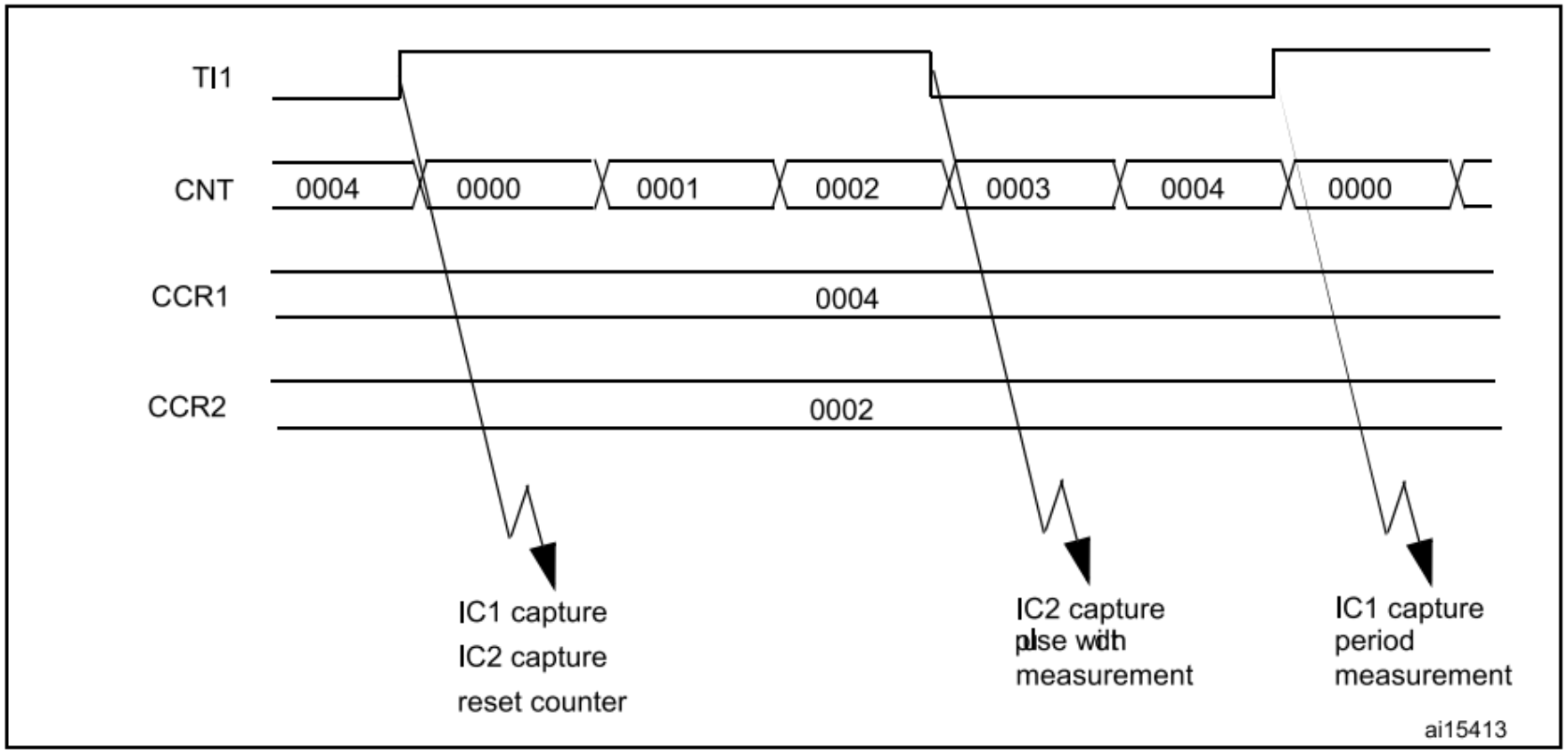

8.3.7 PWM 输入模式¶

此模式是输入捕获模式的一个特殊情况。步骤与输入捕获模式相同,区别如下:

- 两个 ICx 信号映射到同一个 TIx 输入。

- 这两个 ICx 信号在具有相反极性的边缘上处于激活状态。

- 选择其中一个 TIxFP 信号作为触发输入,并将从模式控制器配置为复位模式。

例如,用户可以使用以下步骤测量应用于 TI1 上的 PWM 的周期(存储在 CCR1 寄存器中)和占空比(存储在 CCR2 寄存器中)(取决于 CK_INT 频率和预分频器值):

- 选择 CCR1 的有效输入:在 CCMR1 寄存器中将 CC1S 位写为 01(选择 TI1)。

- 选择 TI1FP1 的有效极性(用于 CCR1 中的捕获和计数器清除):将 CC1P 位写为 ‘0’(在上升沿有效)。

- 选择 CCR2 的有效输入:在 CCMR1 寄存器中将 CC2S 位写为 10(选择 TI1)。

- 选择 TI1FP2 的有效极性(用于 CCR2 中的捕获):将 CC2P 位写为 ‘1’(在下降沿有效)。

- 选择有效的触发输入:在 SMCR 寄存器中将 TS 位写为 101(选择 TI1FP1)。

- 将从模式控制器配置为复位模式:在 SMCR 寄存器中将 SMS 位写为 100。

- 启用捕获:在 CCER 寄存器中将 CC1E 和 CC2E 位写为 ‘1’。

图 31. PWM 输入模式时序

- 由于仅有 TI1FP1 和 TI2FP2 连接到从模式控制器,因此 PWM 输入模式只能与 CH1/CH2 信号一起使用。

8.3.8 强制输出模式¶

在输出模式下(CCxS 位在 CCMRx 寄存器中设置为 00),每个输出比较信号(OCxREF 然后是 OCx/OCxN)可以通过软件直接强制为激活或非激活状态,独立于输出比较寄存器与计数器之间的任何比较。

要强制将输出比较信号(OCxREF/OCx)设为激活状态,用户只需要在相应的 CCMRx 寄存器中将 OCxM 位写为 101。因此,OCxREF 会被强制为高电平(OCxREF 始终为有效高),并且 OCx 的值与 CCxP 极性位相反。

例如:CCxP=0(OCx 有效高)=> OCx 被强制为高电平。

通过在 CCMRx 寄存器中将 OCxM 位写为 100,可以将 OCxREF 信号强制为低电平。

无论如何,CCRx 影像寄存器与计数器之间的比较仍然会进行,并允许设置标志。中断和 DMA 请求可以相应地发送。这将在下面的输出比较模式部分中描述。

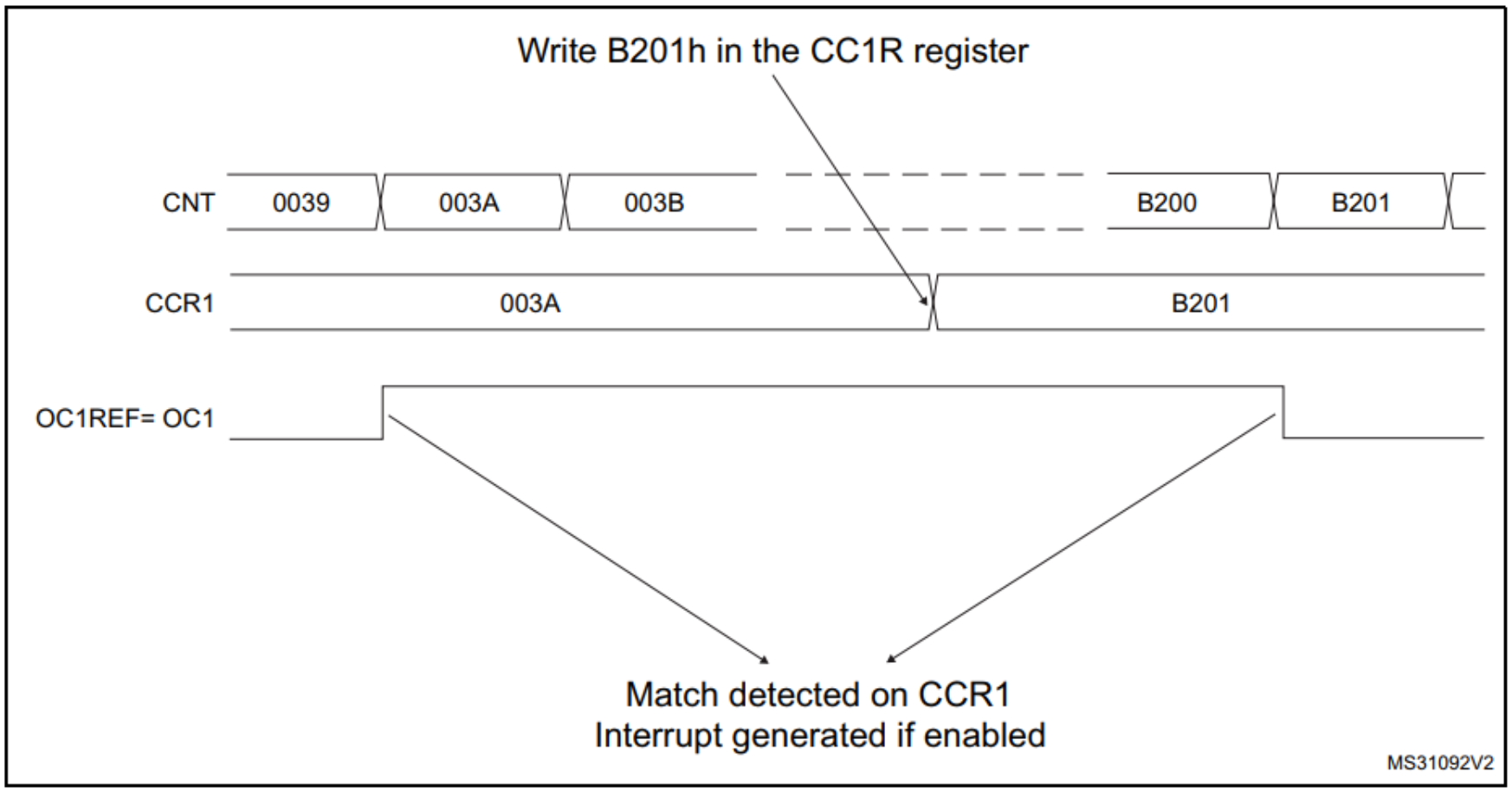

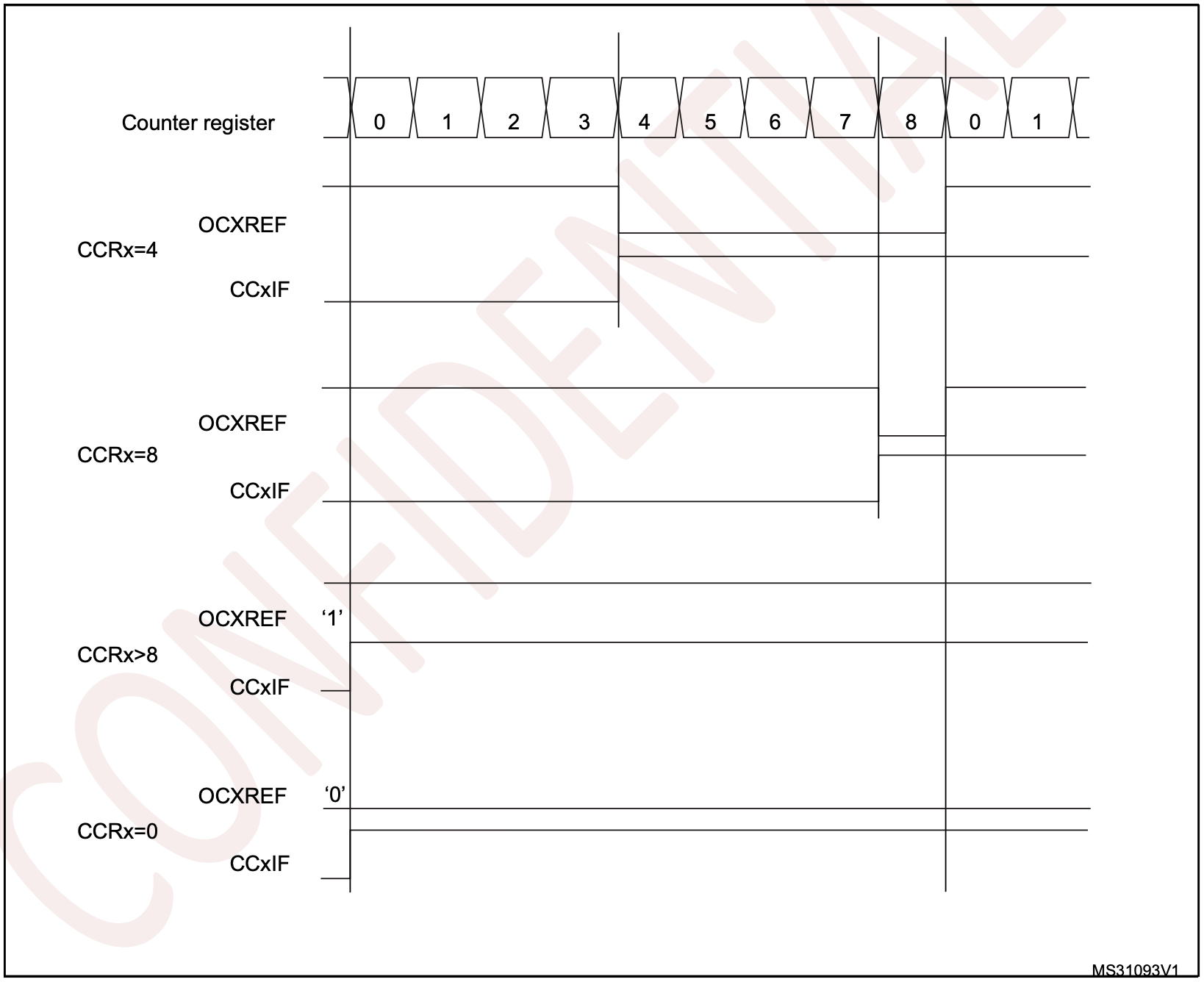

8.3.9 输出比较模式¶

此功能用于控制输出波形或指示某段时间已过去。

当捕获/比较寄存器与计数器匹配时,输出比较功能:

- 将相应的输出引脚分配为由输出比较模式(CCxM 位在 CCMRx 寄存器中)和输出极性(CCxP 位在 CCER 寄存器中)定义的可编程值。输出引脚可以保持其电平(OCxM=000)、设为激活状态(OCxM=001)、设为非激活状态(OCxM=010)或在匹配时切换(OCxM=011)。

- 在中断状态寄存器中设置标志(SR 寄存器中的 CCxIF 位)。

- 如果相应的中断掩码被设置,则生成中断(DIER 寄存器中的 CCxIE 位)。

- 如果相应的启用位被设置,则发送 DMA 请求(DIER 寄存器中的 CCxDE 位,CR2 寄存器中的 CCDS 位用于 DMA 请求选择)。

CCRx 寄存器可以通过 CCMRx 寄存器中的 OCxPE 位进行编程,决定是否使用预装载寄存器。

在输出比较模式下,更新事件 UEV 对 OCxREF 和 OCx 输出没有影响。

计时分辨率为计数器的一个计数。输出比较模式还可以用于输出单个脉冲(在单脉冲模式下)。

操作步骤:

- 选择计数器时钟(内部、外部、预分频器)。

- 在 ARR 和 CCRx 寄存器中写入所需数据。

- 如果要生成中断请求,则设置 CCxIE 位。

-

选择输出模式。例如:

- 写 OCxM = 011,当 CNT 与 CCRx 匹配时切换 OCx 输出引脚。

- 写 OCxPE = 0 禁用预装载寄存器 – 高极性。

- 写 CCxE = 1 启用输出。

- 写 CCxP = 0 选择激活。

-

通过在 CR1 寄存器中设置 CEN 位启用计数器。

只要预装载寄存器未启用(OCxPE = '0',否则只有在下一个更新事件 UEV 时才会更新 CCRx 影像寄存器),CCRx 寄存器可以随时由软件更新,以控制输出波形。图 32 给出了一个示例。

图 32. 输出比较模式,在 OC1 上切换。

8.3.10 PWM 模式¶

脉宽调制(PWM)模式允许生成一个频率由 ARR 寄存器的值决定、占空比由 CCRx 寄存器的值决定的信号。

PWM 模式可以通过在 CCMRx 寄存器中的 OCxM 位写入 ‘110’(PWM 模式 1)或 ‘111’(PWM 模式 2)独立地选择在每个通道上(每个 OCx 输出一个 PWM)。相应的预装载寄存器必须通过在 CCMRx 寄存器中设置 OCxPE 位来启用,最终通过在 CR1 寄存器中设置 ARPE 位来启用自动重装载预装载寄存器(在向上计数或中心对齐模式下)。

由于预装载寄存器仅在更新事件发生时才会传输到影像寄存器,因此在启动计数器之前,用户必须通过在 EGR 寄存器中设置 UG 位来初始化所有寄存器。

OCx 极性可以通过 CCxP 位在 CCER 寄存器中进行软件编程。它可以编程为有效高或有效低。OCx 输出通过 CCxE、CCxNE、MOE、OSSI 和 OSSR 位的组合(CCER 和 BDTR 寄存器)启用。有关更多详细信息,请参阅 CCER 寄存器的描述。

在 PWM 模式(1 或 2)下,CNT 和 CCRx 始终进行比较,以确定是 CCRx < CNT 还是 CNT < CCRx(取决于计数器的方向)。

定时器能够在边缘对齐模式或中心对齐模式下生成 PWM,具体取决于 CR1 寄存器中的 CMS 位。

PWM 边缘对齐模式¶

向上计数配置

当 CR1 寄存器中的 DIR 位为低时,向上计数模式是激活的。请参阅向上计数模式。

在以下示例中,我们考虑 PWM 模式 1。参考 PWM 信号 OCxREF 在 CNT < CCRx 时为高,否则变为低。如果 CCRx 中的比较值大于自动重装载值(在 ARR 中),则 OCxREF 保持为 ‘1’。如果比较值为 0,则 OCxREF 保持为 ‘0’。图 33 显示了一个 ARR=8 的边缘对齐 PWM 波形示例。

图 33. 边缘对齐 PWM 波形(ARR=8)

向下计数配置

当 CR1 寄存器中的 DIR 位为高时,向下计数模式是激活的。请参阅向下计数模式。

在 PWM 模式 1 中,参考信号 OCxREF 在 CNT > CCRx 时为低,否则变为高。如果 CCRx 中的比较值大于 ARR 中的自动重装载值,则 OCxREF 保持为 ‘1’。在此模式下,0% PWM 是不可用的。

PWM 中心对齐模式¶

当 CR1 寄存器中的 CMS 位不等于 ‘00’ 时,中心对齐模式激活(其余配置对 OCxRef/OCx 信号有相同效果)。根据 CMS 位的配置,计数器在向上计数、向下计数或上下计数时都会设置比较标志。CR1 寄存器中的方向位(DIR)由硬件更新,不能由软件更改。请参阅中心对齐模式(向上/向下计数)。

图 34 显示了一个 ARR=8 的中心对齐 PWM 波形示例,其中:

- ARR=8,

- PWM 模式为 PWM 模式 1,

- 选择了 CMS=01 的中心对齐模式 1 时,当计数器向下计数时设置标志。

图 34. 中心对齐 PWM 波形(ARR=8)

使用中心对齐模式的提示:

- 当启动中心对齐模式时,将使用当前的向上/向下配置。这意味着计数器根据 CR1 寄存器中 DIR 位的值向上或向下计数。此外,DIR 和 CMS 位不能同时由软件更改。

-

在运行中心对齐模式时,建议不要写入计数器,因为这可能导致意外结果。特别是:

- 如果用户写入计数器的值大于自动重装载值(CNT > ARR),则方向不会更新。例如,如果计数器正在向上计数,它将继续向上计数。

- 如果用户写入 0 或将 ARR 值写入计数器,则方向会更新,但不会生成更新事件(UEV)。

-

使用中心对齐模式的最安全方法是在启动计数器之前通过软件生成一次更新(在 EGR 寄存器中设置 UG 位),并且不要在计数器运行时写入计数器。

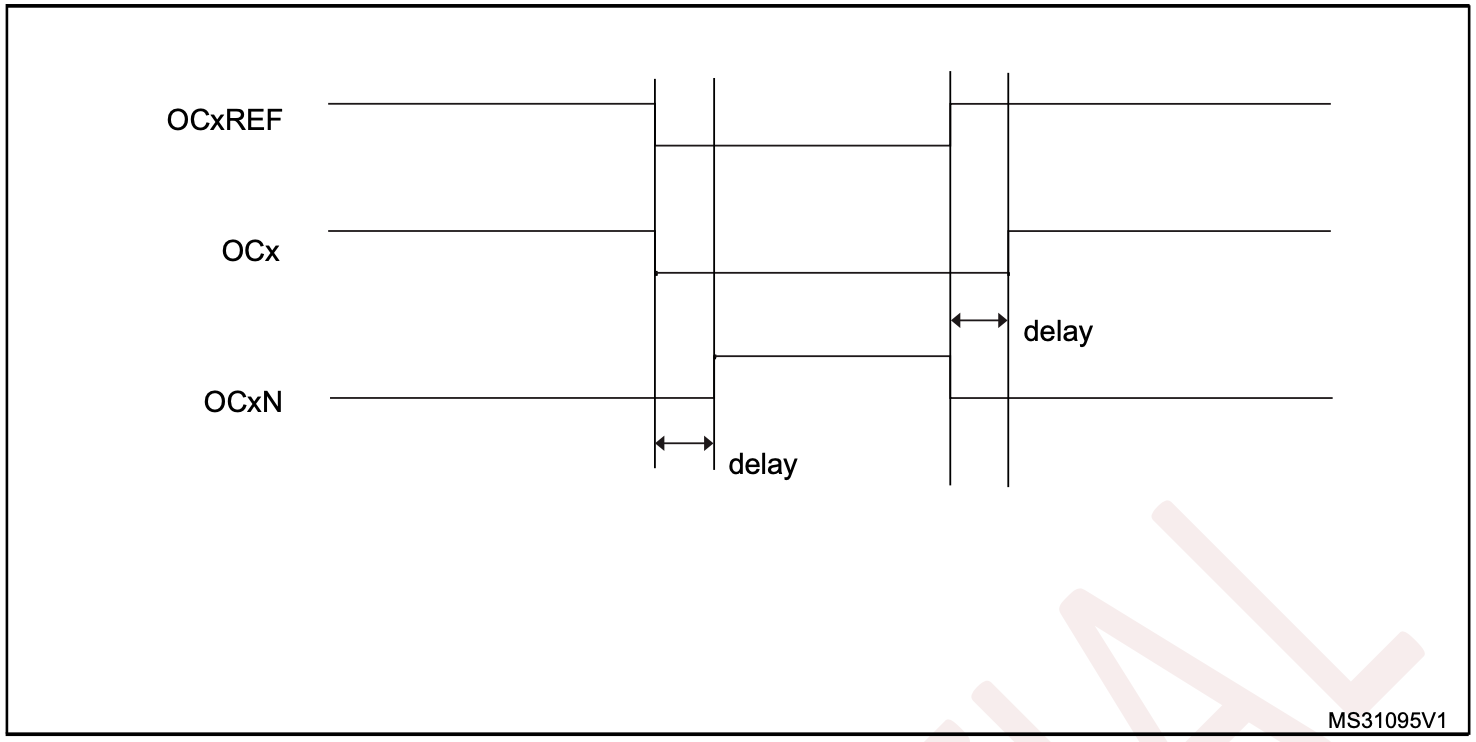

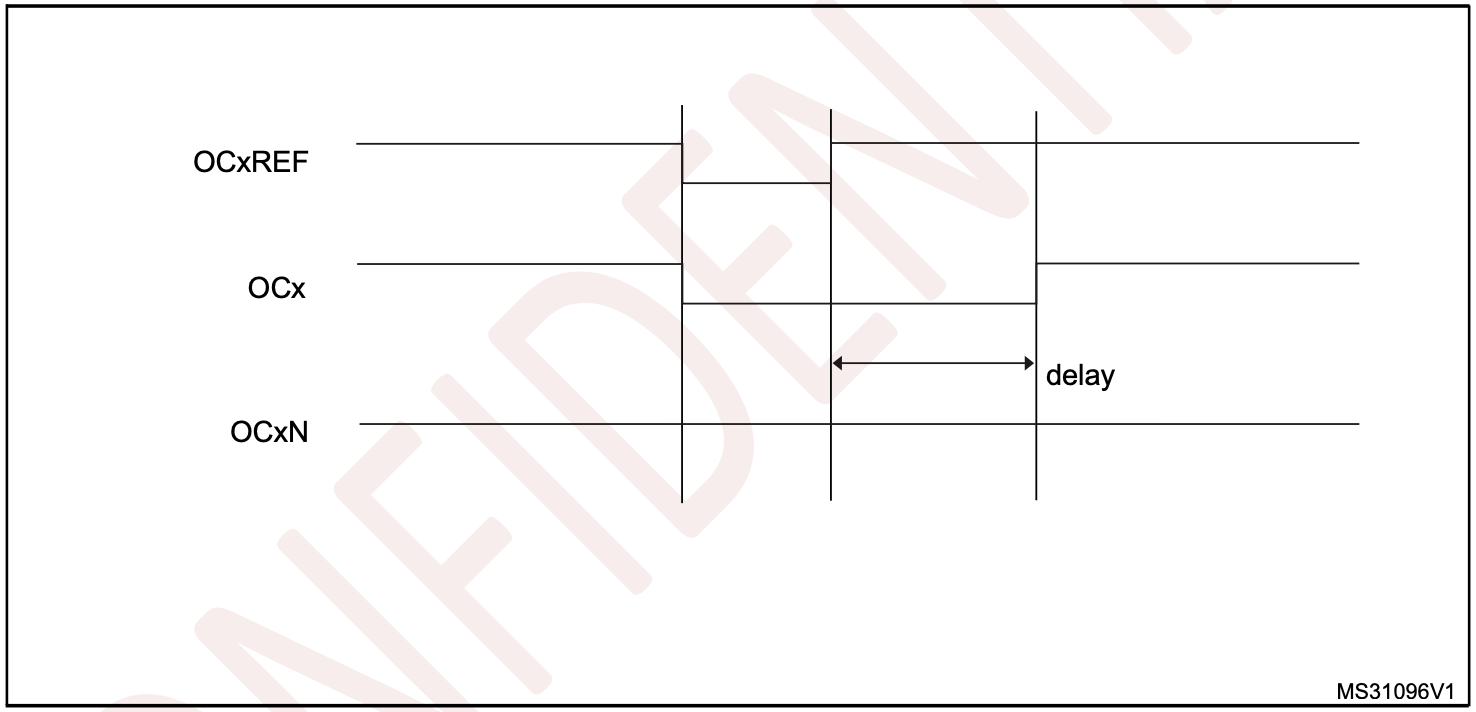

8.3.11 互补输出与死区时间插入¶

高级控制定时器可以输出两个互补信号,并管理输出的关闭和开启时刻。这个时间通常被称为死区时间,需要根据连接到输出的设备及其特性(例如电平转换器的固有延迟、功率开关的延迟等)进行调整。

用户可以独立选择每个输出的极性(主输出 OCx 或互补输出 OCxN)。这是通过在 CCER 寄存器中写入 CCxP 和 CCxNP 位来实现的。

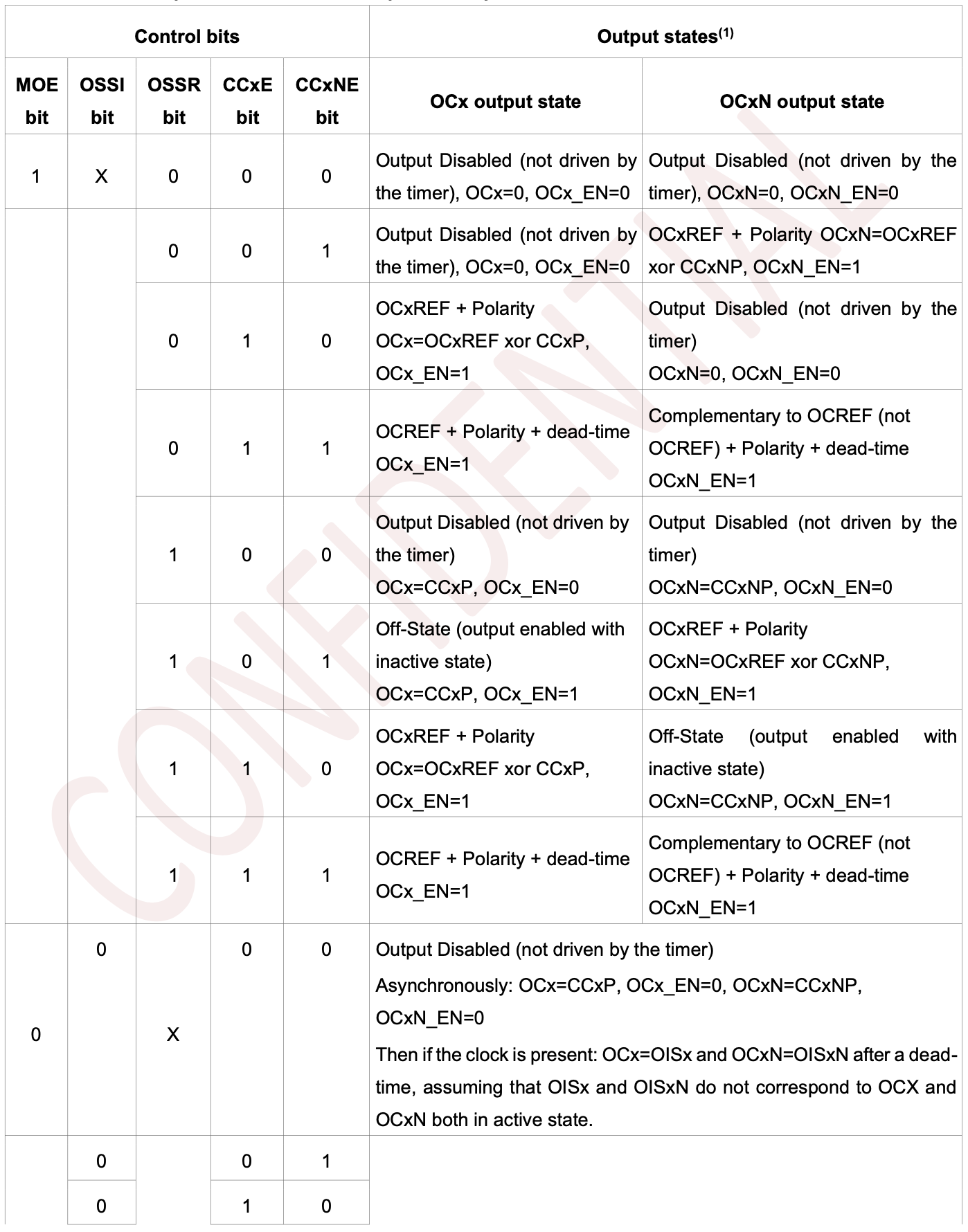

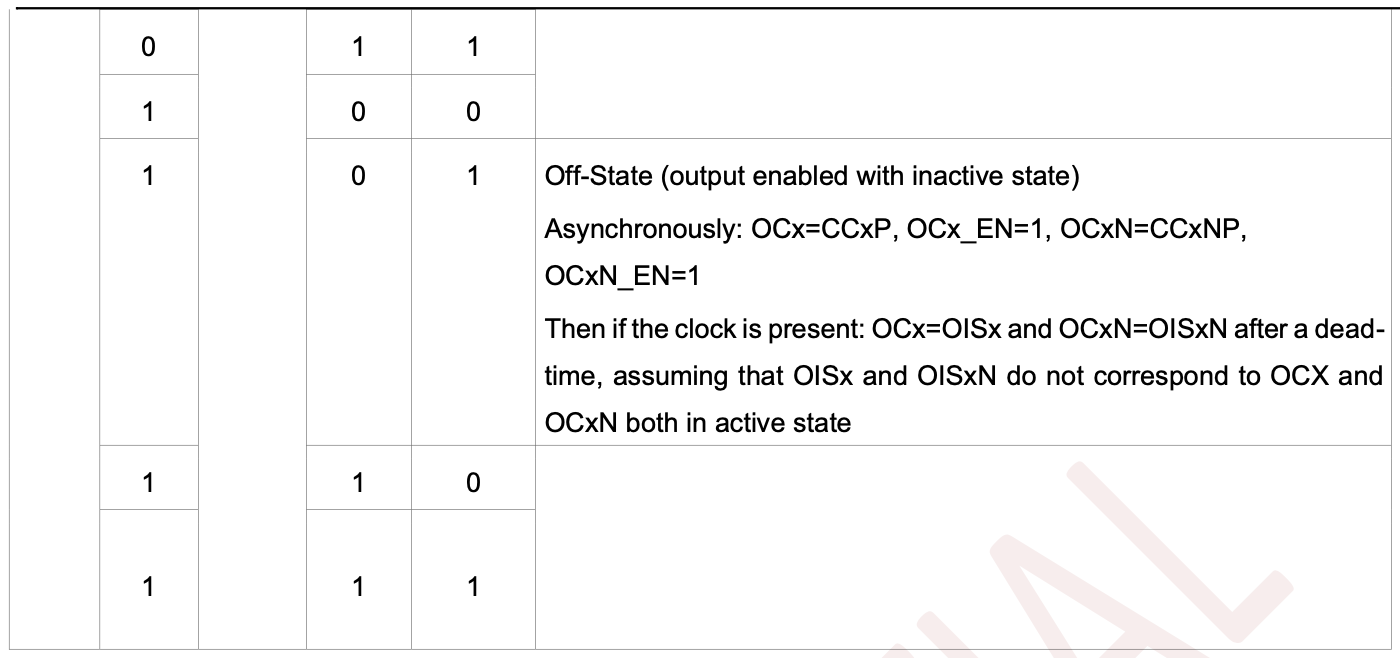

互补信号 OCx 和 OCxN 通过多个控制位的组合激活:CCER 寄存器中的 CCxE 和 CCxNE 位,以及 BDTR 和 CR2 寄存器中的 MOE、OISx、OISxN、OSSI 和 OSSR 位。特别是,当切换到空闲状态时(MOE 下降至 0),死区时间会被激活。

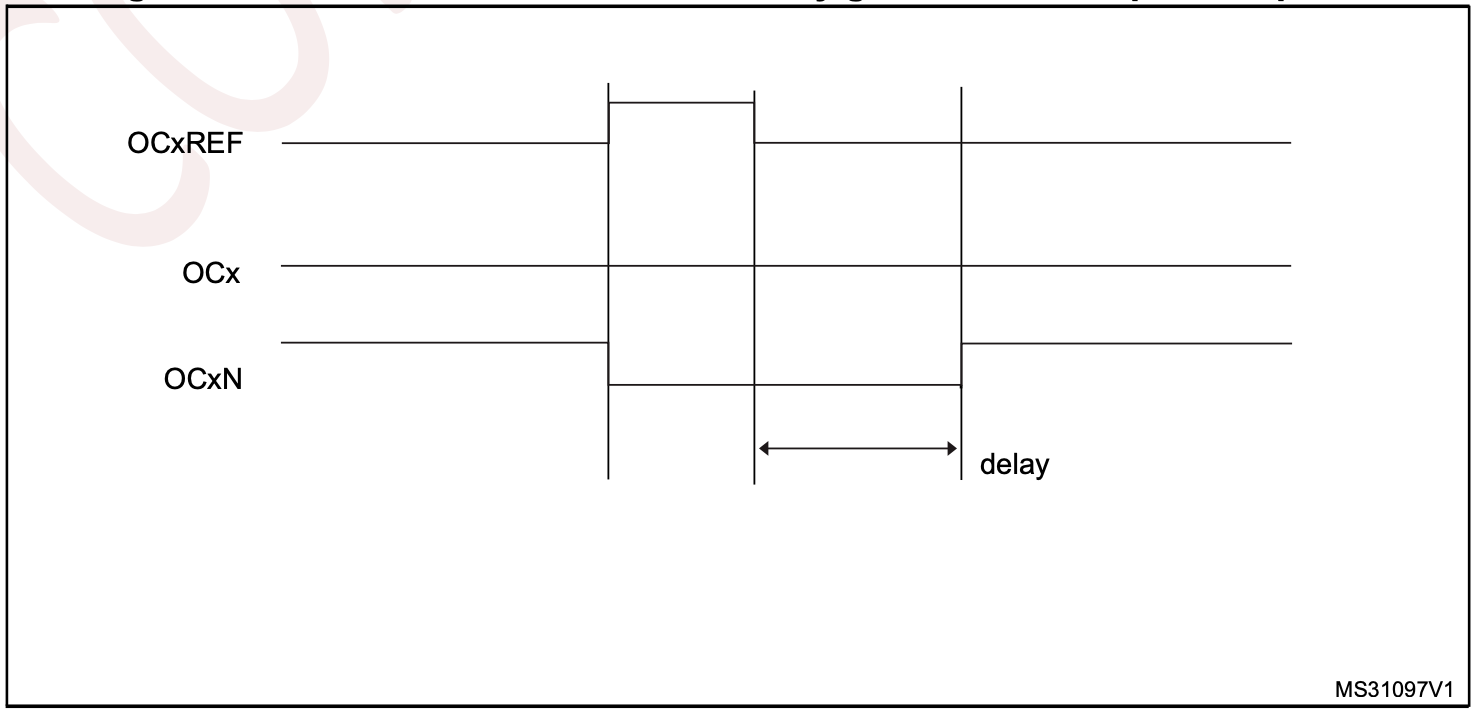

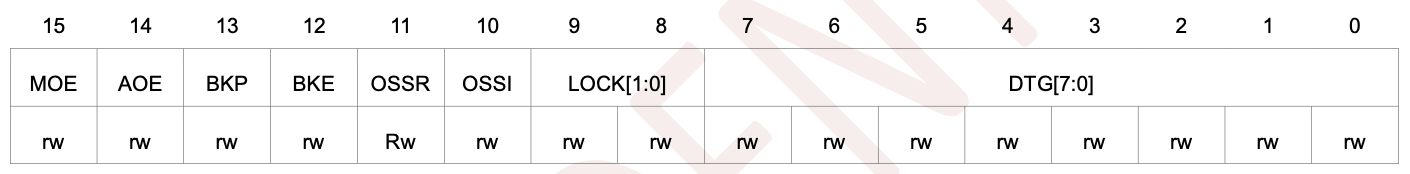

通过设置 CCxE 和 CCxNE 位,并在断开电路存在时设置 MOE 位来启用死区时间插入。BDTR 寄存器中的 DTG[7:0] 位用于控制所有通道的死区时间生成。从参考波形 OCxREF,它生成 2 个输出 OCx 和 OCxN。如果 OCx 和 OCxN 是有效高:

- OCx 输出信号与参考信号相同,但上升沿相对于参考上升沿有所延迟。

- OCxN 输出信号与参考信号相反,但上升沿相对于参考下降沿有所延迟。

如果延迟大于活动输出(OCx 或 OCxN)的宽度,则不会生成相应的脉冲。

以下图示展示了死区时间生成器输出信号与参考信号 OCxREF 之间的关系(我们假设在这些示例中 CCxP=0,CCxNP=0,MOE=1,CCxE=1 和 CCxNE=1)。

图 35. 带死区时间插入的互补输出。

图 36. 死区时间波形(延迟大于负脉冲)。

图 37. 死区时间波形(延迟大于正脉冲)。

死区时间延迟对每个通道都是相同的,并且可以通过 BDTR 寄存器中的 DTG 位进行编程。有关延迟计算的详细信息,请参考断开和死区时间寄存器(BDTR)。

将 OCxREF 重定向到 OCx 或 OCxN¶

在输出模式下(强制、输出比较或 PWM),通过配置 CCER 寄存器中的 CCxE 和 CCxNE 位,OCxREF 可以重定向到 OCx 输出或 OCxN 输出。这允许用户在一个输出上发送特定的波形(例如 PWM 或静态激活电平),而互补输出保持在非激活电平。其他可能的配置是将两个输出都保持在非激活电平,或者将两个输出都设置为激活并互补,带有死区时间。

注意:当仅启用 OCxN(CCxE=0,CCxNE=1)时,它不会进行互补,当 OCxREF 为高时它就变为激活状态。例如,如果 CCxNP=0,则 OCxN=OCxRef。另一方面,当同时启用 OCx 和 OCxN(CCxE=CCxNE=1)时,OCx 在 OCxREF 为高时激活,而 OCxN 进行互补,在 OCxREF 为低时激活。

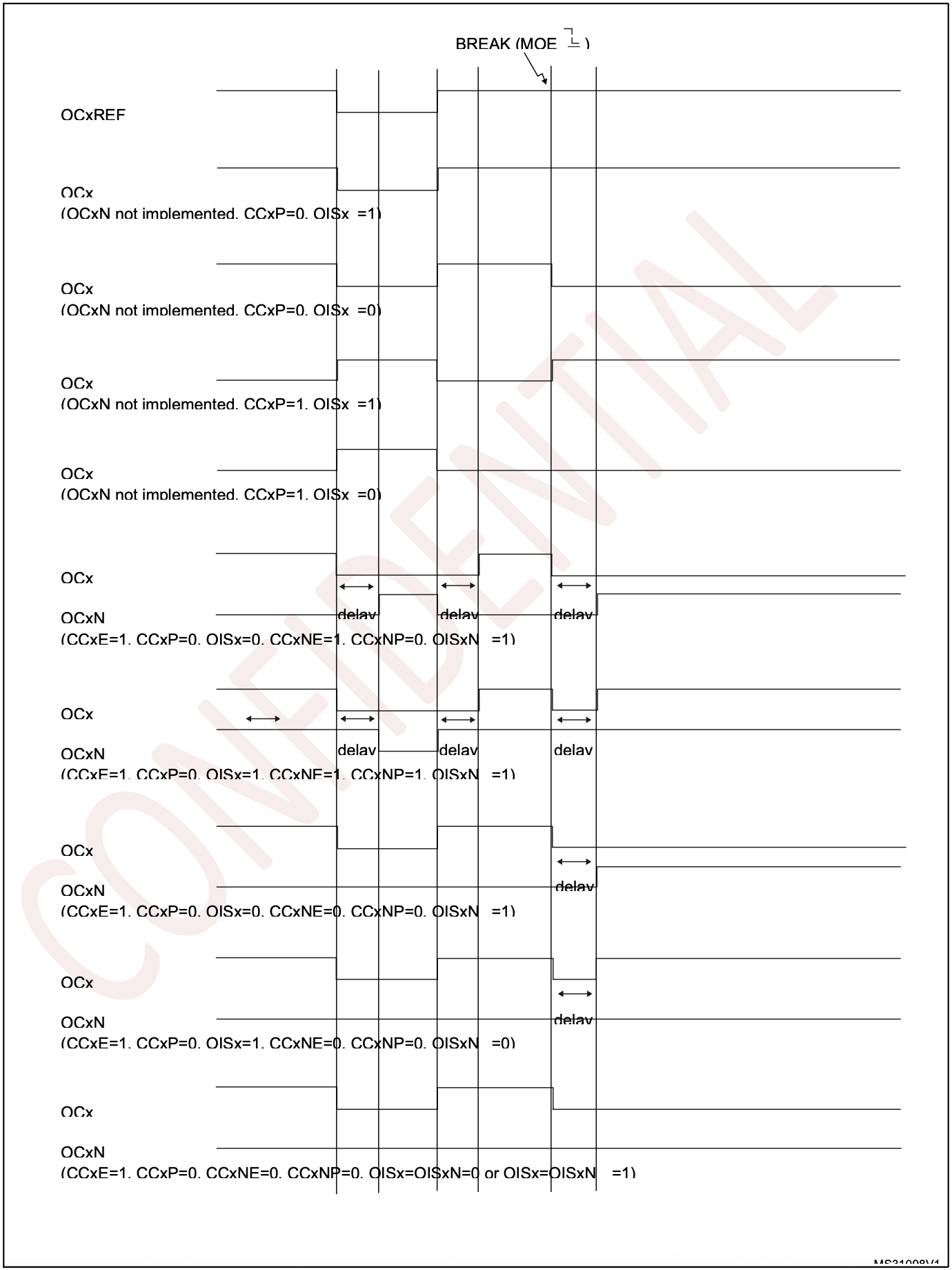

8.3.12 使用断开功能¶

在使用断开功能时,输出使能信号和非激活电平会根据额外的控制位进行修改(BDTR 寄存器中的 MOE、OSSI 和 OSSR 位,CR2 寄存器中的 OISx 和 OISxN 位)。无论如何,OCx 和 OCxN 输出不能在任何给定时刻同时设为激活电平。

断开源可以是断开输入引脚或由时钟安全系统(CSS)生成的时钟故障事件,后者由复位时钟控制器生成。有关时钟安全系统的更多信息,请参阅相关文档。

当从复位退出时,断开电路被禁用,MOE 位为低。用户可以通过在 BDTR 寄存器中设置 BKE 位来启用断开功能。断开输入极性可以通过配置同一寄存器中的 BKP 位来选择。BKE 和 BKP 可以同时修改。当写入 BKE 和 BKP 位时,会应用 1 个 APB 时钟周期的延迟,然后写入生效。因此,在写操作之后,必须等待 1 个 APB 时钟周期才能正确读取该位。

由于 MOE 下降沿可能是异步的,因此在实际信号(作用于输出)和同步控制位(通过 BDTR 寄存器访问)之间插入了重同步电路。这样会导致异步信号与同步信号之间存在一些延迟。特别是,如果 MOE 被写为 1 而之前为低,则在正确读取之前必须插入延迟(虚拟指令)。这是因为用户写入了一个异步信号,但读取的是一个同步信号。

当发生断开事件时(断开输入的选定电平):

- MOE 位被异步清除,将输出设置为非激活状态、空闲状态或复位状态(由 OSSI 位选择)。即使 MCU 振荡器关闭,这个功能也会生效。

- 每个输出通道在 MOE=0 时会根据 CR2 寄存器中的 OISx 位的值进行驱动。如果 OSSI=0,则定时器释放输出使能,否则输出使能保持高电平。

-

当使用互补输出时:

- 输出首先被置于复位状态或非激活状态(取决于极性)。这一步是异步进行的,因此即使定时器没有时钟输入,它也能正常工作。

- 如果定时器时钟仍然存在,则死区时间生成器被重新激活,以在死区时间后使用 OISx 和 OISxN 位编程的电平驱动输出。即便如此,OCx 和 OCxN 不能同时被驱动到激活电平。请注意,由于 MOE 上的重同步,死区时间略长(大约 2 个 ck_tim 时钟周期)。

- 如果 OSSI=0,则定时器释放输出使能,否则一旦 CCxE 或 CCxNE 位为高,输出使能会保持或变为高。

-

断开状态标志(SR 寄存器中的 BIF 位)被置位。如果 DIER 寄存器中的 BIE 位被设置,则可以生成中断。如果 DIER 寄存器中的 BDE 位被设置,则可以发送 DMA 请求。

- 如果 BDTR 寄存器中的 AOE 位被设置,则 MOE 位将在下一个更新事件(UEV)时自动重新设置。这可以用于执行调节。例如,可以用于安全功能,断开输入可以连接到电源驱动器、温度传感器或其他安全组件的警报。

- 否则,MOE 保持低电平,直到再次写入 ‘1’。在这种情况下,它可以用于安全功能,断开输入可以连接到来自电源驱动器、热传感器或任何安全组件的警报。

注意:断开输入作用于电平。因此,当断开输入处于激活状态时,MOE 无法被设置(既不能自动设置,也不能通过软件设置)。与此同时,状态标志 BIF 不能被清除。

断开功能可以通过 BRK 输入生成,BRK 输入具有可编程的极性和 BDTR 寄存器中的启用位 BKE。

生成断开的两种方式:

- 使用具有可编程极性和启用位 BKE 的 BRK 输入,在 BDTR 寄存器中配置。

- 通过软件使用 EGR 寄存器中的 BG 位。

除了断开输入和输出管理外,断开电路内还实现了写保护,以保障应用安全。它允许冻结多个参数的配置(死区时间、OCx/OCxN 极性和禁用时的状态、OCxM 配置、断开使能和极性)。用户可以选择由 BDTR 寄存器中的 LOCK 位选择的三种保护级别。有关详细信息,请参考 "断开和死区时间寄存器(BDTR)"。LOCK 位只能在 MCU 重置后写入一次。

图 38 显示了断开响应时输出行为的示例。

图 38. 断开响应时的输出行为。

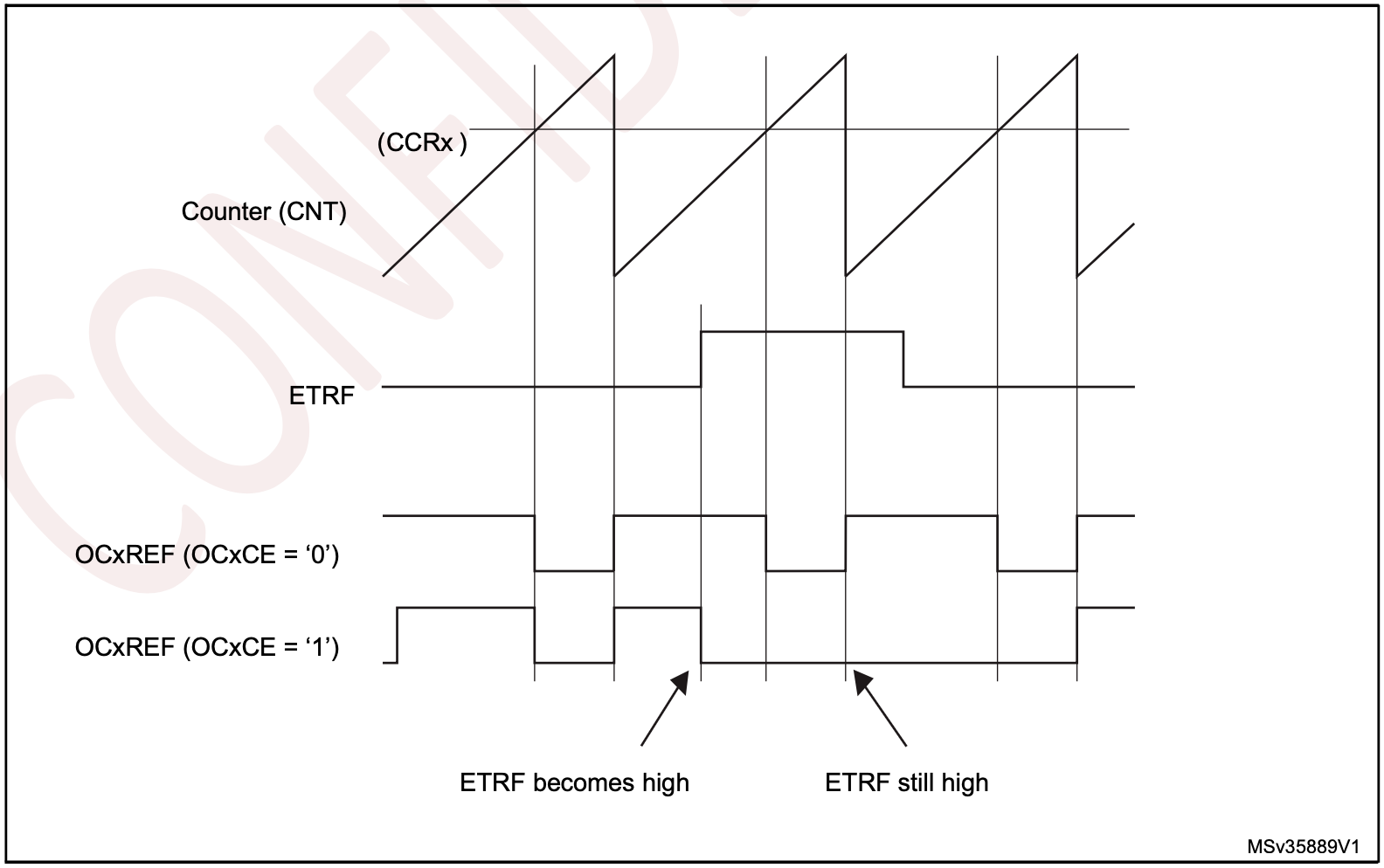

8.3.13 外部事件清除 OCxREF 信号¶

通过对 ETRF 输入施加高电平(将相应 CCMRx 寄存器的 OCxCE 启用位设置为 ‘1’),可以将给定通道的 OCxREF 信号驱动为低电平。OCxREF 信号将保持为低电平,直到下一个更新事件(UEV)发生。

此功能仅可在输出比较和 PWM 模式中使用,在强制模式下不可用。

例如,ETR 信号可以连接到比较器的输出,用于电流处理。在这种情况下,ETR 必须按以下方式配置:

- 外部触发预分频器应保持关闭:将 SMCR 寄存器的 ETPS[1:0] 位设置为 ‘00’。

- 必须禁用外部时钟模式 2:将 SMCR 寄存器的 ECE 位设置为 ‘0’。

- 外部触发极性(ETP)和外部触发滤波器(ETF)可以根据用户需要进行配置。

图 39 显示了当 ETRF 输入变为高电平时,OCxREF 信号的行为,适用于 OCxCE 启用位的两种值。在此示例中,定时器已配置为 PWM 模式。

图 39. 清除 OCxREF

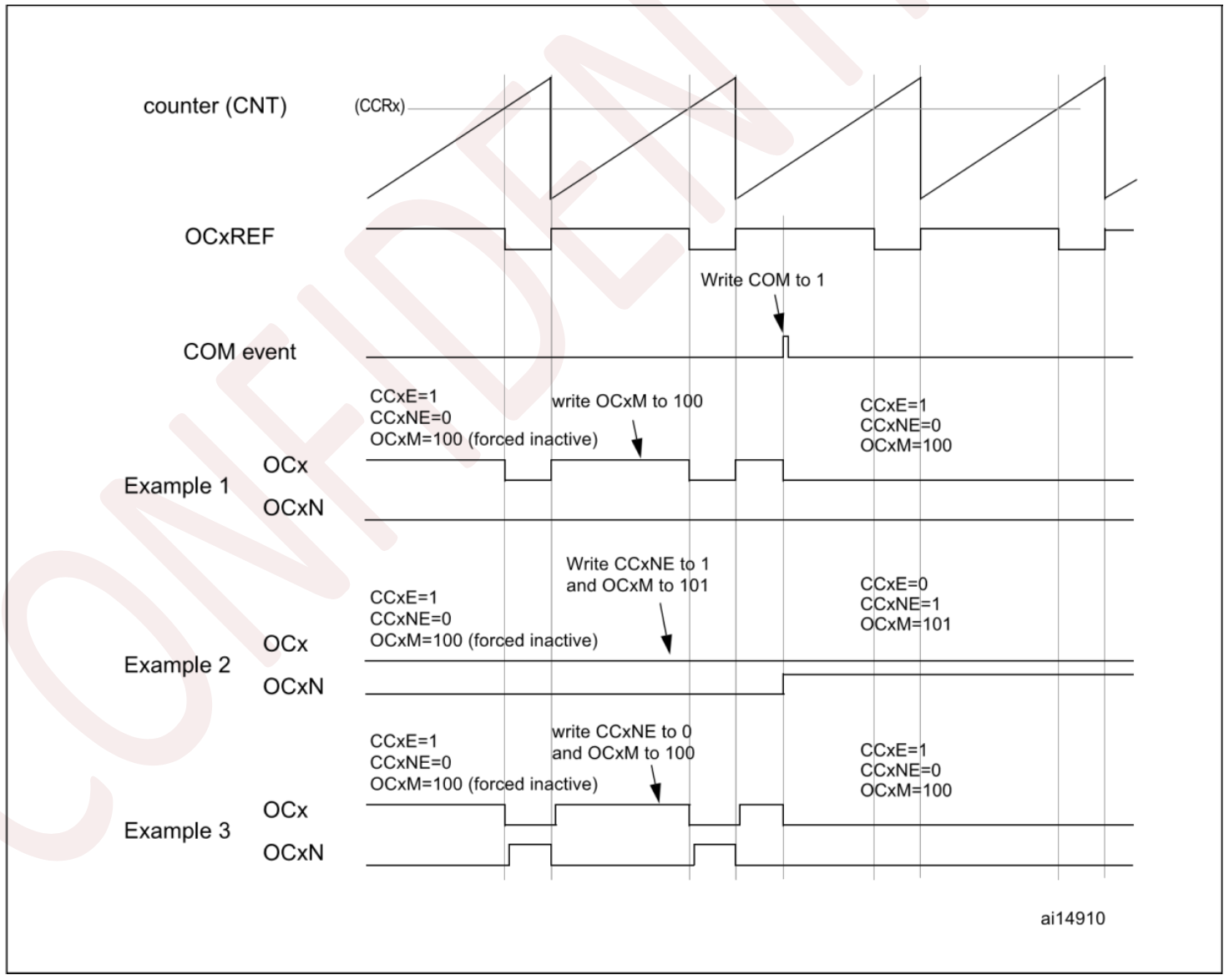

8.3.14 6 步 PWM 生成¶

当通道上使用互补输出时,OCxM、CCxE 和 CCxNE 位上会有预装载位。预装载位会在 COM 换向事件发生时被传输到影像位。用户可以提前编程配置,以便为下一个步骤进行配置,并且可以同时更改所有通道的配置。COM 事件可以通过软件设置 COM 位在 EGR 寄存器中触发,或者通过硬件触发(在 TRGI 上升沿时触发)。

当 COM 事件发生时,会设置一个标志(SR 寄存器中的 COMIF 位),这可以生成中断(如果 DIER 寄存器中的 COMIE 位被设置)或 DMA 请求(如果 DIER 寄存器中的 COMDE 位被设置)。

图 40 描述了当 COM 事件发生时,OCx 和 OCxN 输出的行为,在三种不同的已编程配置示例中。

图 40. 6 步生成,COM 示例(OSSR=1)

8.3.15 单脉冲模式¶

单脉冲模式(OPM)是前述模式的一个特例。它允许计数器在响应一个刺激后启动,并在可编程的延迟后生成一个具有可编程长度的脉冲。

计数器的启动可以通过从模式控制器进行控制。生成波形可以在输出比较模式或 PWM 模式中完成。通过在 CR1 寄存器中设置 OPM 位来选择单脉冲模式。这使得计数器在下一个更新事件(UEV)时自动停止。

只有当比较值与计数器初始值不同的时候,才能正确生成脉冲。在启动之前(当定时器等待触发时),配置必须为:

- 在向上计数时:CNT < CCRx

- 在向下计数时:CNT > CCRx

- ARR(特别是,0 < CCRx)

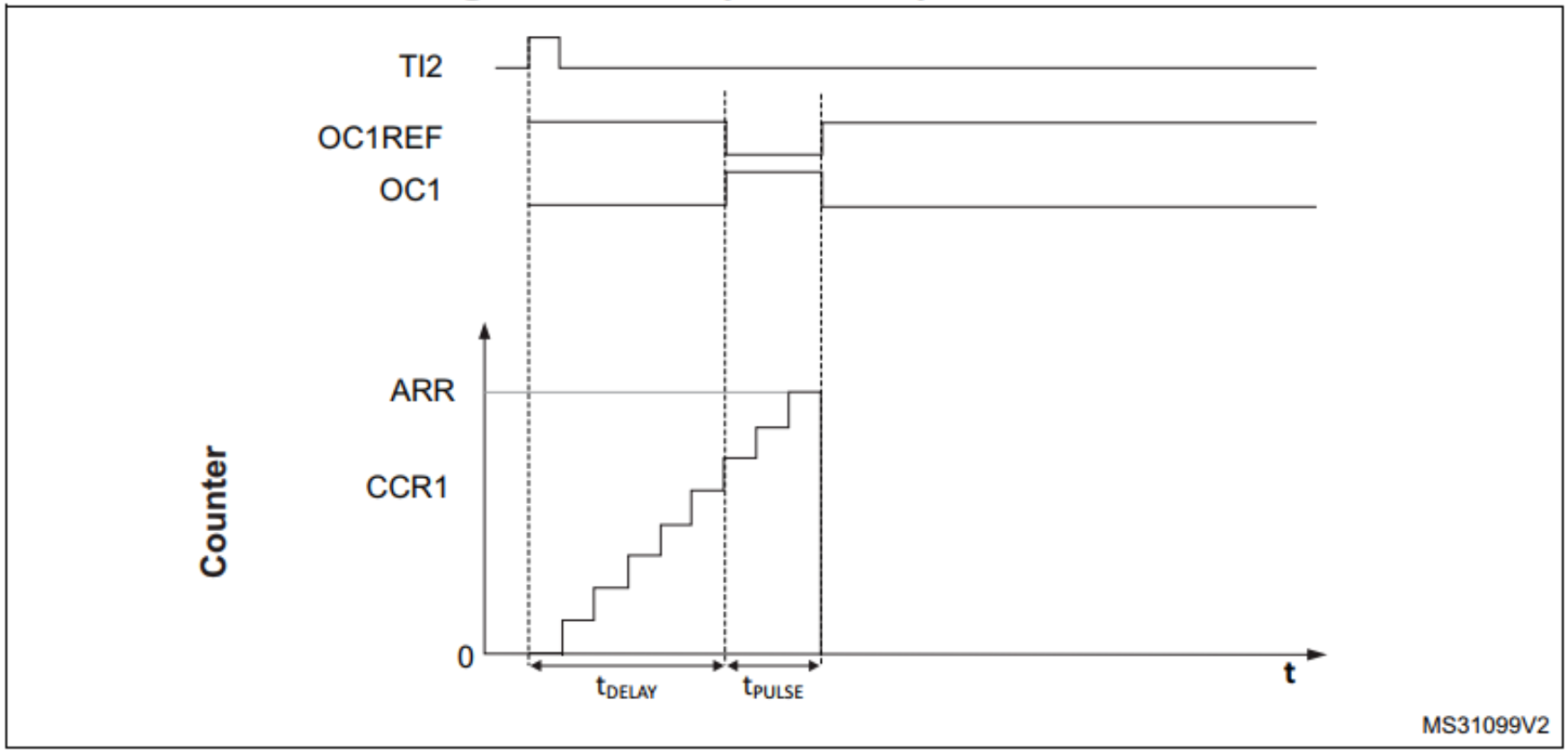

图 41. 单脉冲模式示例。

例如,用户可能希望在 TI2 输入引脚上检测到一个上升沿后,在 OC1 上生成一个时长为 tPULSE 的正脉冲,并延迟 tDELAY。我们使用 TI2FP2 作为触发信号:

- 将 TI2FP2 映射到 TI2,通过在 CCMR1 寄存器中写入 CC2S=’01’。

- TI2FP2 必须检测上升沿,通过在 CCER 寄存器中写入 CC2P=’0’。

- 通过在 SMCR 寄存器中写入 TS=’110’ 将 TI2FP2 配置为从模式控制器(TRGI)的触发源。

- 通过在 SMCR 寄存器中将 SMS 写为 ‘110’ 使用 TI2FP2 启动计数器(触发模式)。

OPM 波形由比较寄存器定义(考虑时钟频率和计数器预分频器)。

- tDELAY 由写入 CCR1 寄存器的值定义。

- tPULSE 由自动重装载值和比较值之间的差值(ARR - CCR1)定义。

- 假设用户希望构建一个波形,在比较匹配时从 ‘0’ 变为 ‘1’,并在计数器达到自动重装载值时从 ‘1’ 变为 ‘0’。为此,通过在 CCMR1 寄存器中写入 OC1M=111 启用 PWM 模式 2。用户还可以通过在 CCMR1 寄存器中写入 OC1PE=’1’ 和在 CR1 寄存器中设置 ARPE 来启用预装载寄存器。在这种情况下,比较值必须写入 CCR1 寄存器,自动重装载值写入 ARR 寄存器,生成一个更新事件通过设置 UG 位,并等待 TI2 上的外部触发事件。在此示例中,CC1P 被写为 ‘0’。

在我们的示例中,CR1 寄存器中的 DIR 和 CMS 位应该为低。

用户只需要一个脉冲(单次模式),因此必须在 CR1 寄存器中将 OPM 位写为 '1',以便在下一个更新事件时停止计数器(当计数器从自动重装载值回滚到 0 时)。当 CR1 寄存器中的 OPM 位设置为 '0' 时,将选择重复模式。

特殊情况:OCx 快速使能:

在单脉冲模式中,TIx 输入上的边缘检测设置 CEN 位,从而启用计数器。然后,计数器与比较值之间的比较使得输出发生切换。但这些操作需要几个时钟周期,这限制了我们能得到的最小延迟 tDELAY min。

如果用户希望输出具有最小延迟的波形,则必须在 CCMRx 寄存器中设置 OCxFE 位。然后,OCxRef(和 OCx)会响应刺激而被强制输出,而不考虑比较操作。它的新电平与发生比较匹配时的电平相同。OCxFE 仅在通道配置为 PWM1 或 PWM2 模式时生效。

8.3.16 编码器接口模式(Encoder Interface Mode)¶

要选择编码器接口模式(Encoder Interface mode),应在 SMCR 寄存器中设置 SMS 位为:

001:仅在 TI2 边沿触发计数;010:仅在 TI1 边沿触发计数;011:在 TI1 和 TI2 的边沿触发计数。

使用 CCER 寄存器中的 CC1P 和 CC2P 位配置 TI1 和 TI2 的极性。如有需要,用户还可以配置输入滤波器(Input Filter)。

TI1 和 TI2 输入用于连接增量式编码器(incremental encoder)。当计数器已启用(即 CR1 寄存器中的 CEN=1),则在 TI1FP1 或 TI2FP2 的每一个有效跳变上计数。

注:TI1FP1 和 TI2FP2 是 TI1 和 TI2 经过输入滤波器与极性控制后的信号。若未启用滤波和极性翻转,则 TI1FP1=TI1,TI2FP2=TI2。

两路输入的跳变顺序会被识别,用于生成计数脉冲及方向信号。根据跳变的顺序,计数器会递增或递减。此时 CR1 寄存器中的 DIR 位会被硬件自动更新。

无论是在 TI1、TI2 或同时在 TI1 和 TI2 上进行计数,每当任一输入发生跳变时,都会重新计算 DIR 位。

编码器接口模式本质上是一个带方向检测的外部时钟输入模式,意味着计数器将在 0 和自动重载寄存器 ARR 中的值之间循环计数。因此,用户在启动前必须正确配置 ARR。

此外,捕获、比较、预分频器、重复计数器和触发输出功能依旧正常工作。编码器模式与外部时钟模式 2(External clock mode 2)不兼容,不能同时启用。

在该模式下,计数器会自动跟随增量式编码器的速度和方向更新,其内容始终代表编码器的位置。计数方向与所连接传感器的旋转方向一致。

表 1:编码器信号与计数方向关系

| 活跃边沿 | 对端信号电平 | TI1FP1 信号 | TI2FP2 信号 | 计数模式 | 方向 |

|---|---|---|---|---|---|

| 上升沿 | 高 | TI1 计数 | 向下 | ||

| 上升沿 | 低 | TI1 计数 | 向上 | ||

| 下降沿 | 高 | TI1 计数 | 向上 | ||

| 下降沿 | 低 | TI1 计数 | 向下 | ||

| 上升沿 | 高 | TI2 计数 | 向上 | ||

| 上升沿 | 低 | TI2 计数 | 向下 | ||

| 下降沿 | 高 | TI2 计数 | 向下 | ||

| 下降沿 | 低 | TI2 计数 | 向上 | ||

| 上升沿 | 高 | TI1+TI2 计数 | 向下 | ||

| 上升沿 | 低 | TI1+TI2 计数 | 向上 | ||

| 下降沿 | 高 | TI1+TI2 计数 | 向上 | ||

| 下降沿 | 低 | TI1+TI2 计数 | 向下 |

注:此表假设 TI1 和 TI2 不会在同一时刻同时变化。

一个外部增量编码器可以直接连接至 MCU,不需要额外的接口逻辑。但通常建议使用比较器将编码器的差分信号转换为数字信号,以显著提高抗干扰能力。

编码器的第三个输出(表示机械零位)可以连接至 MCU 的外部中断引脚,用于触发计数器复位。

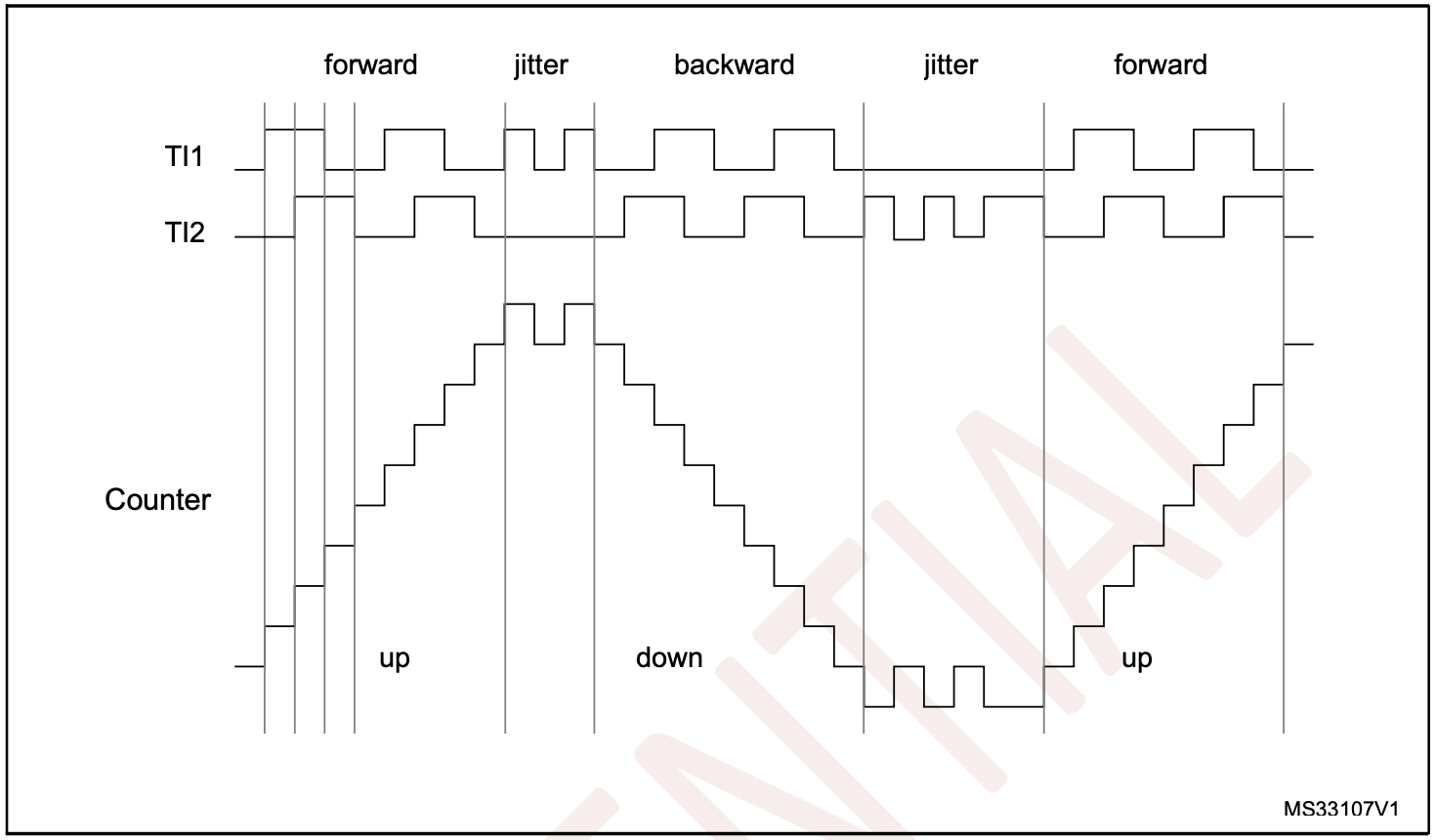

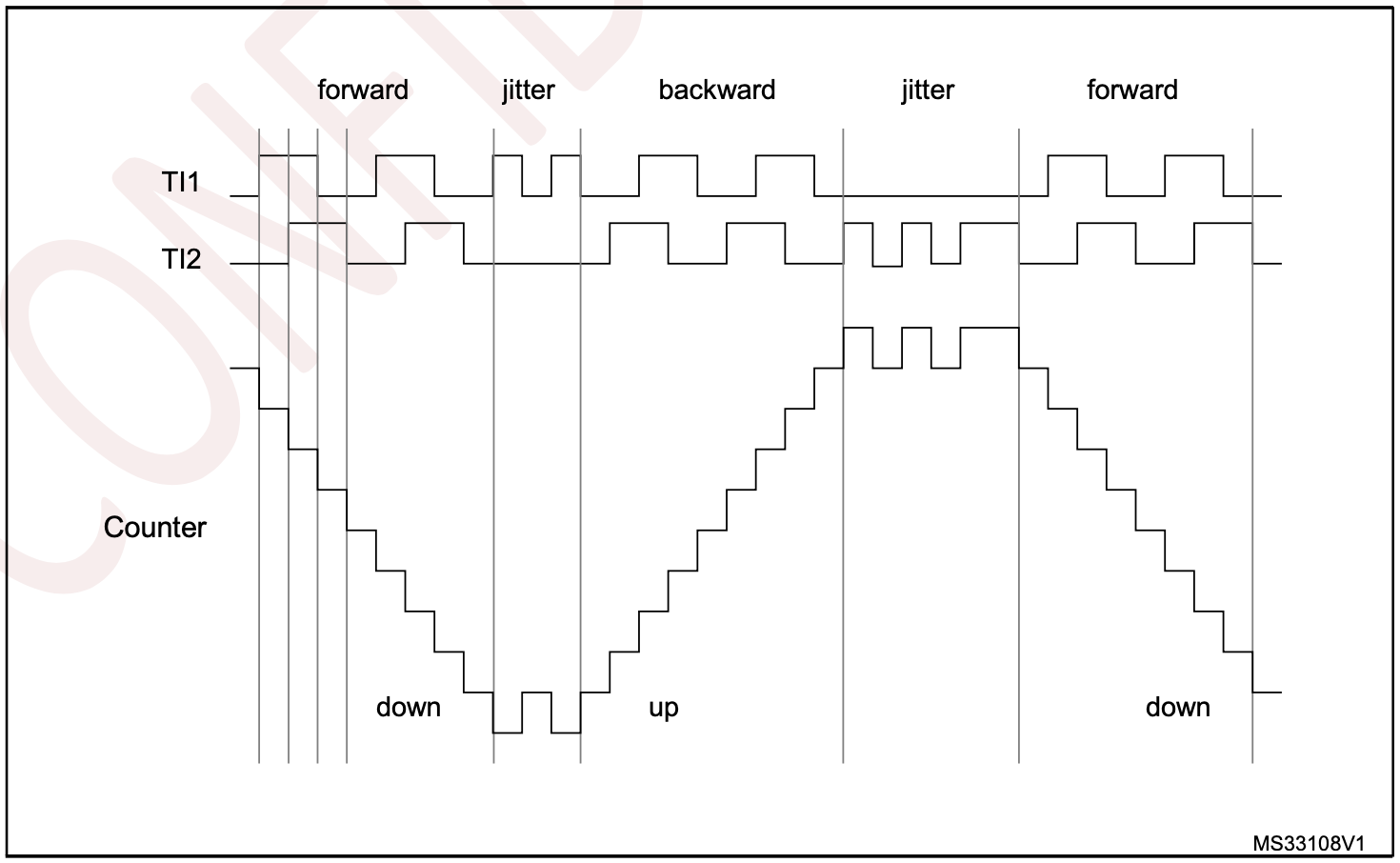

图 42:展示了计数器在编码器接口模式下的工作原理,包括计数信号的生成和方向控制;同时演示了如何在选择双边沿时进行输入抖动的补偿(当传感器接近切换点时可能出现该现象)。

示例配置如下:

CC1S = 01(CCMR1 寄存器中,TI1FP1 映射为 TI1)CC2S = 01(CCMR2 寄存器中,TI2FP2 映射为 TI2)CC1P = 0且IC1F = 0000(TI1 未翻转,无滤波)CC2P = 0且IC2F = 0000(TI2 未翻转,无滤波)SMS = 011(SMCR 寄存器中,TI1 与 TI2 均在上升沿和下降沿激活)CEN = 1(CR1 寄存器中,计数器启用)

图 43:展示了在与上述相同配置下,仅将

CC1P设置为1(TI1 极性翻转)的情况下,编码器接口模式的行为变化。

当定时器配置为编码器接口模式后,可通过以下方式获取动态信息(如速度、加速度、减速度):

- 使用第二个定时器配置为捕获模式(Input Capture)以测量两个编码器事件之间的周期;

- 利用编码器输出的“机械零位”信号作为触发捕获;

- 也可以定期读取计数器值,如使用第三个输入捕获寄存器锁存(如可用);

- 还可以通过DMA 请求读取该值,该请求可由实时时钟(RTC)生成。

8.3.17 定时器输入 XOR 功能¶

CR2 寄存器中的 TI1S 位允许通道 0 的输入滤波器连接到一个 XOR 门的输出,该 XOR 门将三个输入引脚 CH1、CH2 和 CH3 进行组合。

XOR 输出可用于所有定时器输入功能,例如触发或输入捕获。

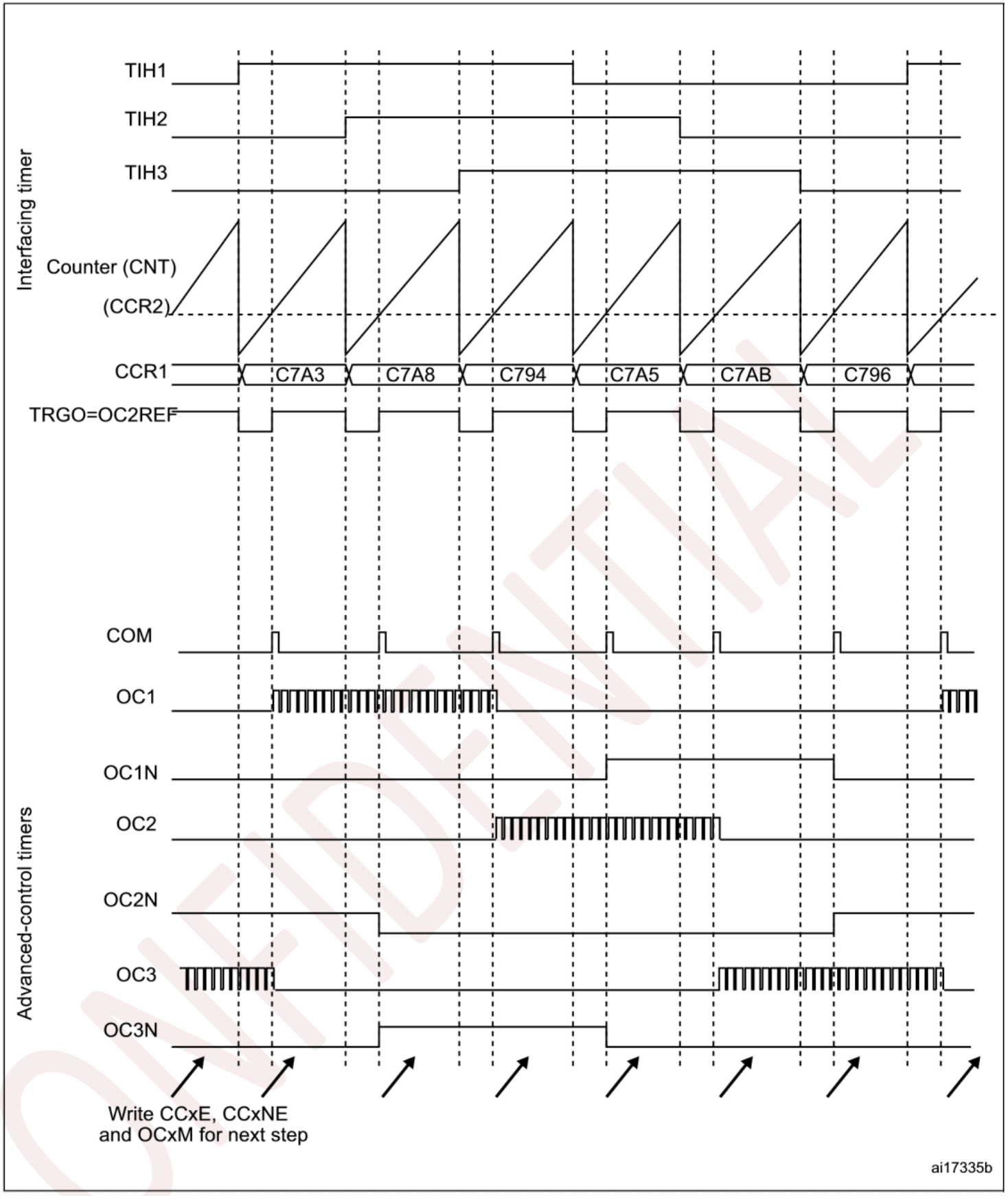

8.3.18 与霍尔传感器接口¶

这通过使用高级控制定时器生成用于驱动电机的 PWM 信号,以及另一个定时器(在图 44 中称为“接口定时器”)来实现。“接口定时器”通过 XOR 门连接 3 个定时器输入引脚(CH1、CH2 和 CH3)到 TI1 输入通道(通过在 CR2 寄存器中设置 TI1S 位来选择)。

从属模式控制器配置为复位模式;从属输入为 TI1F_ED。因此,每当 3 个输入中的任意一个发生翻转时,计数器从 0 开始重新计数。这创建了一个由霍尔输入上的任何变化触发的时间基准。

在“接口定时器”中,捕获/比较通道 0 被配置为捕获模式,捕获信号为 TRC(见图 27)。捕获的值表示输入发生两次变化之间的时间,反映电机的转速信息。

“接口定时器”还可以在输出模式下使用,以生成一个脉冲,该脉冲用于更改高级控制定时器通道的配置(通过触发 COM 事件)。定时器用于生成用于驱动电机的 PWM 信号。为此,接口定时器通道必须被编程为在一个预定延迟后生成一个正脉冲(以输出比较或 PWM 模式)。该脉冲通过 TRGO 输出发送到高级控制定时器。

示例:用户希望在霍尔输入连接的某个定时器上发生变化时,在一个预定延迟后更改高级控制定时器的 PWM 配置。

- 通过将 CR2 寄存器中的 TI1S 位设置为 ‘1’,配置 3 个定时器输入经 OR 连接至 TI1 输入通道;

- 编程时间基准:将 ARR 写为最大值(计数器必须由 TI1 的变化清零),设置预分频器,使最大计数周期长于两个传感器变化之间的时间;

- 将通道 0 配置为捕获模式(选择 TRC):将 CCMR1 寄存器中的 CC1S 位写为 ‘11’。用户还可以在需要时配置数字滤波器;

- 将通道 1 配置为带所需延迟的 PWM 模式 2:将 CCMR1 寄存器中的 OC2M 位写为 ‘111’,将 CC2S 位写为 ‘00’;

- 在 TRGO 上选择 OC2REF 作为触发输出:将 CR2 寄存器中的 MMS 位写为 ‘101’;

在高级控制定时器中,必须选择正确的 ITR 输入作为触发输入,定时器配置为生成 PWM 信号,捕获/比较控制信号被预加载(CR2 寄存器中的 CCPC=1),COM 事件由触发输入控制(CR2 寄存器中的 CCUS=1)。PWM 控制位(CCxE、OCxM)在下一步的 COM 事件后被写入(这可以在由 OC2REF 上升沿产生的中断子程序中完成)。

图 44 描述了该示例。

图 44. 霍尔传感器接口示例

8.3.19 外部触发同步¶

定时器可以通过多种模式与外部触发信号进行同步:复位模式、门控模式和触发模式。

从模式:复位模式

计数器及其预分频器可以在触发输入上发生事件时被重新初始化。此外,如果 CR1 寄存器中的 URS 位为低电平,则会生成一个更新事件 UEV。随后所有预加载的寄存器(ARR,CCRx)都会被更新。

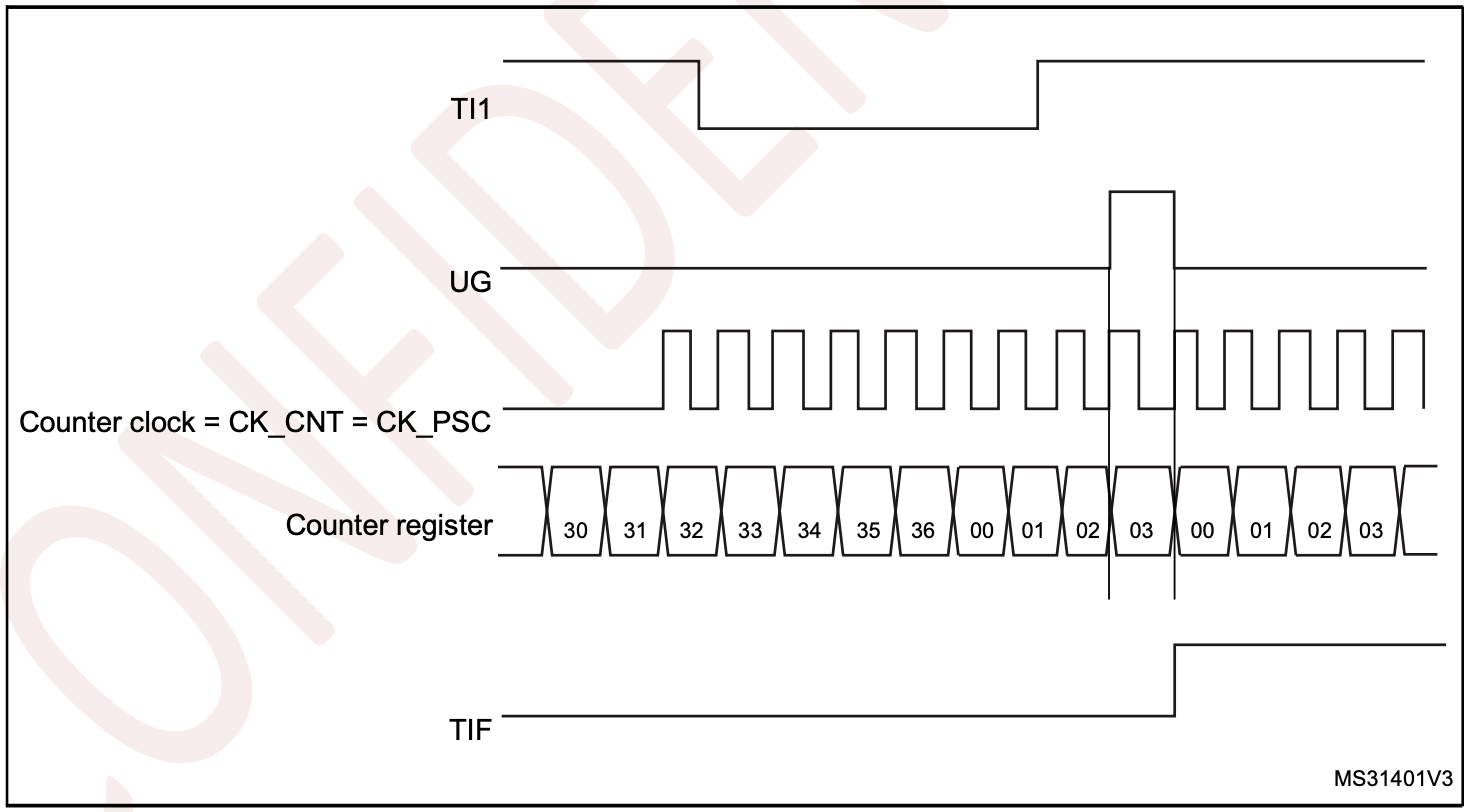

在以下示例中,向上计数器在 TI1 输入的上升沿被清零:

- 配置通道 0 以检测 TI1 上的上升沿。配置输入滤波器的持续时间(在本例中不需要滤波器,因此保持 IC1F=0000)。捕获预分频器在触发中不起作用,因此无需配置它。CC1S 位仅选择输入捕获源,在 CCMR1 寄存器中写入 CC1S=01。为了使能极性(仅检测上升沿),在 CCER 寄存器中写入 CC1P=0。

- 通过在 SMCR 寄存器中写入 SMS=100,将定时器配置为复位模式。通过在 SMCR 寄存器中写入 TS=101,选择 TI1 作为输入源。

- 通过在 CR1 寄存器中写入 CEN=1,启动计数器。

计数器在内部时钟上开始计数,然后正常运行直到 TI1 出现上升沿。当 TI1 上升沿发生时,计数器被清零并从 0 重新开始计数。与此同时,触发标志被置位(SR 寄存器中的 TIF 位),如果启用了中断或 DMA(由 DIER 寄存器中的 TIE 和 TDE 位决定),则可发出中断请求或 DMA 请求。

下图展示了当自动重载寄存器 ARR=0x36 时的该行为。TI1 输入上升沿与计数器实际复位之间的延迟是由 TI1 输入的重同步电路引起的。

图 45. 复位模式下的控制电路

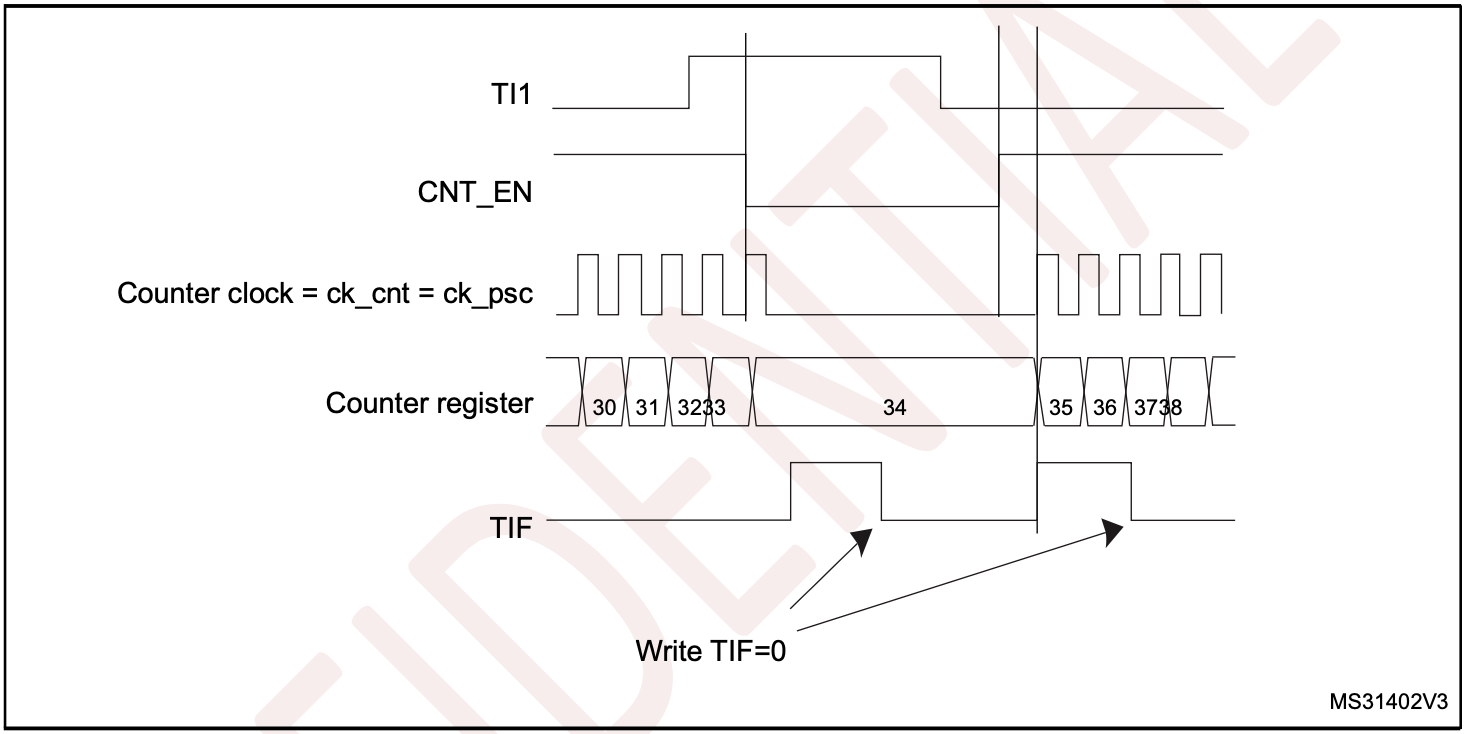

从模式:门控模式

计数器可以根据所选输入的电平来启用。

在以下示例中,向上计数器仅在 TI1 输入为低电平时进行计数:

- 配置通道 0 以检测 TI1 上的低电平。配置输入滤波器的持续时间(在本例中不需要滤波器,因此保持 IC1F=0000)。捕获预分频器在触发中不起作用,因此用户无需配置它。CC1S 位仅用于选择输入捕获源,在 CCMR1 寄存器中写入 CC1S=01。在 CCER 寄存器中写入 CC1P=1,以确认极性(并仅检测低电平)。

- 通过在 SMCR 寄存器中写入 SMS=101,将定时器配置为门控模式。通过在 SMCR 寄存器中写入 TS=101,选择 TI1 作为输入源。

- 通过在 CR1 寄存器中写入 CEN=1 来使能计数器(在门控模式中,如果 CEN=0,则无论触发输入电平如何,计数器都不会启动)。

计数器在内部时钟上开始计数,只要 TI1 为低电平就持续计数,一旦 TI1 变为高电平便停止计数。SR 寄存器中的 TIF 标志在计数器启动或停止时都会被置位。

TI1 上升沿与计数器实际停止之间的延迟是由于 TI1 输入的重同步电路引起的。

图 46. 门控模式下的控制电路

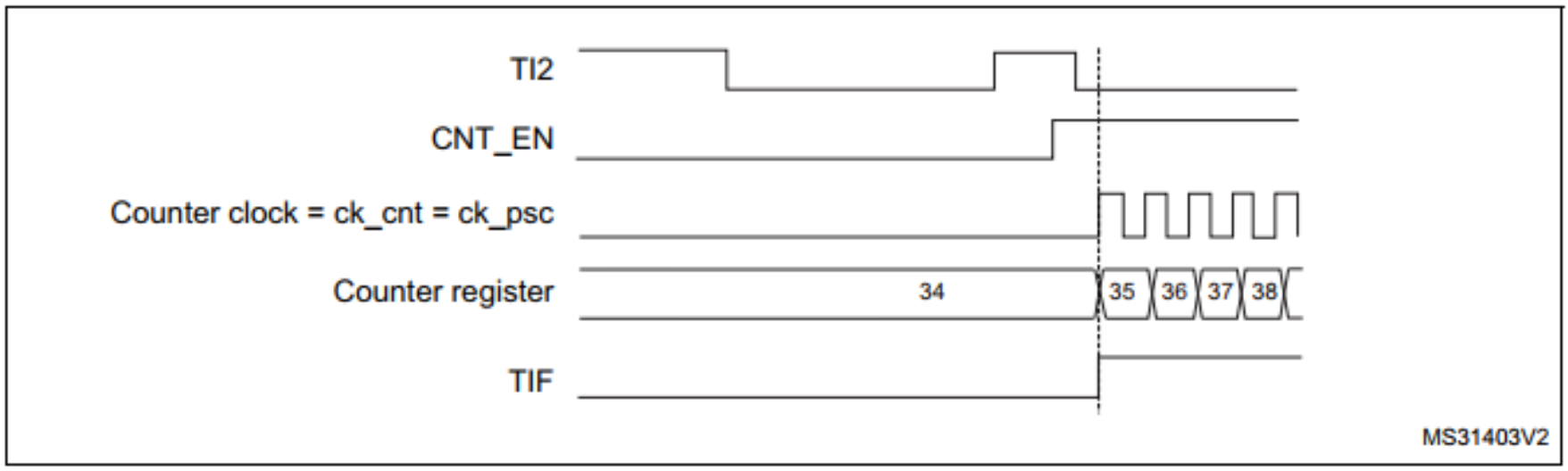

从模式:触发模式

计数器可以响应所选输入上的事件而启动。

在以下示例中,向上计数器响应 TI2 输入上的上升沿而启动:

- 配置通道 1 以检测 TI2 上的上升沿。配置输入滤波器持续时间(在本例中不需要滤波器,因此保持 IC2F=0000)。捕获预分频器在触发中不起作用,因此无需配置。CC2S 位用于选择输入捕获源,仅需配置 CC2S=01(在 CCMR1 寄存器中)。在 CCER 寄存器中写入 CC2P=1,以确认极性(并仅检测低电平)。

- 通过在 SMCR 寄存器中写入 SMS=110,将定时器配置为触发模式。通过在 SMCR 寄存器中写入 TS=110,选择 TI2 作为输入源。

当 TI2 上出现上升沿时,计数器在内部时钟上开始计数,并置位 TIF 标志。

TI2 上升沿与计数器实际开始之间的延迟是由于 TI2 输入的重同步电路引起的。

图 47. 触发模式下的控制电路

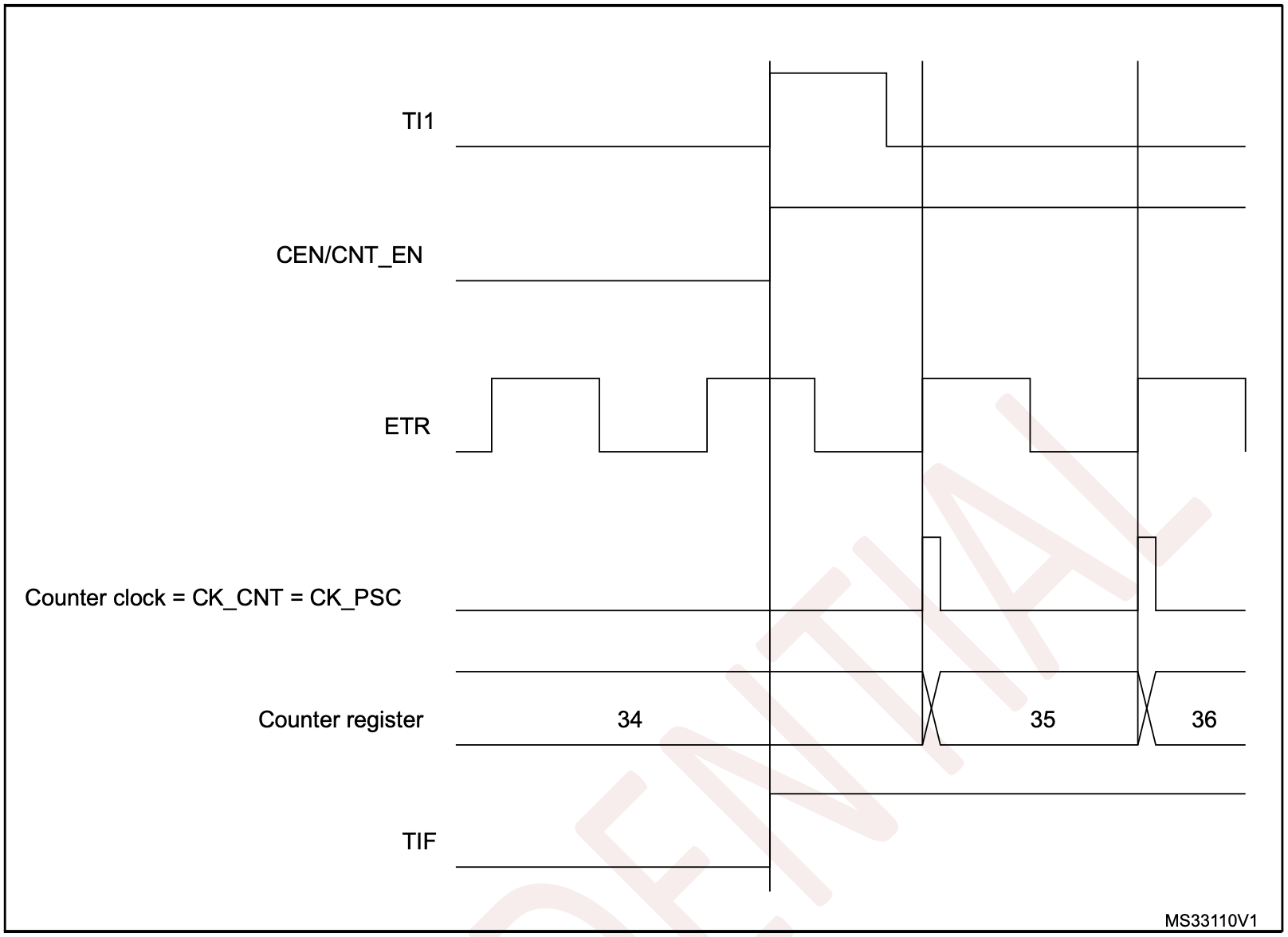

从模式:外部时钟模式 2 + 触发模式

外部时钟模式 2 可与另一种从模式共同使用(除外部时钟模式 1 和编码器模式外)。在这种情况下,ETR 信号被用作外部时钟输入,另一个输入可以选择为触发输入(在复位模式、门控模式或触发模式中)。建议不要通过 SMCR 寄存器的 TS 位选择 ETR 作为 TRGI。

在以下示例中,只要 TI1 出现上升沿,ETR 信号的每个上升沿就会使向上计数器递增一次:

-

通过如下配置 SMCR 寄存器,配置外部触发输入电路:

- ETF = 0000:无滤波器

- ETPS = 00:预分频器禁用

- ETP = 0:检测 ETR 上的上升沿,且 ECE=1 以使能外部时钟模式 2。

-

将通道 0 配置如下,以检测 TI1 上的上升沿:

- IC1F = 0000:无滤波器。

- 捕获预分频器不用于触发,因此无需配置。

- 在 CCMR1 寄存器中设置 CC1S = 01,仅选择输入捕获源。

- 在 CCER 寄存器中设置 CC1P = 0 以确认极性(并仅检测上升沿)。

-

在 SMCR 寄存器中写入 SMS = 110,将定时器配置为触发模式。通过在 SMCR 寄存器中写入 TS = 101,选择 TI1 作为输入源。

TI1 上的上升沿会使计数器使能,并置位 TIF 标志。之后,计数器在 ETR 的上升沿上计数。

ETR 信号的上升沿与计数器实际复位之间的延迟是由于 ETRP 输入上的重同步电路造成的。

图 48. 外部时钟模式 2 + 触发模式下的控制电路

8.3.20 定时器同步¶

TIM 定时器在内部连接在一起,用于定时器同步或级联。

注意:必须在从定时器接收主定时器事件之前使能从定时器的时钟,并且在主定时器触发期间不得动态更改该时钟。

8.3.21 调试模式¶

当微控制器进入调试模式时,计数器要么继续正常工作,要么停止,具体取决于系统控制模块中的 APB_CLK STOP 配置位。

8.4 寄存器¶

外设寄存器可以通过半字(16 位)或字(32 位)访问。

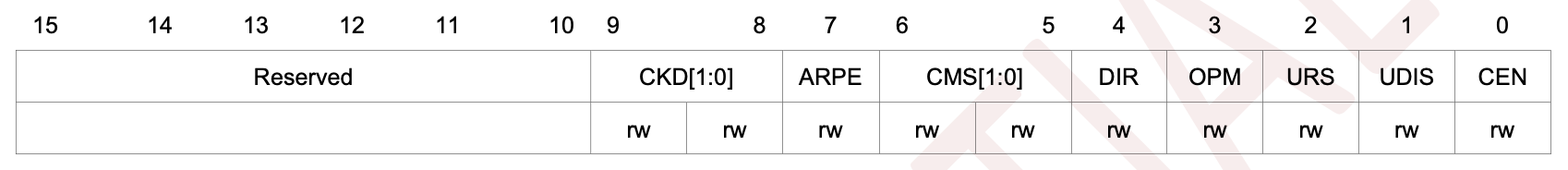

8.4.1 控制寄存器 1(CR1)¶

地址偏移:0x00

复位值:0x0000

- 位 15:10 保留,必须保持为复位值。

-

位 9:8 CKD[1:0]:时钟分频

此位字段表示定时器时钟(CK_INT)频率与死区时间和采样时钟(tDTS)之间的分频比,该时钟用于死区时间发生器和数字滤波器(ETR、TIx)。

00:tDTS = tCK_INT01:tDTS = 2 × tCK_INT10:tDTS = 4 × tCK_INT11:tDTS = 8 × tCK_INT

-

位 7 ARPE:自动重载缓冲使能

0:ARR 寄存器不带缓冲1:ARR 寄存器带缓冲

-

位 6:5 CMS[1:0]:中心对齐模式选择

00:边沿对齐模式。计数器根据方向位(DIR)向上或向下计数01:中心对齐模式 1。计数器交替向上和向下计数。配置为输出模式的通道(CCxS=00)仅在计数器向下计数时设置输出比较中断标志10:中心对齐模式 2。配置为输出模式的通道仅在计数器向上计数时设置输出比较中断标志11:中心对齐模式 3。配置为输出模式的通道在计数器向上和向下计数时均设置输出比较中断标志

注意:当计数器已启用(CEN=1)时,不允许从边沿对齐模式切换为中心对齐模式

-

位 4 DIR:方向

0:计数器作为向上计数器使用1:计数器作为向下计数器使用

注意:仅当定时器配置为中心对齐模式或编码器模式时,此位才可读

-

位 3 OPM:单脉冲模式

0:计数器不会在更新事件时停止1:计数器将在下一个更新事件时停止(清除 CEN 位)

-

位 2 URS:更新请求来源

此位由软件设置和清除,以选择 UEV 事件的来源。

-

0:以下任一事件可在启用的情况下生成更新中断或 DMA 请求:- 计数器上溢/下溢

- 设置 UG 位

- 通过从模式控制器生成的更新事件

-

1:仅计数器上溢/下溢事件可生成更新中断或 DMA 请求(若启用)

-

-

位 1 UDIS:更新禁止

此位由软件设置和清除,以启用/禁用更新事件(UEV)的生成。

-

0:UEV 使能。以下任一事件可生成更新事件:- 计数器上溢/下溢

- 设置 UG 位

- 通过从模式控制器生成的更新事件,此时缓冲寄存器将被预加载值更新

-

1:UEV 禁止。不会生成更新事件,影子寄存器(ARR、PSC、CCRx)保持原值

然而,如果设置了 UG 位,或从从模式控制器收到硬件复位,计数器和预分频器仍将重新初始化

-

-

位 0 CEN:计数器使能

0:计数器禁用1:计数器使能

注意:外部时钟、门控模式和编码器模式仅在软件先设置 CEN 位后才可工作;而触发模式可由硬件自动设置 CEN 位

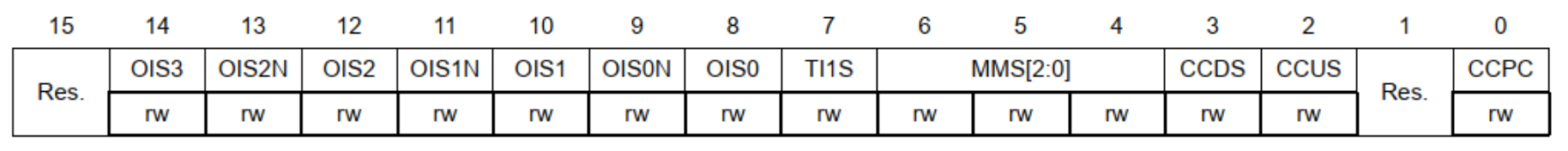

8.4.2 控制寄存器 2(CR2)¶

地址偏移:0x04

复位值:0x0000

- 位 15:保留,必须保持为复位值。

-

位 14 OIS3:输出空闲状态 4(OC3 输出)

参见 OIS1 位。

-

位 13 OIS2N:输出空闲状态 3(OC2N 输出)

参见 OIS1N 位。

-

位 12 OIS2:输出空闲状态 3(OC2 输出)

参见 OIS1 位。

-

位 11 OIS1N:输出空闲状态 2(OC1N 输出)

参见 OIS1N 位。

-

位 10 OIS1:输出空闲状态 2(OC1 输出)

参见 OIS1 位。

-

位 9 OIS0N:输出空闲状态 1(OC0N 输出)

0:当 MOE=0 时,在死区时间之后 OC0N=01:当 MOE=0 时,在死区时间之后 OC0N=1

注意: 若已配置了 LOCK 级别 1、2 或 3(BDTR 寄存器中的 LOCK 位),则该位不可修改。

-

位 8 OIS0:输出空闲状态 1(OC0 输出)

0:当 MOE=0 且(若实现了 OC1N)在死区时间之后 OC0=01:当 MOE=0 且(若实现了 OC1N)在死区时间之后 OC0=1

注意: 若已配置了 LOCK 级别 1、2 或 3(BDTR 寄存器中的 LOCK 位),则该位不可修改。

-

位 7 TI1S:TI1 选择

0:CH1 引脚连接到 TI1 输入1:CH1、CH2 和 CH3 引脚连接至 TI1 输入(XOR 组合)

-

位 6:4 MMS[2:0]:主模式选择(Master Mode Selection)

用于选择在主模式下发送给从定时器的同步信息(TRGO)的来源,组合如下:

000:复位。使用来自 EGR 寄存器的 UG 位作为触发输出(TRGO)。若复位是由触发输入产生(从模式控制器配置为复位模式),则 TRGO 信号会相对实际复位延迟。001:使能。使用计数器使能信号 CNT_EN 作为 TRGO 输出。适用于同时启动多个定时器,或用于控制从定时器使能的时间窗口。CNT_EN 信号由 CEN 控制位与触发输入(在门控模式下配置)逻辑 OR 产生。当 CNT_EN 被触发输入控制时,TRGO 存在延迟,除非启用了主/从模式(见 SMCR 寄存器中的 MSM 位说明)。010:更新。将更新事件作为 TRGO 输出。例如,主定时器可以作为从定时器的预分频器。011:比较脉冲。当 CC1IF 标志将被设置(即便它已为高电平)时,TRGO 发送一个正脉冲,发生在捕获或比较匹配事件发生时。100:比较 - 使用 OC0REF 信号作为 TRGO 输出101:比较 - 使用 OC1REF 信号作为 TRGO 输出110:比较 - 使用 OC2REF 信号作为 TRGO 输出111:比较 - 使用 OC3REF 信号作为 TRGO 输出

注意:从定时器和 ADC 的时钟必须在接收主定时器事件前开启,并且在接收触发信号期间不能动态改变。

-

位 3 CCDS:捕获/比较 DMA 选择

0:当 CCx 事件发生时发送 CCx DMA 请求1:当更新事件发生时发送 CCx DMA 请求

-

位 2 CCUS:捕获/比较控制更新选择

0:当捕获/比较控制位已预装(CCPC=1)时,仅在设置 COMG 位时才更新1:当捕获/比较控制位已预装(CCPC=1)时,设置 COMG 位或 TRGI 上升沿均可触发更新

注意: 此位仅影响具有互补输出的通道。

-

位 1:保留,必须保持为复位值。

-

位 0 CCPC:捕获/比较预加载控制

0:CCxE、CCxNE 和 OCxM 位不进行预加载1:CCxE、CCxNE 和 OCxM 位在写入后进行预加载,只有在发生换相事件(COM)时才会更新(通过设置 COMG 位或 TRGI 上升沿,具体取决于 CCUS 位)

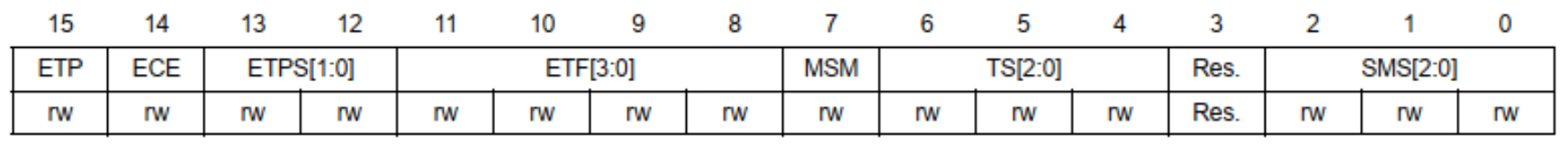

8.4.3 从模式控制寄存器(SMCR)¶

地址偏移:0x08

复位值:0x0000

-

位 15 ETP:外部触发极性

此位用于选择是否对外部触发输入(ETR)信号进行反相:

0:ETR 非反相,处于高电平或上升沿时为有效触发1:ETR 反相,处于低电平或下降沿时为有效触发

-

位 14 ECE:外部时钟使能

启用外部时钟模式 2。

0:禁用外部时钟模式 21:启用外部时钟模式 2,计数器由 ETRF 信号的任意有效边沿驱动计数

注意:

1. 设置 ECE 位的效果等同于选择外部时钟模式 1,并将 TRGI 连接到 ETRF(即SMS=111且TS=111)

2. 外部时钟模式 2 可以与以下从模式同时使用:复位模式、门控模式、触发模式。但此时 TRGI 不能连接到 ETRF(即TS不能为111)

3. 若同时启用外部时钟模式 1 与模式 2,则实际使用的外部时钟输入为 ETRF -

位 13:12 ETPS[1:0]:外部触发预分频器

外部触发信号 ETRP 的频率必须不高于主时钟的 1/4。启用预分频器可以降低 ETRP 的频率,用于快速外部时钟输入场景。

00:不分频01:ETRP 频率除以 210:ETRP 频率除以 411:ETRP 频率除以 8

-

位 11:8 ETF[3:0]:外部触发滤波器

定义对 ETRP 信号采样的频率以及所应用的数字滤波器长度。数字滤波器基于事件计数器,只有 N 个连续事件才能使输出发生变化。

0000:无滤波,采样频率为 fDTS0001:fSAMPLING = fCK_INT,N = 20010:fSAMPLING = fCK_INT,N = 40011:fSAMPLING = fCK_INT,N = 80100:fSAMPLING = fDTS/2,N = 60101:fSAMPLING = fDTS/2,N = 80110:fSAMPLING = fDTS/4,N = 60111:fSAMPLING = fDTS/4,N = 81000:fSAMPLING = fDTS/8,N = 61001:fSAMPLING = fDTS/8,N = 81010:fSAMPLING = fDTS/16,N = 51011:fSAMPLING = fDTS/16,N = 61100:fSAMPLING = fDTS/16,N = 81101:fSAMPLING = fDTS/32,N = 51110:fSAMPLING = fDTS/32,N = 61111:fSAMPLING = fDTS/32,N = 8

-

位 7 MSM:主/从模式

0:无动作1:触发输入(TRGI)上的事件作用会延迟,以实现当前定时器与其从属定时器之间的同步(通过 TRGO)。适用于多个定时器对同一个外部事件进行同步的情况。

-

位 6:4 TS[2:0]:触发源选择

选择用于同步计数器的触发输入源:

000:内部触发 0(ITR0)001:内部触发 1(ITR1)010:内部触发 2(ITR2)011:内部触发 3(ITR3)100:TI1 边沿检测器(TI1F_ED)101:过滤后的定时器输入 1(TI1FP1)110:过滤后的定时器输入 2(TI2FP2)111:外部触发输入(ETRF)

注意: 只有在未使用触发功能时(例如

SMS=000)才能更改这些位,以避免错误的边沿检测。 -

位 3:保留,必须保持为复位值。

-

位 2:0 SMS[2:0]:从模式选择

当选择外部信号时,触发信号(TRGI)的有效边沿由外部输入的极性决定(详见输入控制寄存器和控制寄存器说明):

000:从模式禁用。若 CEN=1,则预分频器由内部时钟直接驱动。001:编码器模式 1 - 计数器在 TI2FP1 的边沿上加/减计数,依据 TI1FP2 的电平。010:编码器模式 2 - 计数器在 TI1FP2 的边沿上加/减计数,依据 TI2FP1 的电平。011:编码器模式 3 - 计数器在 TI1FP1 和 TI2FP2 的边沿上均加/减计数,依据另一个输入的电平。100:复位模式 - 所选触发输入(TRGI)上的上升沿重置计数器并更新寄存器。101:门控模式 - 当触发输入(TRGI)为高电平时启用计数器时钟;当 TRGI 为低时停止计数器(不重置)。110:触发模式 - 计数器在 TRGI 的上升沿开始运行(但不重置)。仅控制启动。111:外部时钟模式 1 - 所选触发输入(TRGI)的上升沿驱动计数器。

注意: 若选择 TI1F_ED(

TS=100)作为触发输入,不应使用门控模式,因为 TI1F_ED 为每次边沿生成一个脉冲,而门控模式依据的是触发信号的电平。说明: 从定时器的时钟在接收来自主定时器的事件前必须已启用,且在接收触发信号期间不得动态更改。

表格:内部触发连接(TS 配置值对照)

| 从定时器 | ITR0 (TS=000) | ITR1 (TS=001) | ITR2 (TS=010) | ITR3 (TS=011) |

|---|---|---|---|---|

| GPTIMER0 | GPTIMER1_TRGO | GPTIMER2_TRGO | GPTIMER3_TRGO | GPTIMER4_TRGO |

| GPTIMER1 | GPTIMER2_TRGO | GPTIMER3_TRGO | GPTIMER4_TRGO | GPTIMER0_TRGO |

| GPTIMER2 | GPTIMER3_TRGO | GPTIMER4_TRGO | GPTIMER0_TRGO | GPTIMER1_TRGO |

| GPTIMER3 | GPTIMER4_TRGO | GPTIMER0_TRGO | GPTIMER1_TRGO | GPTIMER2_TRGO |

| GPTIMER4 | GPTIMER0_TRGO | GPTIMER1_TRGO | GPTIMER2_TRGO | GPTIMER3_TRGO |

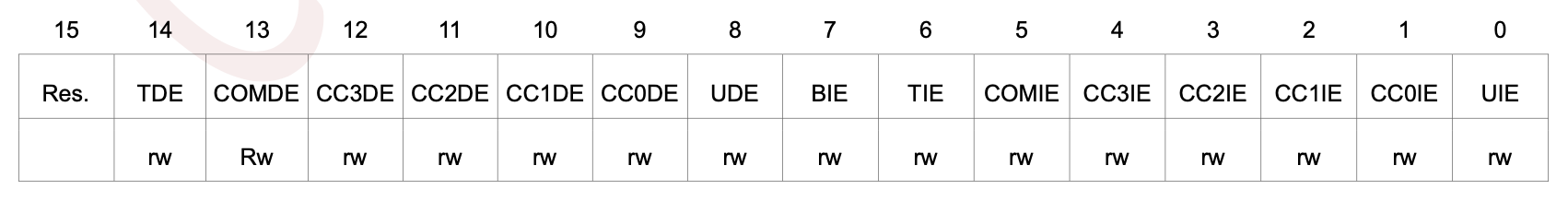

8.4.4 DMA/中断使能寄存器(DIER)¶

地址偏移:0x0C

重置值:0x0000

位定义:

- 位 15 保留,必须保持为重置值。

-

位 14 TDE:触发 DMA 请求使能

- 0: 触发 DMA 请求禁用

- 1: 触发 DMA 请求使能

-

位 13 COMDE:COM DMA 请求使能

- 0: COM DMA 请求禁用

- 1: COM DMA 请求使能

-

位 12 CC3DE:捕获/比较 3 DMA 请求使能

- 0: CC3 DMA 请求禁用

- 1: CC3 DMA 请求使能

-

位 11 CC2DE:捕获/比较 2 DMA 请求使能

- 0: CC2 DMA 请求禁用

- 1: CC2 DMA 请求使能

-

位 10 CC1DE:捕获/比较 1 DMA 请求使能

- 0: CC1 DMA 请求禁用

- 1: CC1 DMA 请求使能

-

位 9 CC0DE:捕获/比较 0 DMA 请求使能

- 0: CC0 DMA 请求禁用

- 1: CC0 DMA 请求使能

-

位 8 UDE:更新 DMA 请求使能

- 0: 更新 DMA 请求禁用

- 1: 更新 DMA 请求使能

-

位 7 BIE:断路器中断使能

- 0: 断路器中断禁用

- 1: 断路器中断使能

-

位 6 TIE:触发中断使能

- 0: 触发中断禁用

- 1: 触发中断使能

-

位 5 COMIE:COM 中断使能

- 0: COM 中断禁用

- 1: COM 中断使能

-

位 4 CC4IE:捕获/比较 4 中断使能

- 0: CC4 中断禁用

- 1: CC4 中断使能

-

位 3 CC3IE:捕获/比较 3 中断使能

- 0: CC3 中断禁用

- 1: CC3 中断使能

-

位 2 CC2IE:捕获/比较 2 中断使能

- 0: CC2 中断禁用

- 1: CC2 中断使能

-

位 1 CC1IE:捕获/比较 1 中断使能

- 0: CC1 中断禁用

- 1: CC1 中断使能

-

位 0 UIE:更新中断使能

- 0: 更新中断禁用

- 1: 更新中断使能

8.4.5 状态寄存器(SR)¶

地址偏移:0x10

重置值:0x0000

位定义:

- 位 15:13 保留,必须保持为重置值。

-

位 12 CC3OF:捕获/比较 3 溢出标志

参见 CC0OF 描述。

-

位 11 CC2OF:捕获/比较 2 溢出标志

参见 CC0OF 描述。

-

位 10 CC1OF:捕获/比较 1 溢出标志

参见 CC0OF 描述。

-

位 9 CC0OF:捕获/比较 0 溢出标志

- 此标志仅在相应通道配置为输入捕获模式时由硬件设置。通过软件将其清除,写入 ‘0’。

- 0: 没有检测到溢出。

- 1: 当 CC0IF 标志已设置时,计数器值已被捕获到 CCR0 寄存器中。

-

位 8 保留,必须保持为重置值。

-

位 7 BIF:断路器中断标志

- 此标志在断路器输入激活时由硬件设置。如果断路器输入未激活,则可以通过软件清除此标志。

- 0: 没有断路器事件发生。

- 1: 检测到断路器输入的有效电平。

-

位 6 TIF:触发中断标志

- 此标志在触发事件发生时由硬件设置(当 TRGI 输入上的上升沿被检测到时,且从模式控制器已启用,在所有模式中,除门控模式外,门控模式中则是两边沿)。可以通过软件清除此标志。

- 0: 没有触发事件发生。

- 1: 触发中断待处理。

-

位 5 COMIF:COM 中断标志

- 此标志在 COM 事件发生时由硬件设置(当捕获/比较控制位 - CCxE, CCxNE, OCxM - 被更新时)。可以通过软件清除此标志。

- 0: 没有 COM 事件发生。

- 1: COM 中断待处理。

-

位 4 CC3IF:捕获/比较 3 中断标志

参见 CC0IF 描述。

-

位 3 CC2IF:捕获/比较 2 中断标志

参见 CC0IF 描述。

-

位 2 CC1IF:捕获/比较 1 中断标志

参见 CC0IF 描述。

-

位 1 CC0IF:捕获/比较 0 中断标志

-

如果通道 CC0 配置为输出:

- 当计数器匹配比较值时,此标志由硬件设置,但在中心对齐模式下有一些例外(参见 CR0 寄存器中的 CMS 位描述)。可以通过软件清除此标志。

- 0: 没有匹配。

- 1: 计数器 CNT 的内容与 CCR0 寄存器的内容匹配。当 CCR0 的内容大于 ARR 的内容时,CC0IF 位在计数器溢出(在向上计数和向上/向下计数模式中)或下溢(在向下计数模式中)时变为高电平。

-

如果通道 CC0 配置为输入:

- 此位由硬件在捕获时设置。可以通过软件或通过读取 CCR0 寄存器来清除此位。

- 0: 没有输入捕获发生。

- 1: 计数器值已被捕获到 CCR0 寄存器(在 IC0 上检测到一个边缘,且该边缘与所选极性匹配)。

-

-

位 0 UIF:更新中断标志

- 此标志在更新事件发生时由硬件设置。可以通过软件清除此标志。

- 0: 没有更新发生。

-

1: 更新中断待处理。当寄存器被更新时,此位由硬件设置:

- 当溢出或下溢与重复计数器值相关时(如果重复计数器 = 0 时进行更新),并且 CR1 寄存器中的 UDIS=0。

- 当通过软件使用 EGR 寄存器中的 UG 位重新初始化 CNT 时,如果 CR0 寄存器中的 URS=0 和 UDIS=0。

- 当通过触发事件重新初始化 CNT 时(参见:从模式控制寄存器 SMCR),如果 CR1 寄存器中的 URS=0 和 UDIS=0。

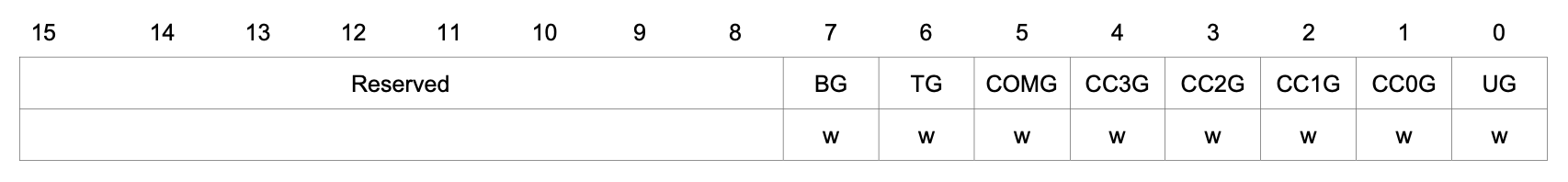

8.4.6 事件生成寄存器 (EGR)¶

地址偏移:0x14

重置值:0x0000

- 位 15:8 保留,必须保持在重置值。

-

位 7 BG:断点生成

- 此位由软件设置以生成一个事件,硬件会自动清除此位。

- 0: 无动作

- 1: 生成断点事件。MOE 位被清除,BIF 标志被设置。如果启用,可能会发生相关中断或 DMA 传输。

-

位 6 TG:触发生成

- 此位由软件设置以生成一个事件,硬件会自动清除此位。

- 0: 无动作

- 1: 在 SR 寄存器中设置 TIF 标志。如果启用,可能会发生相关中断或 DMA 传输。

-

位 5 COMG:捕获/比较控制更新生成

- 此位由软件设置,硬件会自动清除此位。

- 0: 无动作

- 1: 当 CCPC 位被设置时,允许更新 CCxE、CCxNE 和 OCxM 位。

- 注意:此位仅作用于具有互补输出的通道。

-

位 3 CC3G:捕获/比较 3 生成,参考 CC1G 描述。

- 位 2 CC2G:捕获/比较 2 生成,参考 CC1G 描述。

- 位 1 CC1G:捕获/比较 1 生成,参考 CC1G 描述。

-

位 0 CC0G:捕获/比较 0 生成

- 此位由软件设置以生成一个事件,硬件会自动清除此位。

- 0: 无动作

-

1: 在通道 0 上生成捕获/比较事件:

- 如果 CC0 通道被配置为输出:设置 CC1IF 标志,如果启用,发送相应的中断或 DMA 请求。

- 如果 CC0 通道被配置为输入:当前计数器的值被捕获到 CCR0 寄存器中。设置 CC0IF 标志,如果启用,发送相应的中断或 DMA 请求。如果 CC0IF 标志已经被置高,则设置 CC0OF 标志。

-

位 0 UG:更新生成

- 此位由软件设置,硬件会自动清除此位。

- 0: 无动作

- 1: 重新初始化计数器并生成寄存器更新。注意,预分频器计数器也会被清除(但预分频比率不受影响)。如果选择中心对齐模式或 DIR=0(向上计数),则计数器会被清除;如果 DIR=1(向下计数),则计数器取自动重载值(ARR)。

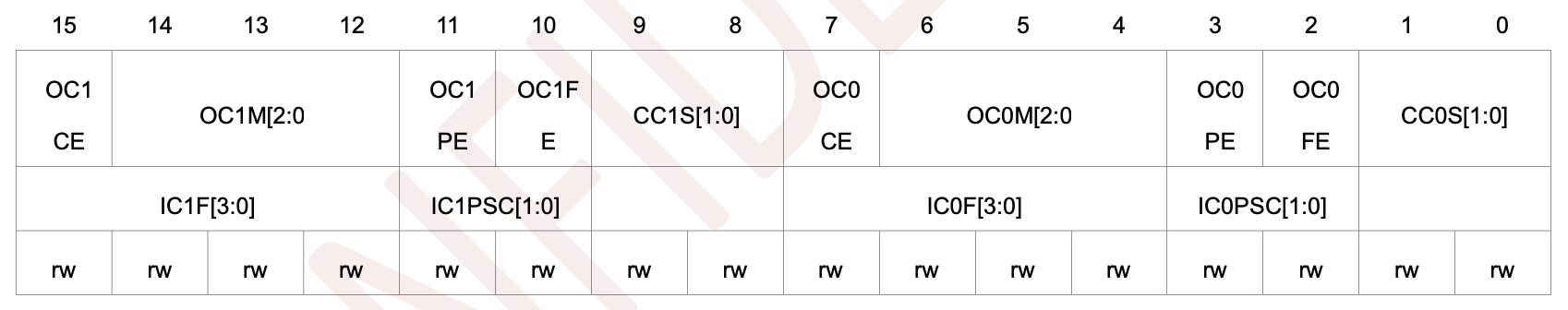

8.4.7 捕获/比较模式寄存器 1 (CCMR1)¶

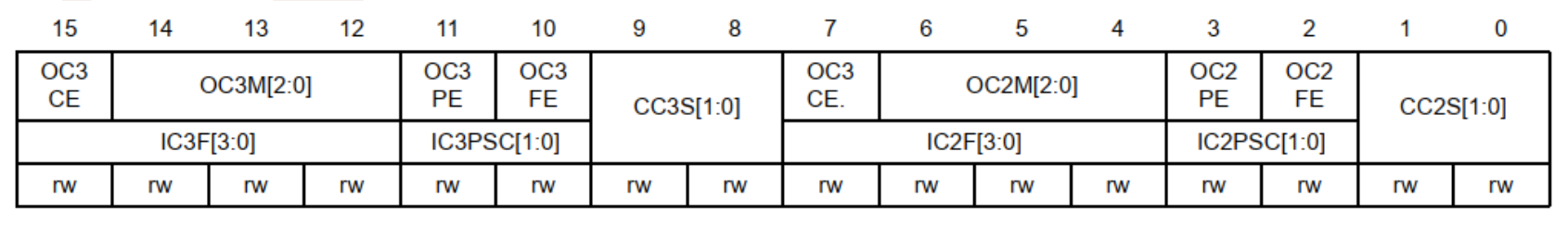

地址偏移: 0x18

复位值: 0x0000

通道可以用于输入(捕获模式)或输出(比较模式)。通道的方向通过配置相应的 CCxS 位来定义。该寄存器的所有其他位在输入和输出模式下具有不同的功能。对于给定的位,OCxx 描述的是通道配置为输出时的功能,ICxx 描述的是通道配置为输入时的功能。因此,用户需要注意,同一位在输入阶段和输出阶段可能具有不同的含义。

输出比较模式¶

- 位 15 OC1CE: 输出比较 2 清除使能

- 位 14:12 OC1M[2:0]: 输出比较 2 模式

- 位 11 OC1PE: 输出比较 2 预加载使能

- 位 10 OC1FE: 输出比较 2 快速使能

-

位 9:8 CC1S[1:0]: 捕获/比较 2 选择

- 该位域定义了通道的方向(输入/输出)以及所使用的输入。

- 00:CC1 通道配置为输出

- 01:CC1 通道配置为输入,IC1 映射到 TI1

- 10:CC1 通道配置为输入,IC1 映射到 TI0

- 11:CC1 通道配置为输入,IC1 映射到 TRC。此模式仅在通过 TS 位(SMCR 寄存器)选择了内部触发输入时有效。

注意: CC1S 位仅在通道关闭时可写(CC1E = ‘0’ 在 CCER 寄存器中)。

-

位 7 OC0CE: 输出比较 1 清除使能

-

OC0CE: 输出比较 1 清除使能

- 0:ETRF 输入不影响 OC0Ref

- 1:当检测到 ETRF 输入的高电平时,OC0Ref 会被清除

-

-

位 6:4 OC0M: 输出比较 1 模式

- 这些位定义了从 OC0 生成的输出参考信号 OC0REF 的行为,OC0 和 OC0N 的激活电平取决于 CC0P 和 CC0NP 位。

- 000:冻结 - 输出比较寄存器 CCR0 和计数器 CNT 之间的比较对输出没有影响。(此模式用于生成时基)

- 001:当计数器 CNT 与捕获/比较寄存器 1(CCR0)匹配时,OC0REF 信号强制为高电平。

- 010:当计数器 CNT 与捕获/比较寄存器 1(CCR0)匹配时,OC1REF 信号强制为低电平。

- 011:切换 - 当 CNT = CCR0 时,OC0REF 切换。

- 100:强制为低电平 - OC0REF 强制为低电平。

- 101:强制为高电平 - OC0REF 强制为高电平。

- 110:PWM 模式 1 - 在递增计数中,当 CNT < CCR0 时,通道 0 激活,否则为不活跃。在递减计数中,当 CNT > CCR0 时,通道 0 不活跃(OC0REF=‘0’),否则为活跃(OC0REF=‘1’)。

- 111:PWM 模式 2 - 在递增计数中,当 CNT < CCR0 时,通道 0 不活跃,否则为活跃。在递减计数中,当 CNT > CCR0 时,通道 0 激活,否则不活跃。

注意: 1. 这些位不能在 LOCK 级别 3 被编程(BDTR 寄存器中的 LOCK 位)且 CC0S = ‘00’(通道配置为输出)时修改。 2. 在 PWM 模式 1 或 2 中,OCREF 电平仅在比较结果发生变化时或当输出比较模式从“冻结”模式切换到“PWM”模式时变化。

-

位 3 OC0PE: 输出比较 1 预加载使能

- 0:禁用 CCR0 上的预加载寄存器。CCR0 可以随时写入,新值立即生效。

- 1:启用 CCR0 上的预加载寄存器。读/写操作访问预加载寄存器。每次更新事件时,CCR0 预加载值将加载到活动寄存器中。

注意: 1. 这些位不能在 LOCK 级别 3 被编程(BDTR 寄存器中的 LOCK 位)且 CC0S = ‘00’(通道配置为输出)时修改。 2. 仅在单脉冲模式下(CR0 寄存器中的 OPM 位设置)可以在不验证预加载寄存器的情况下使用 PWM 模式,否则行为无法保证。

-

位 2 OC0FE: 输出比较 1 快速使能

- 该位用于加速事件在输入触发上的效果,影响 CC 输出。

- 0:即使触发输入为 ON,CC0 也根据计数器和 CCR0 的值正常工作。触发输入边缘发生时,激活 CC0 输出的最小延迟为 5 个时钟周期。

- 1:触发输入上的活动边缘像比较匹配一样作用于 CC0 输出。然后,无论比较结果如何,OC 被设置为比较电平。采样触发输入并激活 CC0 输出的延迟缩短为 3 个时钟周期。OCFE 仅在通道配置为 PWM1 或 PWM2 模式时生效。

-

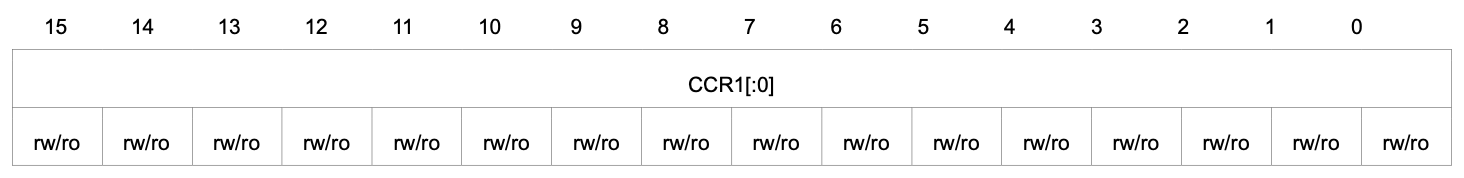

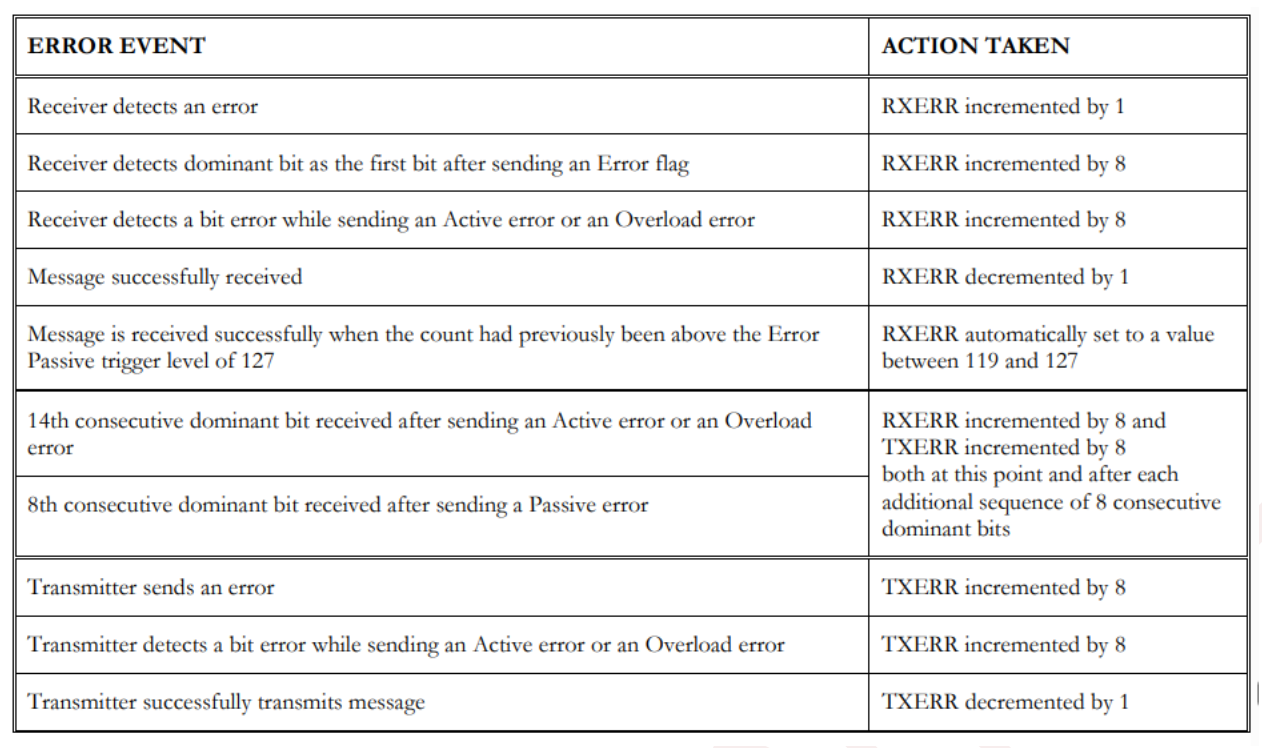

位 1:0 CC0S: 捕获/比较 1 选择